卷積是一種線性運(yùn)算,其本質(zhì)是滑動(dòng)平均思想,廣泛應(yīng)用于圖像濾波。而隨著人工智能及深度學(xué)習(xí)的發(fā)展,卷積也在神經(jīng)網(wǎng)絡(luò)中發(fā)揮重要的作用,如卷積神經(jīng)網(wǎng)絡(luò)。本參考設(shè)計(jì)主要介紹如何基于INTEL 硬浮點(diǎn)的DSP

2018-07-23 09:09:45 7322

7322

FPGA中DSP資源是寶貴的且有限,我們在計(jì)算大位寬的指數(shù)、復(fù)數(shù)乘法、累加、累乘等運(yùn)算時(shí)都會用到DSP資源,如果我們不了解底層的DSP特性,很多設(shè)計(jì)可能都無法進(jìn)行。邏輯綜合往往是不可控的,為了能夠

2020-09-30 11:48:55 26638

26638

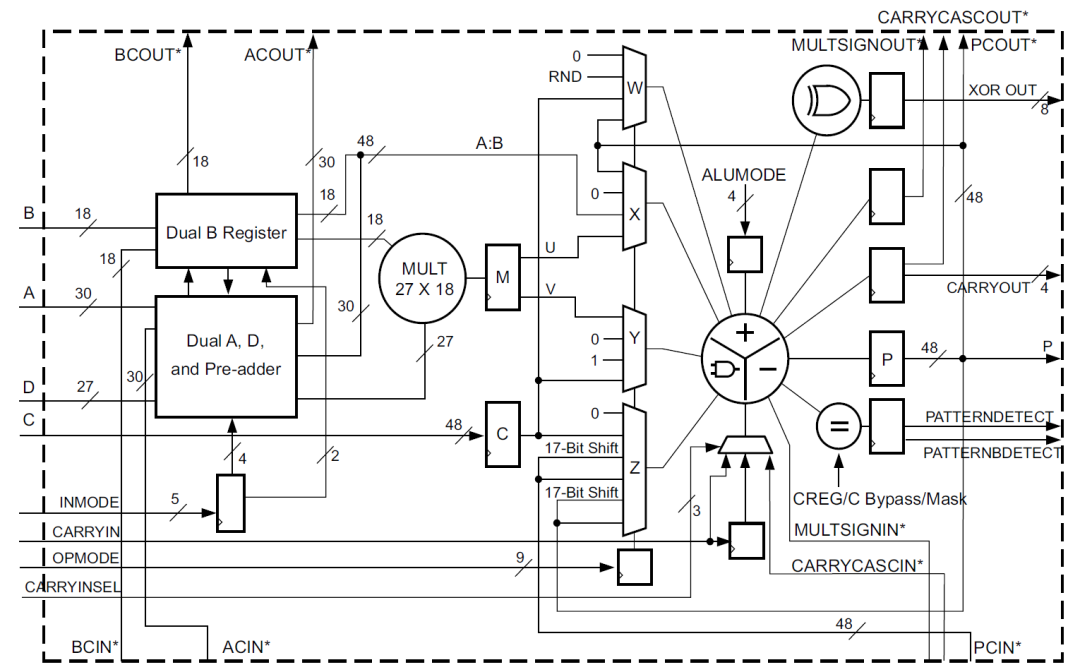

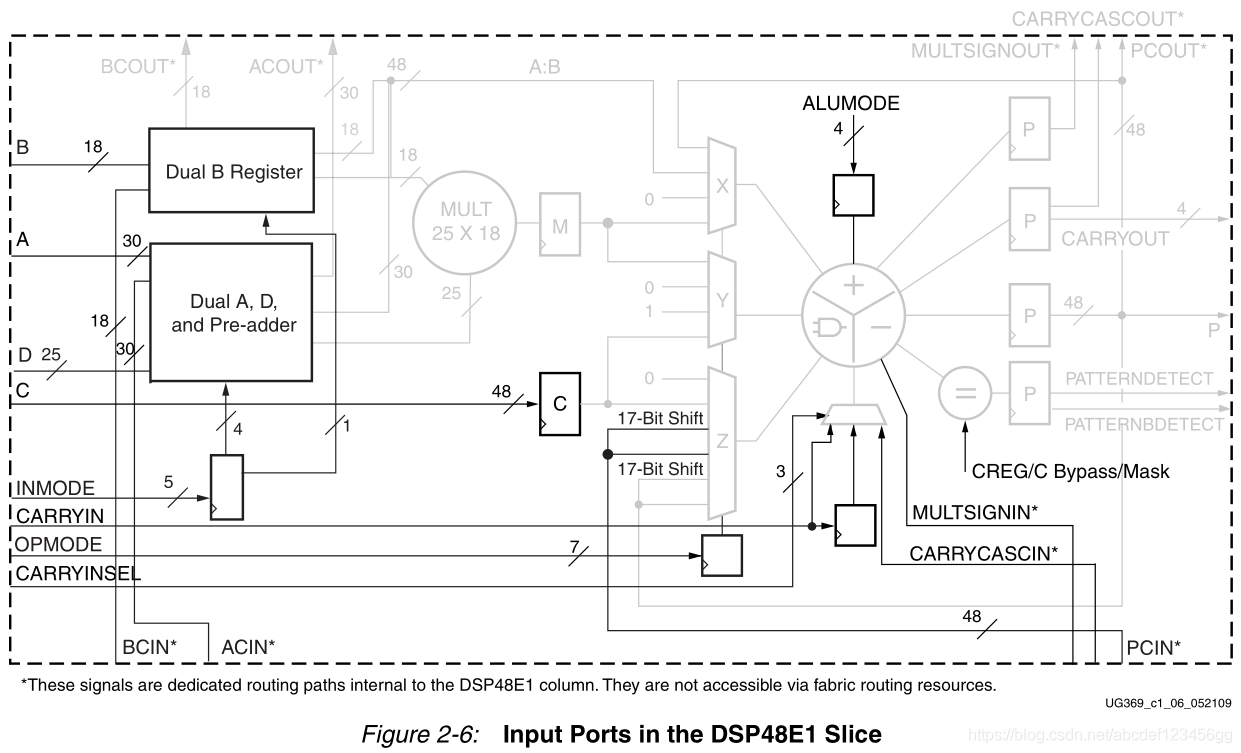

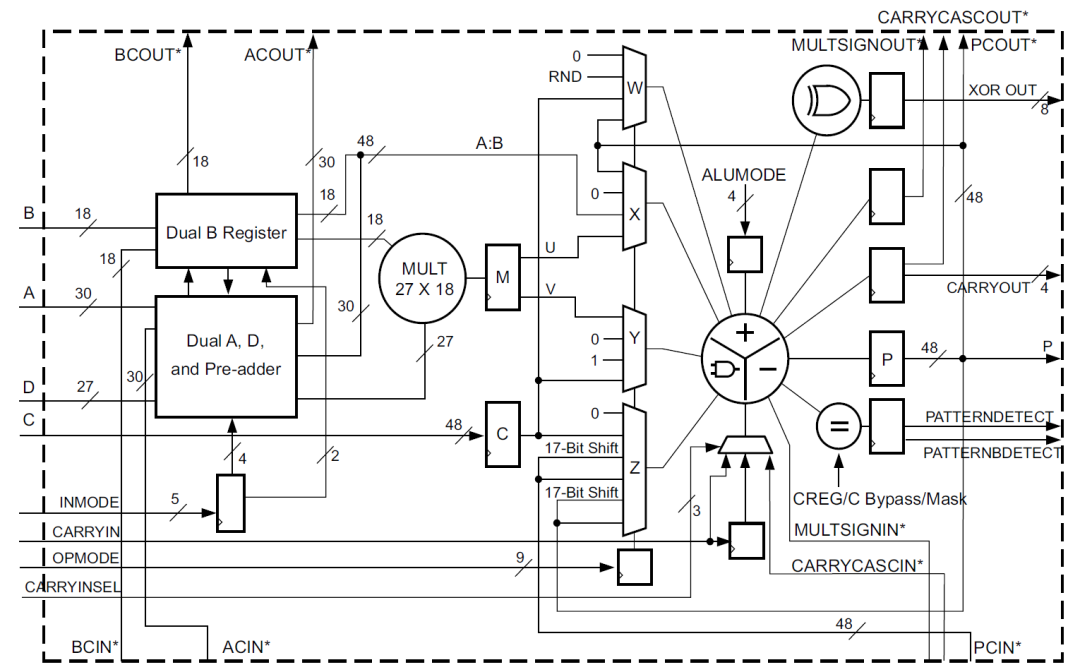

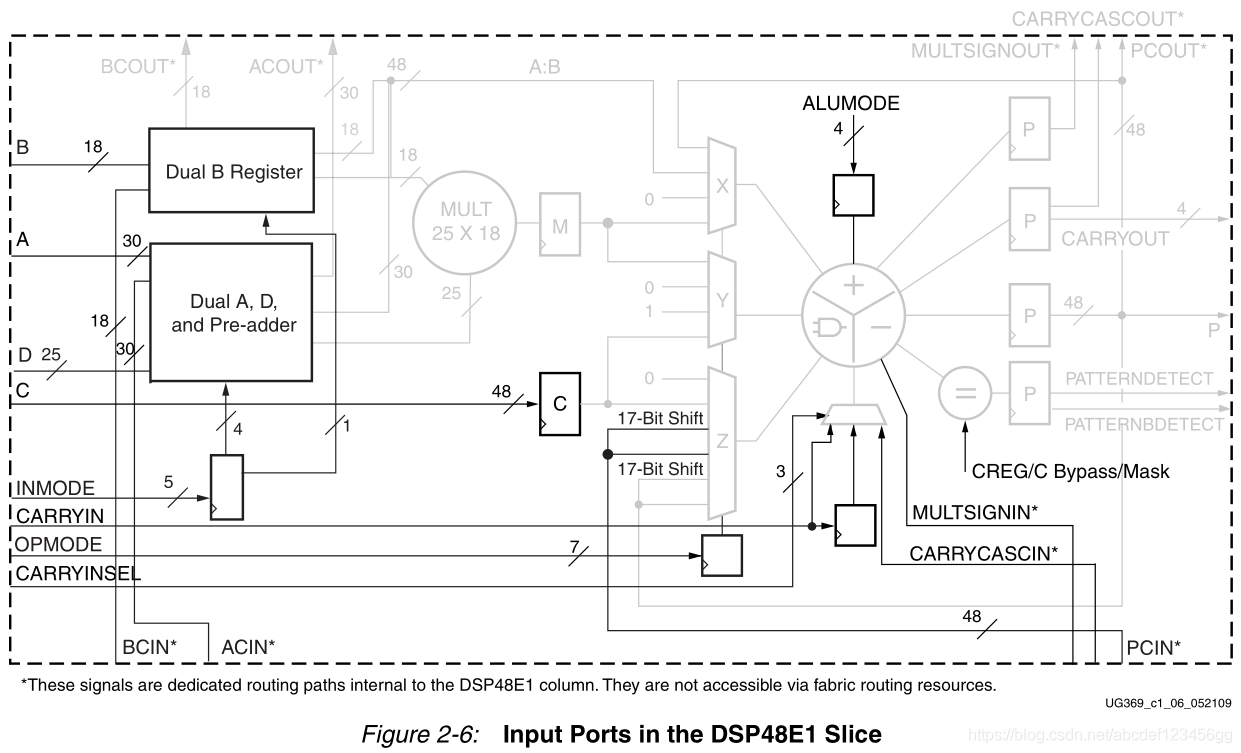

DSP48E2是zynq器件中使用的DSP類型,其主要結(jié)構(gòu)包括一個(gè)27bit前加器,27x18bit的乘法器,一個(gè)48bit的可以執(zhí)行加減法,累加以及邏輯功能的ALU。

2022-08-02 09:16:27 3378

3378

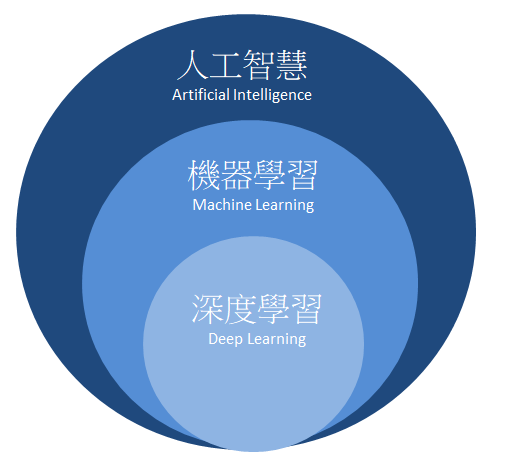

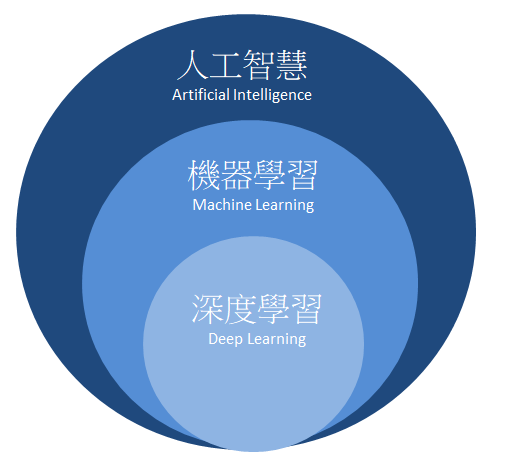

人工智慧隸屬于大範(fàn)疇,包含了機(jī)器學(xué)習(xí)(Machine Learning) 與深度學(xué)習(xí)(Deep Learning)。如下圖所示,我們最興趣的深度學(xué)習(xí)則是規(guī)範(fàn)于機(jī)器學(xué)習(xí)之中的一項(xiàng)分支,而以下段落將簡單介紹機(jī)器學(xué)習(xí)與深度學(xué)習(xí)的差異。

2020-12-18 15:45:31 3870

3870

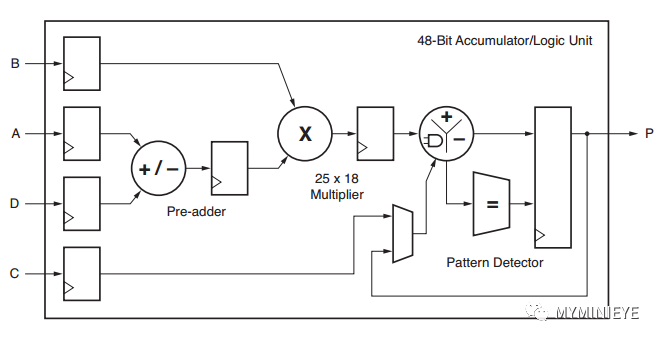

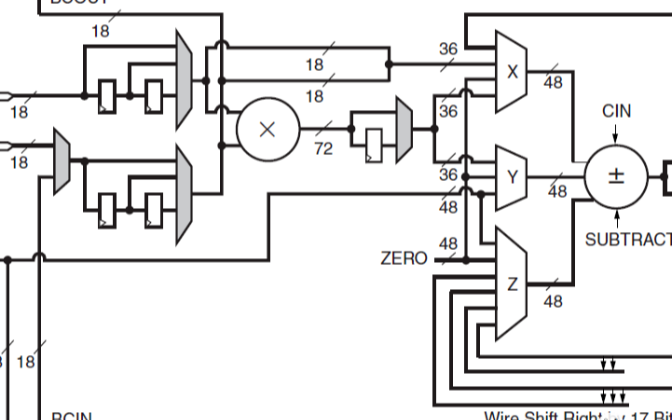

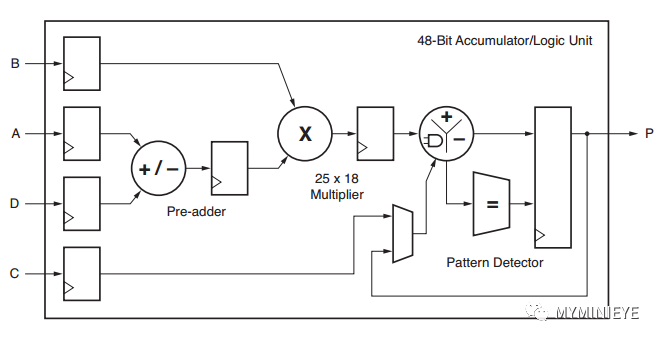

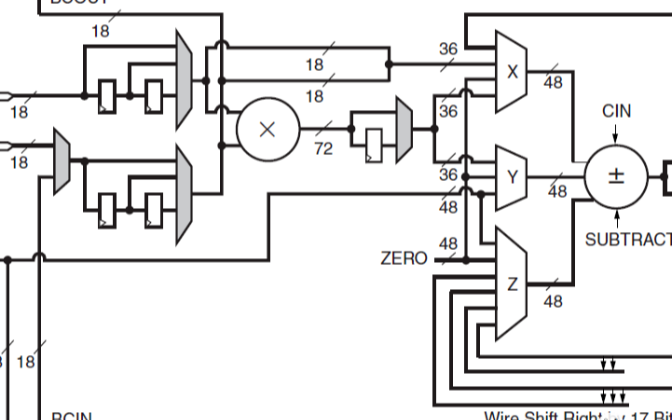

乘法器和一個(gè)三輸入加法器/減法器/累加器。DSP48E1乘法器具有非對稱的輸入,接受18位2的補(bǔ)數(shù)操作數(shù)和25位2的補(bǔ)數(shù)操作數(shù)。乘法器階段以兩個(gè)部分乘積的形式產(chǎn)生一個(gè)43位2的補(bǔ)碼結(jié)果。這些部分積在X

2021-01-08 16:46:10

7系列FPGA DSP48E1片的特點(diǎn)什么

2021-03-05 06:26:41

我正在實(shí)例化DSP切片并進(jìn)行簡單的乘法然后加法((A * B)+ C)。根據(jù)DSP48E1用戶指南,當(dāng)使用所有三個(gè)流水線寄存器時(shí),它給出了最高頻率為600 MHz。但就我而言,它使用流水線寄存器

2020-06-12 06:32:01

嗨,我有一個(gè)如下的指令:(D-A)* B + C.端口A,B,C,D與DSP48E1輸入引腳相對應(yīng)。我試圖將整個(gè)操作打包在DSP單元中。 (順便說一句,我的數(shù)據(jù)寬度是8位)在布局和布線完成后,我

2019-04-01 14:25:40

to use a DSP48E1 slice to delay data up to 48bits wide by three cycles and hence only use 1 DSP48 rather

2019-04-18 06:40:33

DSP48E1屬性

2021-01-27 06:21:23

和RSTB復(fù)位(如圖2-7和圖2-8所示)。 P端口 每個(gè)DSP48E1片都有一個(gè)48位的輸出端口p。這個(gè)輸出可以通過PCOUT路徑內(nèi)部連接(級聯(lián)連接)到相鄰的DSP48E1片。PCOUT連接

2020-12-23 16:54:08

Memory,開啟cache。 如DSP能對SDRAM的不同4個(gè)bank可以同時(shí)訪問,此時(shí)你可以將需要同時(shí)運(yùn)算的數(shù)據(jù)放入不同的bank (8)開啟仿真軟件的編譯優(yōu)化選項(xiàng) 在菜單相應(yīng)的地方勾上

2011-10-19 10:31:23

,51的指令是一條一條的執(zhí)行,DSP的指令可以多條并行處理,從而獲得了更快的計(jì)算速度。2、運(yùn)算能力。很多DSP器件硬件支持浮點(diǎn)數(shù)乘法,同時(shí)有硬件循環(huán)指令。硬件浮點(diǎn)乘法極大的提高了運(yùn)算能力。硬件循環(huán)指令

2012-01-11 09:28:20

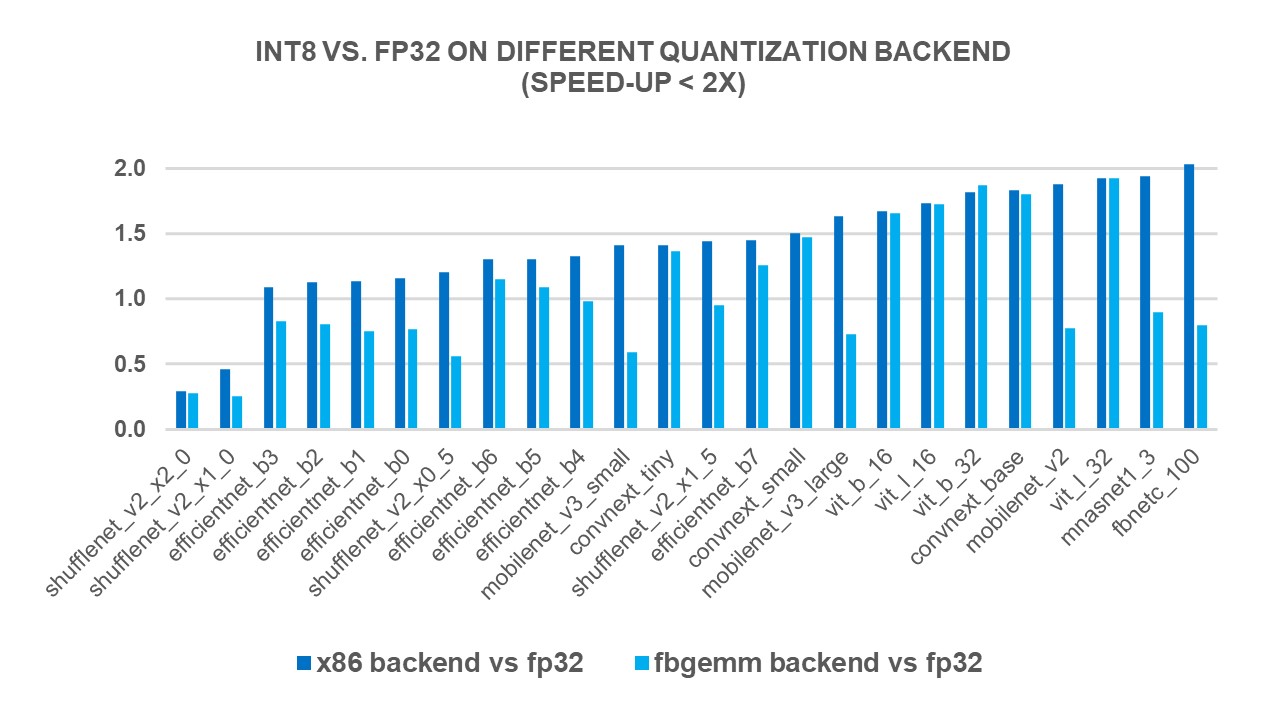

一、int8的輸出和fp32模型輸出差異比較大

解決方案:

檢查前后處理是否有問題,int8網(wǎng)絡(luò)輸入輸出一般需要做scale處理,看看是否遺漏?

通過量化可視化工具分析int8的輸出和fp32

2023-09-19 06:09:33

深度學(xué)習(xí)常用模型有哪些?深度學(xué)習(xí)常用軟件工具及平臺有哪些?深度學(xué)習(xí)存在哪些問題?

2021-10-14 08:20:47

時(shí)間安排大綱具體內(nèi)容實(shí)操案例三天關(guān)鍵點(diǎn)1.強(qiáng)化學(xué)習(xí)的發(fā)展歷程2.馬爾可夫決策過程3.動(dòng)態(tài)規(guī)劃4.無模型預(yù)測學(xué)習(xí)5.無模型控制學(xué)習(xí)6.價(jià)值函數(shù)逼近7.策略梯度方法8.深度強(qiáng)化學(xué)習(xí)-DQN算法系列9.

2022-04-21 14:57:39

CPU優(yōu)化深度學(xué)習(xí)框架和函數(shù)庫機(jī)器學(xué)***器

2021-02-22 06:01:02

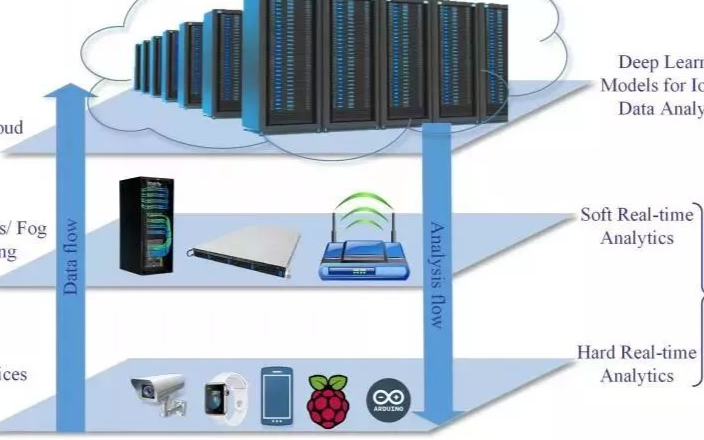

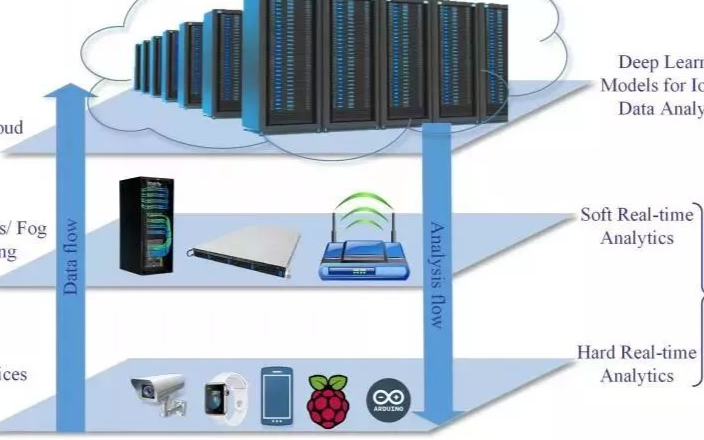

具有深度學(xué)習(xí)模型的嵌入式系統(tǒng)應(yīng)用程序帶來了巨大的好處。深度學(xué)習(xí)嵌入式系統(tǒng)已經(jīng)改變了各個(gè)行業(yè)的企業(yè)和組織。深度學(xué)習(xí)模型可以幫助實(shí)現(xiàn)工業(yè)流程自動(dòng)化,進(jìn)行實(shí)時(shí)分析以做出決策,甚至可以預(yù)測預(yù)警。這些AI

2021-10-27 06:34:15

機(jī)器學(xué)習(xí) (ML) 是云和邊緣基礎(chǔ)設(shè)施中增長最快的部分之一。在 ML 中,深度學(xué)習(xí)推理預(yù)計(jì)會增長得更快。在本博客中,我們比較了三種 Amazon Web Services (AWS) EC2 云實(shí)例

2022-08-31 15:03:46

1. 簡介隨著人工智能的普及,深度學(xué)習(xí)網(wǎng)絡(luò)的不斷涌現(xiàn),為了讓各硬件(CPU, GPU, NPU,…)能夠支持深度學(xué)習(xí)應(yīng)用,各硬件芯片需要軟件庫去支持高性能的深度學(xué)習(xí)張量運(yùn)算。目前,這些高性能計(jì)算庫

2021-12-14 06:18:21

L2cache

2.2 峰值算力

峰值算力:

FP32峰值算力 = 64 * 16 * 2(FP32 MAC) * 2 * 0 55G / 1024 = 2.2 TOPS

INT8峰值算力 = 64

2023-09-19 08:11:10

學(xué)習(xí),也就是現(xiàn)在最流行的深度學(xué)習(xí)領(lǐng)域,關(guān)注論壇的朋友應(yīng)該看到了,開發(fā)板試用活動(dòng)中有【NanoPi K1 Plus試用】的申請,介紹中NanopiK1plus的高大上優(yōu)點(diǎn)之一就是“可運(yùn)行深度學(xué)習(xí)算法的智能

2018-06-04 22:32:12

`Nanopi深度學(xué)習(xí)之路這一系列的日記內(nèi)容如下:1. 根據(jù)深度學(xué)習(xí)任務(wù)配置Nanopi2。2. 在Nanopi2上安裝Keras和TensorFlow。3. 在Nanopi2上部署一個(gè)訓(xùn)練好的深度

2018-06-05 17:29:51

DSP(Digital Signal Processor)和 EVE(Embedded Vision/Vector Engine),用于加速計(jì)算深度學(xué)習(xí)神經(jīng)網(wǎng)絡(luò)。相比于上一代TDA2/TDA3系列

2022-11-03 06:53:11

UltraScale DSP48 Slice架構(gòu)的優(yōu)勢是什么?UltraScale內(nèi)存架構(gòu)的優(yōu)勢是什么?

2021-05-24 06:34:00

the slice, can't I use the DSP48A1 macro itself to test this Xapp706 application?

2019-07-04 15:36:07

,這樣的輸入選擇有助于構(gòu)建多種類型,高流水化的DSP應(yīng)用。

2. DSP48E1使用

(1)DSP原語使用的每個(gè)端口及位寬如下所示:

①表示的數(shù)據(jù)通道,運(yùn)算數(shù)據(jù)的輸入。

②寄存器配置通道,我們可以通過

2023-06-20 14:29:51

model_deploy.py --mlir yolov5l.mlir --quantize INT8 --calibration_table yolov5l_cali_table --chip

2024-01-10 06:40:14

,使其更緊湊和更易debug,并提供了擴(kuò)展的便利性。 課程內(nèi)容基本上是以代碼編程為主,也會有少量的深度學(xué)習(xí)理論內(nèi)容。課程會一步一步從Keras環(huán)境安裝開始講解,并從最基礎(chǔ)的Keras實(shí)現(xiàn)線性回歸

2018-07-17 11:40:31

caffe模型(浮點(diǎn)),得到int8的模型,再通過sdk編程,直接部署到FPGA上,這個(gè)過程本質(zhì)上應(yīng)該還是使用了SDSoC的相關(guān)工具。 大佬們開發(fā)了DPU這個(gè)深度學(xué)習(xí)的IP,在不遠(yuǎn)的將來要放置到

2019-03-21 15:09:29

申請理由:1)由于剛接觸到DSP不久,希望通過DSP的開發(fā)板能夠快速入門,前期實(shí)現(xiàn)一些基本的功能;2)在學(xué)習(xí)到DSP的一些基本知識后,將逐漸運(yùn)用DSP的實(shí)際項(xiàng)目中,先試著嘗試解決一些振動(dòng)數(shù)據(jù)分析

2015-09-10 11:20:00

計(jì)算公司賽靈思(NASDAQ:XLNX)宣布,收購北京人工智能(AI)芯片初創(chuàng)公司深鑒科技。深鑒科技擁有業(yè)界較為領(lǐng)先的機(jī)器學(xué)習(xí)能力,專注于神經(jīng)網(wǎng)絡(luò)剪枝、深度壓縮技術(shù)及系統(tǒng)級優(yōu)化。深鑒科技原本是一家芯片

2020-12-10 15:23:40

開始的,相比傳統(tǒng)的CPU和GPU,在深度學(xué)習(xí)運(yùn)算能力上有比較大幅度的提升。接下來在RV1109和RV1126上使用了第二代NPU,提升了NPU的利用率。第三代NPU應(yīng)用在RK3566和RK3568上

2022-06-23 15:05:22

深度學(xué)習(xí)是什么意思

2020-11-11 06:58:03

,即使使用具有一定低位寬的數(shù)據(jù),深度學(xué)習(xí)推理也不會降低最終精度。目前據(jù)說8位左右可以提供穩(wěn)定的準(zhǔn)確率,但最新的研究表明,已經(jīng)出現(xiàn)了即使降低到4位或2位也能獲得很好準(zhǔn)確率的模型和學(xué)習(xí)方法,越來越多的正在

2023-02-17 16:56:59

本文闡述了Spartan-3 FPGA針對DSP而優(yōu)化的特性,并通過實(shí)現(xiàn)示例分析了它們在性能和成本上的優(yōu)勢。

2019-10-18 07:11:35

矩陣乘,則可使用 B 與 A 矩陣乘之后進(jìn)行轉(zhuǎn)置進(jìn)行替換,可節(jié)約一次轉(zhuǎn)置運(yùn)算。b. 算子融合是常見的深度學(xué)習(xí)的優(yōu)化手段。算子融合雖然不能減少計(jì)算量,但是可以減少訪存量,提高計(jì)算訪存比,從而提升性能

2023-02-09 16:35:34

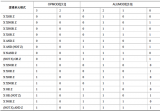

1323%DSP48E1的數(shù)量168641%設(shè)備利用率摘要(估計(jì)值)[ - ]邏輯利用用過的可得到采用切片寄存器的數(shù)量38695068736056%切片LUT的數(shù)量15269234368044%完全

2019-03-25 14:27:40

嗨,我想使用DSP45E1模塊實(shí)現(xiàn)Multply-Add操作,其中一個(gè)要求是我需要DSP模塊上的3級流水線。查看UG479 7系列DSP48E1 Slice用戶指南(UG479) - Xilinx

2020-07-21 13:52:24

DSP48E1片的數(shù)學(xué)部分由一個(gè)25位的預(yù)加器、2個(gè)25位、18位的補(bǔ)法器和3個(gè)48位的數(shù)據(jù)路徑多路復(fù)用器(具有輸出X、Y和Z)組成,然后是一個(gè)3輸入加法器/減法器或2輸入邏輯單元(參見圖2

2021-01-08 16:36:32

簡化DSP48E1片操作

2021-01-27 07:13:57

切片是整個(gè)切片數(shù)量的一部分還是它們在FPGA上共享資源?2)如果我們沒有進(jìn)行任何DSP操作,那么DSP48E Slice是否可以用于實(shí)現(xiàn)某些常規(guī)邏輯,或者這些DSP Slice是否專門用于實(shí)現(xiàn)DSP

2019-04-04 06:36:56

DSP48E1磁貼(由2個(gè)切片和互連組成)與5個(gè)CLB具有相同的高度1 DSP48E1瓷磚與一個(gè)BRAM36K具有相同的高度1 DPS48E1 Slice水平對齊BRAM18K我讀到了xilinx asmbl架構(gòu)

2020-07-25 11:04:42

求大神指教:在labview的公式節(jié)點(diǎn)中如何定義一個(gè)靜態(tài)變量(例如:static int8 i=0;這樣可以嗎?)

2016-04-13 21:37:29

的體系結(jié)構(gòu),熟練使用相關(guān)開發(fā)調(diào)試工具,擅長軟件性能分析和優(yōu)化,能在緊約束條件下充分利用硬件資源,深度優(yōu)化提升軟件效率; 8、勇于承擔(dān)責(zé)任,良好的溝通能力和團(tuán)隊(duì)合作精神; 9、較好的英文閱讀能力。 有興趣的朋友,請聯(lián)系我,企鵝號碼:1537906585

2016-05-04 17:40:52

嗨,我正在使用兩個(gè)使用級聯(lián)鏈路連接的DSP48切片來執(zhí)行所需的操作。我想嘗試多泵操作以有效地使用DSP48切片。請?zhí)峁?b class="flag-6" style="color: red">DSP48 slice中的Multipumping示例。提前致謝

2019-08-06 10:42:26

本帖最后由 一只耳朵怪 于 2018-6-13 16:29 編輯

大家好,使用28335也有1年多了,這個(gè)數(shù)制問題一直困擾我,就是如何自己定義8位的int型整數(shù)?在網(wǎng)上搜到的 typedef CPU_INT08U uint8; //[0 255],這個(gè)能用么?謝謝大家~

2018-06-13 04:13:04

本帖最后由 一只耳朵怪 于 2018-6-25 14:58 編輯

不能是INT16字型的?INT8精度不夠呀~

2018-06-25 01:12:25

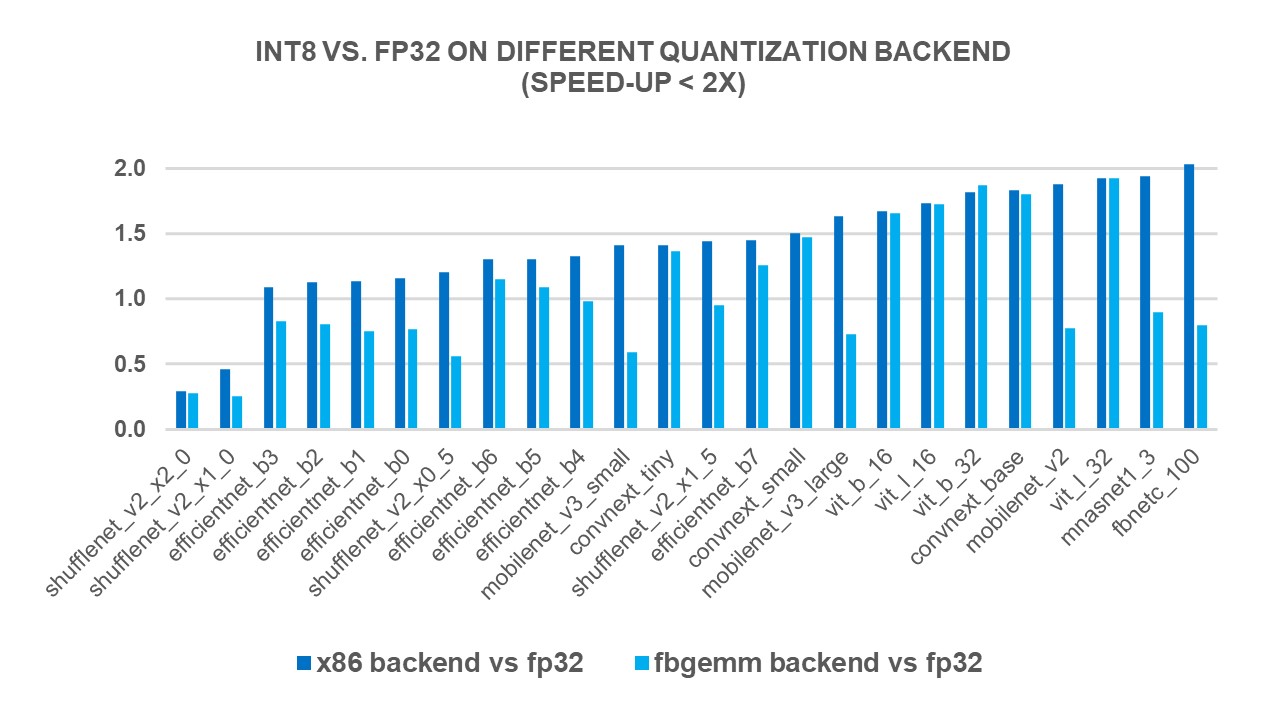

與采用舊 CPU 的推理相比,在新 CPU 上推斷的 INT8 模型的推理速度更快。

2023-08-15 08:28:42

High DSP Performance Platform– The DSP48E Slice– Essential DSP Building Blocks• Imaging Algorithms

2009-04-09 22:05:31 12

12 本文簡要介紹了MPEG4-SP在DSP TM1300上的實(shí)現(xiàn)和優(yōu)化過程。分析了其性能優(yōu)化原理,給出了性能優(yōu)化中使用到的幾個(gè)技巧,最終取得了滿意的優(yōu)化效果。

2009-05-09 14:14:45 13

13 CDMA網(wǎng)絡(luò)深度覆蓋的天線應(yīng)用與RSSI指標(biāo)優(yōu)化分析,很好的網(wǎng)絡(luò)資料,快來學(xué)習(xí)吧。

2016-04-19 11:30:48 23

23 、乘加(MACC, ),乘加,三輸入加法等等。該架構(gòu)還支持串聯(lián)多個(gè)DSP48E1 slice,避免使用fpga邏輯功能的繁瑣。 System generator DSP48E1 模塊參數(shù) 雙擊dsp48e1模塊

2017-02-08 01:07:12 595

595

UltraScale DSP48E2 Slice 完美結(jié)合在一起。Prodigy KU 邏輯模塊理想適用于計(jì)算密集型應(yīng)用;根據(jù) S2C 的介紹,該模塊提供的 DSP 資源比市場上任何原型板都要多。除了數(shù)千

2017-02-08 12:19:14 884

884 為了適應(yīng)越來越復(fù)雜的DSP運(yùn)算,Spartan-6在Spartan 3A DSP模塊DSP48A 基礎(chǔ)上,不斷進(jìn)行功能擴(kuò)展,推出了功能更強(qiáng)大的DSP48A1 SLICE。

2017-02-11 08:53:13 992

992

為了適應(yīng)越來越復(fù)雜的DSP運(yùn)算,Virtex-6中嵌入了功能更強(qiáng)大的DSP48E1 SLICE,簡化的DSP48E1模塊如圖5-16所示。

2017-02-11 09:17:13 1391

1391

賽靈思 INT8 優(yōu)化為使用深度學(xué)習(xí)推斷和傳統(tǒng)計(jì)算機(jī)視覺功能的嵌入式視覺應(yīng)用提供最優(yōu)異的性能和能效最出色的計(jì)算方法。與其他 FPGA/DSP 架構(gòu)相比,賽靈思的集成 DSP 架構(gòu)在 INT8 深度學(xué)習(xí)運(yùn)算上能實(shí)現(xiàn) 1.75 倍的性能優(yōu)勢。

2017-09-22 17:27:11 5280

5280 類庫,用數(shù)組向量來定義和計(jì)算數(shù)學(xué)表達(dá)式。它使得在Python環(huán)境下編寫深度學(xué)習(xí)算法變得簡單。在它基礎(chǔ)之上還搭建了許多類庫。Keras是一個(gè)簡潔、高度模塊化的神經(jīng)網(wǎng)絡(luò)庫,它的設(shè)計(jì)參考了Torch,用Python語言編寫,支持調(diào)用GPU和CPU優(yōu)化后的Theano運(yùn)算。

2017-11-16 14:20:45 2873

2873 這篇論文對于使用深度學(xué)習(xí)來改進(jìn)IoT領(lǐng)域的數(shù)據(jù)分析和學(xué)習(xí)方法進(jìn)行了詳細(xì)的綜述。

2018-03-01 11:05:12 7452

7452

在研究基于大數(shù)據(jù)框架將深度學(xué)習(xí)的分布式實(shí)現(xiàn)后,王萬良指出,人工智能是大數(shù)據(jù)分析領(lǐng)域的研究主流,基于深度學(xué)習(xí)的大數(shù)據(jù)分析方法發(fā)展最為迅速,GPU成為深度學(xué)習(xí)的更高效的硬件平臺,研究分布式計(jì)算智能優(yōu)化算法將解決大數(shù)據(jù)優(yōu)化問題,能夠提升算法的效果并降低計(jì)算復(fù)雜度。

2018-09-26 16:56:13 8879

8879 了解如何為UltraScale +設(shè)計(jì)添加額外的安全級別。

該視頻演示了如何防止差分功耗分析(DPA),以在比特流配置之上增加額外的安全性。

2018-11-27 06:24:00 2667

2667 本視頻介紹了7系列FPGA的DSP Slice功能。

此外,還討論了Pre-Adder和Dynamic Pipeline控制資源。

2018-11-26 06:02:00 6700

6700 賽靈思的 DSP 架構(gòu)和庫針對 INT8 運(yùn)算進(jìn)行了精心優(yōu)化。本白皮書介紹如何使用賽靈思 16nm 和 20nm All Programmable 器件中的 DSP48E2 Slice,在共享相同內(nèi)核權(quán)重的同時(shí)處理兩個(gè)并行的 INT8 MACC 運(yùn)算。

2019-07-29 11:19:32 2303

2303 要使用可編程邏輯上的 DSP 實(shí)現(xiàn)中值濾波器,可以對算法做改動(dòng)。每次比較運(yùn)算可以分為減法運(yùn)算及后續(xù)的符號位檢查。對減法運(yùn)算,DSP48E2 Slice 能夠以四個(gè) 12 位或兩個(gè) 24 位模式進(jìn)行運(yùn)算。要充分利用 DSP48E2 Slice,可以并行運(yùn)算多個(gè)像素。

2019-07-30 08:59:46 2913

2913

晶心科技今日宣布將攜手合作,在基于AndeStar? V5架構(gòu)的晶心RISC-V CPU核心上配置高度優(yōu)化的深度學(xué)習(xí)模型,使AI深度學(xué)習(xí)模型變得更輕巧、快速和節(jié)能。

2019-12-31 16:30:11 1002

1002 Intel近日發(fā)布了最新版的高性能深度學(xué)習(xí)優(yōu)化庫DNNL 1.2,證實(shí)即將推出的全新Xe架構(gòu)獨(dú)立GPU的一項(xiàng)新技能,那就是支持Int8整數(shù)數(shù)據(jù)類型。

2020-02-04 15:31:19 1258

1258 在深度學(xué)習(xí)中,有很多種優(yōu)化算法,這些算法需要在極高維度(通常參數(shù)有數(shù)百萬個(gè)以上)也即數(shù)百萬維的空間進(jìn)行梯度下降,從最開始的初始點(diǎn)開始,尋找最優(yōu)化的參數(shù),通常這一過程可能會遇到多種的情況

2020-08-28 09:52:45 2268

2268

DSP48最早出現(xiàn)在XilinxVirtex-4 FPGA中,但就乘法器而言,Virtex-II和Virtex-II Pro中就已經(jīng)有了專用的18x18的乘法器,不過DSP48可不只是乘法器,其功能

2020-10-30 17:16:51 5770

5770

深度學(xué)習(xí)是機(jī)器學(xué)習(xí)與神經(jīng)網(wǎng)絡(luò)、人工智能、圖形化建模、優(yōu)化、模式識別和信號處理等技術(shù)融合后產(chǎn)生的一個(gè)領(lǐng)域。

2020-11-05 09:31:19 4711

4711 A、B、C、CARRYIN、CARRYINSEL、OPMODE、BCIN、PCIN、ACIN、ALUMODE、CARRYCASCIN、MULTSIGNIN以及相應(yīng)的時(shí)鐘啟用輸入和復(fù)位輸入都是保留端口。D和INMODE端口對于DSP48E1片是唯一的。本節(jié)詳細(xì)描述DSP48E1片的輸入端口

2022-07-25 18:00:18 4429

4429

在DSP48E1列中,級聯(lián)各個(gè)DSP48E1片可以支持更高級的DSP功能。兩個(gè)數(shù)據(jù)路徑(ACOUT和BCOUT)和DSP48E1片輸出(PCOUT、MULTSIGNOUT和CARRYCASCOUT)提供級聯(lián)功能。級聯(lián)數(shù)據(jù)路徑的能力在過濾器設(shè)計(jì)中很有用。

2021-01-27 07:34:32 8

8 A、B、C、CARRYIN、CARRYINSEL、OPMODE、BCIN、PCIN、ACIN、ALUMODE、CARRYCASCIN、MULTSIGNIN以及相應(yīng)的時(shí)鐘啟用輸入和復(fù)位輸入都是保留端口。D和INMODE端口對于DSP48E1片是唯一的。本節(jié)詳細(xì)描述DSP48E1片的輸入端口

2021-01-27 08:18:02 2

2 深度模型中的優(yōu)化與學(xué)習(xí)課件下載

2021-04-07 16:21:01 3

3 2020年開始,新手機(jī) CPU 幾乎都是 armv8.2 架構(gòu),這個(gè)架構(gòu)引入了新的 fp16 運(yùn)算和 int8 dot 指令,優(yōu)化得當(dāng)就能大幅加速深度學(xué)習(xí)框架的...

2022-01-26 18:53:19 0

0 本文是對NCNN社區(qū)int8模塊的重構(gòu)開發(fā),再也不用擔(dān)心溢出問題了,速度也還行。作者:圈圈蟲首發(fā)知乎傳送門ncnnBUG1989/caffe-int8-conver...

2022-02-07 12:38:26 1

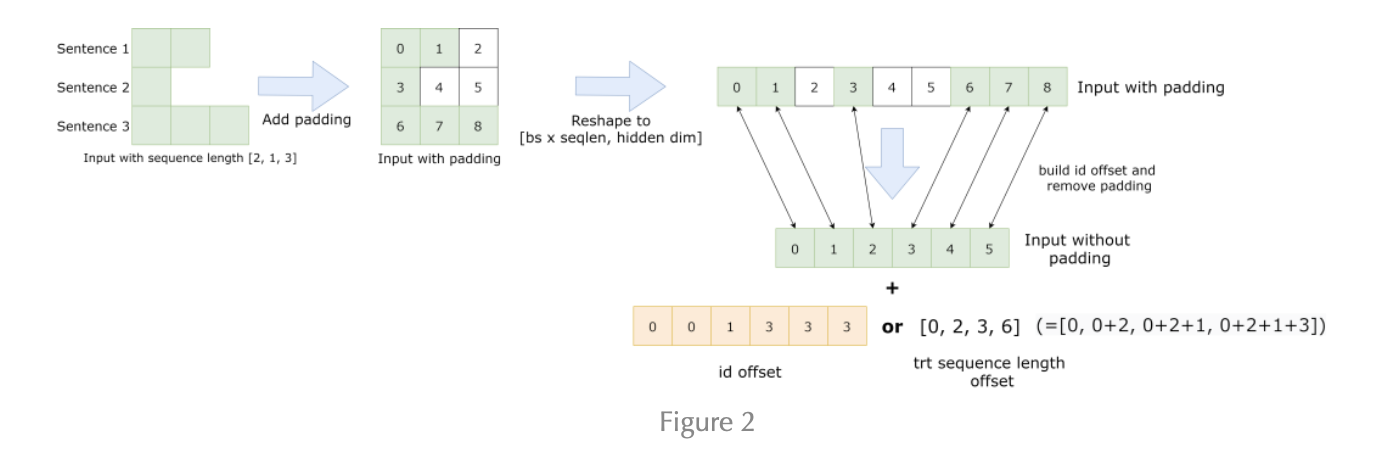

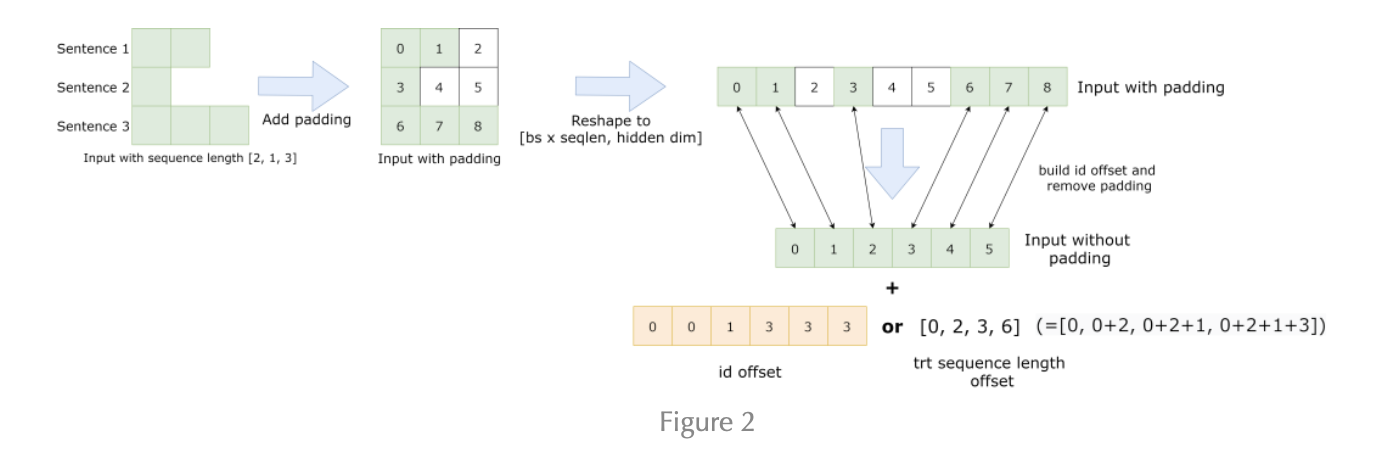

1 FasterTransformer BERT 包含優(yōu)化的 BERT 模型、高效的 FasterTransformer 和 INT8 量化推理。

2023-01-30 09:34:48 1283

1283

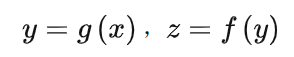

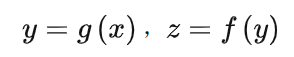

先大致講一下什么是深度學(xué)習(xí)中優(yōu)化算法吧,我們可以把模型比作函數(shù),一種很復(fù)雜的函數(shù):h(f(g(k(x)))),函數(shù)有參數(shù),這些參數(shù)是未知的,深度學(xué)習(xí)中的“學(xué)習(xí)”就是通過訓(xùn)練數(shù)據(jù)求解這些未知的參數(shù)。

2023-02-13 15:31:48 1019

1019

繼續(xù)深度學(xué)習(xí)編譯器的優(yōu)化工作解讀,本篇文章要介紹的是OneFlow系統(tǒng)中如何基于MLIR實(shí)現(xiàn)Layerout Transform。

2023-05-18 17:32:42 389

389 FasterTransformer BERT 包含優(yōu)化的 BERT 模型、高效的 FasterTransformer 和 INT8 量化推理。

2023-05-30 15:15:15 905

905

電子發(fā)燒友網(wǎng)站提供《PyTorch教程12.1之優(yōu)化和深度學(xué)習(xí).pdf》資料免費(fèi)下載

2023-06-05 15:08:41 0

0 12.1. 優(yōu)化和深度學(xué)習(xí)? Colab [火炬]在 Colab 中打開筆記本 Colab [mxnet] Open the notebook in Colab Colab [jax

2023-06-05 15:44:30 327

327

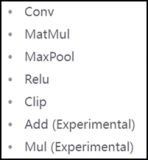

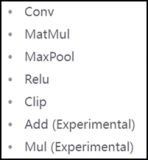

深度學(xué)習(xí)模型量化支持深度學(xué)習(xí)模型部署框架支持的一種輕量化模型與加速模型推理的一種常用手段,ONNXRUNTIME支持模型的簡化、量化等腳本操作,簡單易學(xué),非常實(shí)用。

2023-07-18 09:34:57 2200

2200

INT8量子化PyTorch x86處理器

2023-08-31 14:27:07 453

453

可視化其他量化形式的engine和問題engine進(jìn)行對比,我們發(fā)現(xiàn)是一些層的int8量化會出問題,由此找出問題量化節(jié)點(diǎn)解決。

2023-11-23 16:40:20 531

531

電子發(fā)燒友App

電子發(fā)燒友App

評論