資料介紹

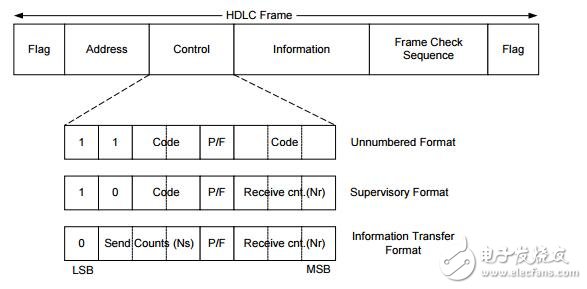

The Teridian 73M2901CE supports the use of a host-based software module for V.42 / MNP 2-4 Error correction Protocol and SDLC operation. These protocol operations require a special mode from the 73M2901CE called quasi-synchronous. This mode of operation is enabled via the ATY4 command. Quasi-synchronous operation (sometimes called the pseudo-synchronous) is a feature of the 73M2901CE modem to perform an asynchronous to synchronous conversion (and vice versa) to the data going over the DTE interface to and from the Host system. The following discussion describes the operation of this mode. HDLC, SDLC, as well as V.42 and MNP Error control protocols, use a synchronous data format. The data is sent via 8 bit octets synchronized by the Transmit and Receive Clocks. A problem arises when sending data to and from the host system because most hosts do not have a synchronous connection to the modem data pump. These systems generally only have an asynchronous UART for sending and receiving serial data. A UART does not use the Transmit and Receive Clocks from the modem; instead it transfers data as characters using extra bits called Start and Stop bits to convey timing information. If the UART is not sending data, the Transmit pin is held in a high, or in a “Marking” state. If the UART wishes to transmit a byte (Octet) of data, a “Start Bit” is transmitted first. A Start Bit or low state is sent for one bit time before the first bit of data is transmitted. After the 8 bits of data are transmitted, the UART returns to the high, or “Marking” state for an additional bit time before more data can be transmitted. This trailing “Marking” time is called the “Stop Bit”。 These extra bits added to the data stream represent 20% more data than what would normally be transmitted with the data bits only. Synchronous data, without a protocol, does not add overhead to the actual data.

- HDLC協議IP核的設計與實現

- 如何使用FPGA實現HDLC協議控制器 15次下載

- 采用FPGA實現同步、幀同步系統的設計 12次下載

- 基于DSP與FPGA實現的HDLC系統 1次下載

- 基于DSP與FPGA實現的HDLC 0次下載

- 異步傳輸方式的HDLC協議的實現 62次下載

- 基于FPGA的HDLC協議控制器 93次下載

- 基于DSP和FPGA的HDLC協議通訊電路設計 98次下載

- WTB網絡HDLC在FPGA中的實現

- 基于FPGA的高速同步HDLC通信控制器設計

- 準同步采樣技術及其DSP實現方法

- 準同步采樣技術及其DSP實現方法

- 基于 ARM 的HDLC 通信的DMA實現

- 基于ARM的HDLC通信的DMA實現

- 準同步寬帶CDMA衛星移動通信分析

- 什么是RS485?淺談RS485組網方式 3301次閱讀

- 同步模式下OpenVINO2023 SDK的推理方式 746次閱讀

- 如何利用DS31256 HDLC控制器實現間隔時鐘應用 743次閱讀

- Rsync遠程數據同步工具簡介 825次閱讀

- 采用Quartus II軟件和EP2C5芯片實現新型位同步提取電路的設計 3359次閱讀

- 采用電流型控制芯片UC3846實現電源交錯并聯時的同步運行設計 6950次閱讀

- 國內地鐵采用什么供電方式 3.6w次閱讀

- HPI接口的工作模式以及與上位主機的連接方式解析 7553次閱讀

- USB控制主機的測試及原理 2208次閱讀

- 如何采用STM32配置SPI實現同步通信 6032次閱讀

- 詳解電梯系統涉及到的兩種主機:異步主機與同步主機 2.1w次閱讀

- 針對飛控模擬裝置的HDLC協議控制器的設計 2675次閱讀

- pwm調制原理同步調制_幾種pwm調制方式介紹 6.9w次閱讀

- 如何實現功率測量的“神同步” 3059次閱讀

- 采用掃描振鏡與高溫計的激光焊接技術 1479次閱讀

下載排行

本周

- 1TPS54202H降壓轉換器評估模塊用戶指南

- 1.02MB | 7次下載 | 免費

- 2DH251全極型霍爾效應傳感器中文手冊

- 0.86 MB | 4次下載 | 免費

- 3RK3506G參考設計

- 0.97 MB | 2次下載 | 3 積分

- 4DMT0660數字萬用表產品說明書

- 0.70 MB | 2次下載 | 免費

- 5U18霍爾效應位置傳感器中文手冊

- 0.73 MB | 1次下載 | 免費

- 6UC3842/3/4/5電源管理芯片中文手冊

- 1.75 MB | 1次下載 | 免費

- 7華瑞昇CR215芯片數字萬用表原理圖

- 0.21 MB | 1次下載 | 3 積分

- 8電涌保護器(SPD)的選擇、安裝以及裝配

- 4.57 MB | 1次下載 | 免費

本月

- 1XL4015+LM358恒壓恒流電路圖

- 0.38 MB | 166次下載 | 1 積分

- 2PCB布線和布局電路設計規則

- 0.40 MB | 77次下載 | 免費

- 3開關電源設計原理手冊

- 1.83 MB | 28次下載 | 免費

- 4智能門鎖原理圖

- 0.39 MB | 26次下載 | 免費

- 5OAH0428最新規格書(中文)

- 2.52 MB | 14次下載 | 7 積分

- 6ADI高性能電源管理解決方案

- 2.43 MB | 13次下載 | 免費

- 72024PMIC市場洞察

- 2.23 MB | 8次下載 | 免費

- 8TPS54202H降壓轉換器評估模塊用戶指南

- 1.02MB | 7次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935115次下載 | 10 積分

- 2開源硬件-PMP21529.1-4 開關降壓/升壓雙向直流/直流轉換器 PCB layout 設計

- 1.48MB | 420061次下載 | 10 積分

- 3Altium DXP2002下載入口

- 未知 | 233084次下載 | 10 積分

- 4電路仿真軟件multisim 10.0免費下載

- 340992 | 191367次下載 | 10 積分

- 5十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183334次下載 | 10 積分

- 6labview8.5下載

- 未知 | 81581次下載 | 10 積分

- 7Keil工具MDK-Arm免費下載

- 0.02 MB | 73806次下載 | 10 積分

- 8LabVIEW 8.6下載

- 未知 | 65986次下載 | 10 積分

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論