資料介紹

1 概述

隨著微電子技術的快速發展,可編程芯片的處理能力也在不斷加強,尤其是DSP芯片正在朝著高速,多指令并行執行的方向發展。DSP處理能力的增強,使得原來運算量很大的算法可以用軟件的方式快速實現。由于軟件處理的靈活性,這給整體的無線電體系結構帶來了深刻的變化。

軟件無線電是指一種基于可編程的,具有一定靈活性的高速信號處理平臺。處理平臺上的設備都可以進行重新配置,將通用化、模塊化、標準化的算法單元用軟件方式實現,根據系統的實際需要,在軟件中添加各種不同算法,可以完成特定的功能,因而可以跨越多種通信標準。當需要從一種標準切換至另一種標準時,處理器能夠動態的在軟件的主要部分切換[1“5]。

2 系統結構設計

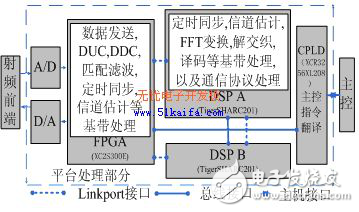

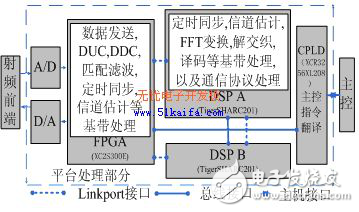

本平臺主要針對寬帶無線數字通信系統物理層的中頻和基帶單元的數字信號處理,如圖1所示,平臺上有兩個DSP(ADI,TigerSHARC201),一個FPGA(Xilinx XC2S300E)和一個CPLD(Xilinx XCR3256XL208)。依據信號處理各模塊的運算特點,以及器件特點,我們將不同的模塊選擇在不同的器件中完成。FPGA設置靈活,但是主頻很難做高,通常低于120MHz,適合于處理可并行計算的模塊;而DSP主頻很高,主要以串行方式執行指令,且DSP支持C語言,所以便于處理通信協議。基于以上特點,FPGA適合處理發送端數據以及數字上變頻(DUC);在接收端適合處理數字下變頻(DDC),匹配濾波器,定時同步等其它基帶處理模塊。DSP適合定時同步,信道估計,FFT變換,解交織,譯碼等其它基帶處理模塊,以及通信協議處理。而CPLD由于其器件特性限制,一般用作主控模塊或主控指令翻譯器。

現代寬帶無線數字通信系統要盡量使用數字信號處理方法來增加可靠性,因此要使用寬帶A/D和D/A,但是由于器件性能局限,我們一般情況下選擇在中頻處使用A/D,D/A。本平臺A/D使用12bit的AD9235,最高采樣率為65MSPS,如果中頻低于65MHz,我們可直接對中頻信號進行采樣,如果中頻頻率較高,可以采用帶通采樣的方法。D/A使用14bi的AD9857,200MSPS,實現中頻輸出。

圖1:平臺結構圖

寬帶無線數字通信系統的一般基帶處理算法中主要分為碼片級處理和符號級處理,同時還有通信協議處理。碼片級信號處理的特點是運算量大,比如定時同步等,所以在以往的系統中大多采用FPGA或ASIC來實現,但是本平臺上的高性能DSP中設置了一些特殊單元,完全可以滿足碼片級處理的要求,表1為DSP處理能力的峰值指標,從此表中我們可以看到其強大的處理能力。符號級處理比如譯碼等,相對來說處理量不是很大,此DSP還提供了增強的指令,使得Viterbi和Turbo碼解碼更快。通信協議處理部分需要很多判斷,跳轉等操作,這部分如果使用FPGA或ASIC處理將使系統開發變得非常慢,而DSP可采用C語言,這點無疑非常適合于通信協議的處理。

表1:DSP處理能力指標

峰值速率

32-bit 浮點性能 3,600 MFLOPS

16-bit算法 執行時間 時鐘周期

256點復數FFT(基2) 1.5μs 901

32-bit算法 執行時間 時鐘周期

1024點復數FFT(基2) 16.8μs 10,061

注:此表中是DSP工作在600MHz時的數據

FPGA作為DSP的硬件協處理器能夠增強功能,改善吞吐量,減小系統成本。本平臺上的FPGA較小,只有100萬邏輯門,在此平臺上主要作為DSP的協處理器。CPLD為主要用于完成主控指令的轉換。

2.1 DSP體系結構簡介

平臺上使用的高性能DSP TigerSHARC201主頻600MHz,其主要特點是能夠進行多指令并行執行,芯片內部集成了一些專用處理模塊,用以保證一些較為復雜的運算指令也能在一時鐘周期處理完畢。

TigerSHARC201內部主要模塊:(1)兩個運算模塊,可以并行執行計算,且每個運算模塊每周期能完成2條運算指令,大大增強了數字信號處理能力,支持定點和浮點運算;(2)兩個整數ALU,能提供強大的地址產生能力和通用的整數操作;(3)六塊片內DRAM共24M bit,每塊4Mbit,用于存儲指令和數據,這種分塊DRAM結構使得DSP可以在取指的同時訪問數據;(4)三條相互獨立的128bit寬片內數據總線,使得指令行能包括4個32bit指令,且提供了許多并行操作以簡化編程。例如,一條指令行可以讓DSP有條件的在兩個運算模塊中分別執行乘,加和減操作,且可以同時跳轉到程序的其它地方。每條片內數據總線都與六個片內DRAM相連,用以保證片內指令和數據的并行高效傳輸[6]。

TigerSHARC201外部接口:(1)一個總線接口,數據線可配置為64bit或32bit,地址線32bit;(2)四個Linkport接口,采用LVDS技術,每個接口能提供額外的全復用4bit接收和發送能力,其最大傳輸速率500Mbytes/s,用于處理器間的點對點高速數據傳輸,為數據傳輸提供了又一種途徑,Linkport接口也是本平臺的最大特點之一[6]。

2.2 數據調度方法

數據調度的原則是:盡量減少芯片間的數據傳輸量。因為芯片間的數據傳輸要走PCB板的數據線,其數據傳輸速率相對較低,而且過于頻繁的板級數據傳輸容易造成系統調度沖突,不便于處理。但是此DSP支持一個特殊的數據傳輸接口——Linkport接口,可以在很大程度上緩解此問題。

使用DSP的Linkport接口分別實現DSP與DSP,DSP與FPGA之間的點對點高速數據傳輸,這樣可滿足數據調度原則,使得系統總體調度變得較為簡單。總線接口只要負責控制指令和小量數據的傳輸就可以了。如果兩個DSP要對同一批數據分別進行處理,那么這時候就要走總線接口,使用廣播的方式進行數據傳遞,即兩個DSP可以同時接收數據,以減少數據調度。平臺上有兩個DSP,根據系統運算量需求來確定使用一個或者兩個都用。DSP間可以形成了一個處理鏈,也可以配置成兩個DSP并行處理。

為了使得平臺便于調度,所以可在平臺上將FPGA或者一個DSP設置為從屬器件。在FPGA中設置控制寄存器和狀態寄存器,在從屬DSP中設置控制變量和狀態變量,DSP通過總線接口來讀寫這些寄存器或者變量以達到控制從屬器件的目的,這樣做相當于硬件平臺上只有一個“大腦”,有利于減小硬件平臺調度沖突。同時FPGA還要通過總線接口接受CPLD(即主控)的控制。

2.3 控制信息處理機制

控制信息處理機制是指DSP作為硬件平臺的核心,如何控制其它從屬器件。一般主要有兩種方法:查詢模式和中斷模式。查詢模式是指從屬器件在特定時刻(一般為某個模塊處理完畢后)會主動讀取DSP發送來的并已事先存儲在緩存中的指令,隨后執行。中斷模式是指DSP發送的指令以中斷的形式強制從屬器件立即執行,從而控制整個硬件平臺。

CPLD主要用來作為主控或者翻譯主控發來的指令,然后將控制信息傳遞給DSP和FPGA。這里CPLD可以直接通過總線接口控制FPGA,也可以通過DSP間接控制FPGA。

隨著微電子技術的快速發展,可編程芯片的處理能力也在不斷加強,尤其是DSP芯片正在朝著高速,多指令并行執行的方向發展。DSP處理能力的增強,使得原來運算量很大的算法可以用軟件的方式快速實現。由于軟件處理的靈活性,這給整體的無線電體系結構帶來了深刻的變化。

軟件無線電是指一種基于可編程的,具有一定靈活性的高速信號處理平臺。處理平臺上的設備都可以進行重新配置,將通用化、模塊化、標準化的算法單元用軟件方式實現,根據系統的實際需要,在軟件中添加各種不同算法,可以完成特定的功能,因而可以跨越多種通信標準。當需要從一種標準切換至另一種標準時,處理器能夠動態的在軟件的主要部分切換[1“5]。

2 系統結構設計

本平臺主要針對寬帶無線數字通信系統物理層的中頻和基帶單元的數字信號處理,如圖1所示,平臺上有兩個DSP(ADI,TigerSHARC201),一個FPGA(Xilinx XC2S300E)和一個CPLD(Xilinx XCR3256XL208)。依據信號處理各模塊的運算特點,以及器件特點,我們將不同的模塊選擇在不同的器件中完成。FPGA設置靈活,但是主頻很難做高,通常低于120MHz,適合于處理可并行計算的模塊;而DSP主頻很高,主要以串行方式執行指令,且DSP支持C語言,所以便于處理通信協議。基于以上特點,FPGA適合處理發送端數據以及數字上變頻(DUC);在接收端適合處理數字下變頻(DDC),匹配濾波器,定時同步等其它基帶處理模塊。DSP適合定時同步,信道估計,FFT變換,解交織,譯碼等其它基帶處理模塊,以及通信協議處理。而CPLD由于其器件特性限制,一般用作主控模塊或主控指令翻譯器。

現代寬帶無線數字通信系統要盡量使用數字信號處理方法來增加可靠性,因此要使用寬帶A/D和D/A,但是由于器件性能局限,我們一般情況下選擇在中頻處使用A/D,D/A。本平臺A/D使用12bit的AD9235,最高采樣率為65MSPS,如果中頻低于65MHz,我們可直接對中頻信號進行采樣,如果中頻頻率較高,可以采用帶通采樣的方法。D/A使用14bi的AD9857,200MSPS,實現中頻輸出。

圖1:平臺結構圖

寬帶無線數字通信系統的一般基帶處理算法中主要分為碼片級處理和符號級處理,同時還有通信協議處理。碼片級信號處理的特點是運算量大,比如定時同步等,所以在以往的系統中大多采用FPGA或ASIC來實現,但是本平臺上的高性能DSP中設置了一些特殊單元,完全可以滿足碼片級處理的要求,表1為DSP處理能力的峰值指標,從此表中我們可以看到其強大的處理能力。符號級處理比如譯碼等,相對來說處理量不是很大,此DSP還提供了增強的指令,使得Viterbi和Turbo碼解碼更快。通信協議處理部分需要很多判斷,跳轉等操作,這部分如果使用FPGA或ASIC處理將使系統開發變得非常慢,而DSP可采用C語言,這點無疑非常適合于通信協議的處理。

表1:DSP處理能力指標

峰值速率

32-bit 浮點性能 3,600 MFLOPS

16-bit算法 執行時間 時鐘周期

256點復數FFT(基2) 1.5μs 901

32-bit算法 執行時間 時鐘周期

1024點復數FFT(基2) 16.8μs 10,061

注:此表中是DSP工作在600MHz時的數據

FPGA作為DSP的硬件協處理器能夠增強功能,改善吞吐量,減小系統成本。本平臺上的FPGA較小,只有100萬邏輯門,在此平臺上主要作為DSP的協處理器。CPLD為主要用于完成主控指令的轉換。

2.1 DSP體系結構簡介

平臺上使用的高性能DSP TigerSHARC201主頻600MHz,其主要特點是能夠進行多指令并行執行,芯片內部集成了一些專用處理模塊,用以保證一些較為復雜的運算指令也能在一時鐘周期處理完畢。

TigerSHARC201內部主要模塊:(1)兩個運算模塊,可以并行執行計算,且每個運算模塊每周期能完成2條運算指令,大大增強了數字信號處理能力,支持定點和浮點運算;(2)兩個整數ALU,能提供強大的地址產生能力和通用的整數操作;(3)六塊片內DRAM共24M bit,每塊4Mbit,用于存儲指令和數據,這種分塊DRAM結構使得DSP可以在取指的同時訪問數據;(4)三條相互獨立的128bit寬片內數據總線,使得指令行能包括4個32bit指令,且提供了許多并行操作以簡化編程。例如,一條指令行可以讓DSP有條件的在兩個運算模塊中分別執行乘,加和減操作,且可以同時跳轉到程序的其它地方。每條片內數據總線都與六個片內DRAM相連,用以保證片內指令和數據的并行高效傳輸[6]。

TigerSHARC201外部接口:(1)一個總線接口,數據線可配置為64bit或32bit,地址線32bit;(2)四個Linkport接口,采用LVDS技術,每個接口能提供額外的全復用4bit接收和發送能力,其最大傳輸速率500Mbytes/s,用于處理器間的點對點高速數據傳輸,為數據傳輸提供了又一種途徑,Linkport接口也是本平臺的最大特點之一[6]。

2.2 數據調度方法

數據調度的原則是:盡量減少芯片間的數據傳輸量。因為芯片間的數據傳輸要走PCB板的數據線,其數據傳輸速率相對較低,而且過于頻繁的板級數據傳輸容易造成系統調度沖突,不便于處理。但是此DSP支持一個特殊的數據傳輸接口——Linkport接口,可以在很大程度上緩解此問題。

使用DSP的Linkport接口分別實現DSP與DSP,DSP與FPGA之間的點對點高速數據傳輸,這樣可滿足數據調度原則,使得系統總體調度變得較為簡單。總線接口只要負責控制指令和小量數據的傳輸就可以了。如果兩個DSP要對同一批數據分別進行處理,那么這時候就要走總線接口,使用廣播的方式進行數據傳遞,即兩個DSP可以同時接收數據,以減少數據調度。平臺上有兩個DSP,根據系統運算量需求來確定使用一個或者兩個都用。DSP間可以形成了一個處理鏈,也可以配置成兩個DSP并行處理。

為了使得平臺便于調度,所以可在平臺上將FPGA或者一個DSP設置為從屬器件。在FPGA中設置控制寄存器和狀態寄存器,在從屬DSP中設置控制變量和狀態變量,DSP通過總線接口來讀寫這些寄存器或者變量以達到控制從屬器件的目的,這樣做相當于硬件平臺上只有一個“大腦”,有利于減小硬件平臺調度沖突。同時FPGA還要通過總線接口接受CPLD(即主控)的控制。

2.3 控制信息處理機制

控制信息處理機制是指DSP作為硬件平臺的核心,如何控制其它從屬器件。一般主要有兩種方法:查詢模式和中斷模式。查詢模式是指從屬器件在特定時刻(一般為某個模塊處理完畢后)會主動讀取DSP發送來的并已事先存儲在緩存中的指令,隨后執行。中斷模式是指DSP發送的指令以中斷的形式強制從屬器件立即執行,從而控制整個硬件平臺。

CPLD主要用來作為主控或者翻譯主控發來的指令,然后將控制信息傳遞給DSP和FPGA。這里CPLD可以直接通過總線接口控制FPGA,也可以通過DSP間接控制FPGA。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- DSP在短波軟件無線電通信系統中的應用 19次下載

- 軟件無線電GPS接收機的DSP實現與優化概述 4次下載

- 軟件無線電基礎 50次下載

- 短波軟件無線電通信系統中的DSP技術簡介 7次下載

- GNU Radio:開放的軟件無線電平臺 10次下載

- 短波軟件無線電通信系統中DSP技術 7次下載

- 基于MATLAB的DSP控制系統仿真平臺設計方案 20次下載

- 軟件無線電RFID測試平臺課件下載 32次下載

- 如何使用軟件無線電實現OFDM系統的設計與實現 11次下載

- 如何使用FPGA實現軟件無線電平臺的設計

- 使用DDC控制器設計中頻無線電接收系統的方案說明 10次下載

- 基于FPGA的軟件無線電平臺設計方案解析 4次下載

- DSP無線圖像傳輸系統的設計方案解析 10次下載

- 軟件無線電中DSP應用模式的分析 11次下載

- 軟件無線電中多DSP系統結構設計 37次下載

- 基于濾波器和混頻器實現軟件無線電的應用設計方案 1851次閱讀

- 基于無線電技術實現基站接收天線感應系統的設計 7281次閱讀

- 基于TigerSHARC201和FPGA實現軟件無線電平臺的設計 2187次閱讀

- 基于DSP及FPGA器件實現軟件無線電多信道發射機系統的設計 3164次閱讀

- 基于Xilinx Virtex6 FPGA的通用軟件無線電平臺設計 1498次閱讀

- 基于新型Virtex FPGA實現小型軟件無線電平臺SFF SDR設計 1205次閱讀

- 軟件無線電硬件平臺的FPGA動態配置 1043次閱讀

- 基于搭建一種具有優秀可移植性的高性能通用軟件無線電平臺的目的 4165次閱讀

- 以軟件無線電為核心的在FPGA基礎上的DQPSK調制解調系統設計方案詳解 4349次閱讀

- 基于FPGA的軟件無線電平臺設計詳細教程 3411次閱讀

- 最新小型軟件無線電平臺SFF SDR介紹 2698次閱讀

- 基于FPGA的通用軟件無線電平臺設計 3554次閱讀

- 基于FPGA+DSP的跳頻電臺傳輸系統的設計方案分析 2179次閱讀

- 基于軟件無線電中頻接收系統的設計方案 2833次閱讀

- 基于SVPWM算法的變頻調速系統設計方案 4800次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費下載

- 0.00 MB | 1489次下載 | 免費

- 2單片機典型實例介紹

- 18.19 MB | 91次下載 | 1 積分

- 3S7-200PLC編程實例詳細資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關電源原理及各功能電路詳解

- 0.38 MB | 9次下載 | 免費

- 6基于AT89C2051/4051單片機編程器的實驗

- 0.11 MB | 4次下載 | 免費

- 7基于單片機和 SG3525的程控開關電源設計

- 0.23 MB | 3次下載 | 免費

- 8基于單片機的紅外風扇遙控

- 0.23 MB | 3次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費

- 4LabView 8.0 專業版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費

- 5555集成電路應用800例(新編版)

- 0.00 MB | 33562次下載 | 免費

- 6接口電路圖大全

- 未知 | 30319次下載 | 免費

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費

- 8開關電源設計實例指南

- 未知 | 21539次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537791次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233045次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191183次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183277次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138039次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論