資料介紹

1 概 述

隨著大規(guī)模集成電路水平的發(fā)展,以數(shù)字信號處理器(Digital Signal Process,DSP)為基礎的實時數(shù)字信號處理技術(shù)正在迅速發(fā)展,現(xiàn)已廣泛應用于圖像處理技術(shù)、語聲處理、智能化儀表、生物醫(yī)學與工程、通信、自動控制等領域。由Analog Device公司生產(chǎn)的ADSP是應用非常廣泛的一類DSP,其典型產(chǎn)品有定點的ADSP2181和浮點的ADSP21060。在許多實際系統(tǒng)中,需要采用多片DSP級聯(lián)的方式進行處理。因此,ADSP2181經(jīng)常經(jīng)級聯(lián)后用在實際系統(tǒng)中,我們設計了基于ISA總線的通用多DSP目標系統(tǒng),這種系統(tǒng)可以用于早期研發(fā)及各種算法的硬件平臺,他對縮短實際系統(tǒng)開發(fā)周期、項目預研等都有重要意義和應用價值。

2 通用多DSP 目標系統(tǒng)的構(gòu)成

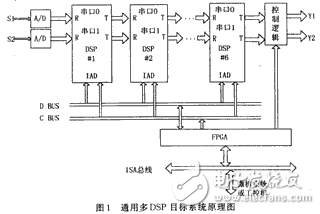

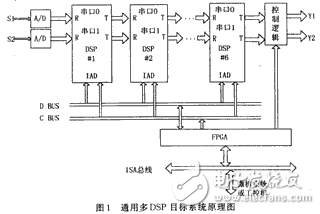

通用多DSP 目標系統(tǒng)的構(gòu)成由6片ADSP2181、2片A/D變換器以及實現(xiàn)邏輯功能的FPGA組成,其原理框圖如圖1所示。

(1)處理系統(tǒng)

整個處理系統(tǒng)由6片DSP構(gòu)成,他完成對2路模擬信號的采集和數(shù)據(jù)處理。本系統(tǒng)采用的是Analog Device公司較為典型的定點DSP系列ADSP2181,相鄰2片DSP之間的串口數(shù)據(jù)的發(fā)送與接收、幀同步信號的發(fā)送與接收分別對應相連,數(shù)據(jù)的傳輸采用自動緩沖的方式。

(2)系統(tǒng)輸入

系統(tǒng)輸入的模擬信號由2路精度為12b的串行A/D變換器完成,采樣率最高達400kS/s,輸入模擬量為單極性(0~2.5V)信號。模擬信號經(jīng)A/D變換器后以串行方式送入第1片DSP。

(3)時序控制

系統(tǒng)時序控制由FPGA(Field Programmable Gate Array,現(xiàn)場可編程門陣列)實現(xiàn),系統(tǒng)采用Altera公司的FPGA芯片EPFl0K10,其實現(xiàn)的主要功能有:

①產(chǎn)生ISA總線對各片DSP訪問的地址譯碼與控制;

②產(chǎn)生通過IDMA端口訪問DSP所需的控制信號IAL,IWR, IRD和IS;

③產(chǎn)生各個DSP的復位信號;

④產(chǎn)生滿足A/D轉(zhuǎn)換器時序要求的控制信號CLK(串口時鐘)和CONV(轉(zhuǎn)換控制)。

另外,F(xiàn)PGA還完成了DSP與ISA總線之間數(shù)據(jù)傳輸所需的控制時序,有效地保證了數(shù)據(jù)傳輸?shù)目煽啃浴?br /> 3 通用多DSP目標系統(tǒng)的硬件設計

(1)目標系統(tǒng)的地址分配與實現(xiàn)

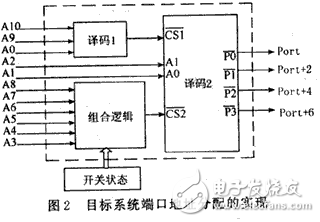

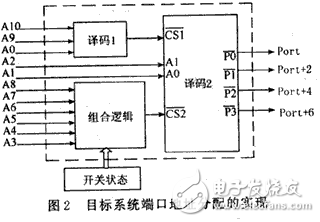

每塊DSP目標板只占用一組端口地址,每組地址共4個:數(shù)據(jù)端口、地址端口、復位端口和控制端口。組起始地址通過4b跳線開關(guān)加以選擇,設開關(guān)值為n,則板卡起始地址為360-4×n(記作port),其他3個端口地址分別為port+2,port+4,port+6。在FPGA中采用如圖2所示的邏輯,實現(xiàn)了目標系統(tǒng)板端口地址的動態(tài)分配。

數(shù)據(jù)端口port 用于實現(xiàn)對DSP內(nèi)部存儲器的讀寫操作,完成DSP與上位機之間的數(shù)據(jù)傳輸。

地址端口port+2 用于提供對DSP進行讀寫操作時DSP內(nèi)部程序存儲區(qū)(PM)或數(shù)據(jù)存儲區(qū)(DM)的起始地址。

復位端口port+4 用于對DSP進行復位操作,實現(xiàn)對DSP的軟復位。

控制端口port+6 用于選擇要操作的DSP。

隨著大規(guī)模集成電路水平的發(fā)展,以數(shù)字信號處理器(Digital Signal Process,DSP)為基礎的實時數(shù)字信號處理技術(shù)正在迅速發(fā)展,現(xiàn)已廣泛應用于圖像處理技術(shù)、語聲處理、智能化儀表、生物醫(yī)學與工程、通信、自動控制等領域。由Analog Device公司生產(chǎn)的ADSP是應用非常廣泛的一類DSP,其典型產(chǎn)品有定點的ADSP2181和浮點的ADSP21060。在許多實際系統(tǒng)中,需要采用多片DSP級聯(lián)的方式進行處理。因此,ADSP2181經(jīng)常經(jīng)級聯(lián)后用在實際系統(tǒng)中,我們設計了基于ISA總線的通用多DSP目標系統(tǒng),這種系統(tǒng)可以用于早期研發(fā)及各種算法的硬件平臺,他對縮短實際系統(tǒng)開發(fā)周期、項目預研等都有重要意義和應用價值。

2 通用多DSP 目標系統(tǒng)的構(gòu)成

通用多DSP 目標系統(tǒng)的構(gòu)成由6片ADSP2181、2片A/D變換器以及實現(xiàn)邏輯功能的FPGA組成,其原理框圖如圖1所示。

(1)處理系統(tǒng)

整個處理系統(tǒng)由6片DSP構(gòu)成,他完成對2路模擬信號的采集和數(shù)據(jù)處理。本系統(tǒng)采用的是Analog Device公司較為典型的定點DSP系列ADSP2181,相鄰2片DSP之間的串口數(shù)據(jù)的發(fā)送與接收、幀同步信號的發(fā)送與接收分別對應相連,數(shù)據(jù)的傳輸采用自動緩沖的方式。

(2)系統(tǒng)輸入

系統(tǒng)輸入的模擬信號由2路精度為12b的串行A/D變換器完成,采樣率最高達400kS/s,輸入模擬量為單極性(0~2.5V)信號。模擬信號經(jīng)A/D變換器后以串行方式送入第1片DSP。

(3)時序控制

系統(tǒng)時序控制由FPGA(Field Programmable Gate Array,現(xiàn)場可編程門陣列)實現(xiàn),系統(tǒng)采用Altera公司的FPGA芯片EPFl0K10,其實現(xiàn)的主要功能有:

①產(chǎn)生ISA總線對各片DSP訪問的地址譯碼與控制;

②產(chǎn)生通過IDMA端口訪問DSP所需的控制信號IAL,IWR, IRD和IS;

③產(chǎn)生各個DSP的復位信號;

④產(chǎn)生滿足A/D轉(zhuǎn)換器時序要求的控制信號CLK(串口時鐘)和CONV(轉(zhuǎn)換控制)。

另外,F(xiàn)PGA還完成了DSP與ISA總線之間數(shù)據(jù)傳輸所需的控制時序,有效地保證了數(shù)據(jù)傳輸?shù)目煽啃浴?br /> 3 通用多DSP目標系統(tǒng)的硬件設計

(1)目標系統(tǒng)的地址分配與實現(xiàn)

每塊DSP目標板只占用一組端口地址,每組地址共4個:數(shù)據(jù)端口、地址端口、復位端口和控制端口。組起始地址通過4b跳線開關(guān)加以選擇,設開關(guān)值為n,則板卡起始地址為360-4×n(記作port),其他3個端口地址分別為port+2,port+4,port+6。在FPGA中采用如圖2所示的邏輯,實現(xiàn)了目標系統(tǒng)板端口地址的動態(tài)分配。

數(shù)據(jù)端口port 用于實現(xiàn)對DSP內(nèi)部存儲器的讀寫操作,完成DSP與上位機之間的數(shù)據(jù)傳輸。

地址端口port+2 用于提供對DSP進行讀寫操作時DSP內(nèi)部程序存儲區(qū)(PM)或數(shù)據(jù)存儲區(qū)(DM)的起始地址。

復位端口port+4 用于對DSP進行復位操作,實現(xiàn)對DSP的軟復位。

控制端口port+6 用于選擇要操作的DSP。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 交流電機系統(tǒng)分析.中英結(jié)合版PDF 0次下載

- 系統(tǒng)分析用戶指南(英文版) 0次下載

- 系統(tǒng)分析方法 0次下載

- 嵌入式實時操作系統(tǒng)分析 10次下載

- §1信號的函數(shù)表示與系統(tǒng)分析方法 0次下載

- 基于SVPWM的變頻系統(tǒng)分析設計 10次下載

- 電力系統(tǒng)分析_下冊 0次下載

- 基于Pspice的電子系統(tǒng)分析 0次下載

- 基于MATLAB的系統(tǒng)分析與設計信號處理 31次下載

- 基于MATLAB的系統(tǒng)分析與設計時頻分析 16次下載

- 自行小車的PLC控制系統(tǒng)分析

- 信號與線性系統(tǒng)分析課件吳大正版 0次下載

- DSP與基于標準總線的DSP系統(tǒng) 42次下載

- 系統(tǒng)分析ppt 0次下載

- 指令系統(tǒng)分析

- 單端口網(wǎng)絡S參數(shù)測量系統(tǒng)分析 479次閱讀

- 基于多通道目標模擬系統(tǒng)構(gòu)建 617次閱讀

- 基于DSP實現(xiàn)多幀數(shù)據(jù)準確通信系統(tǒng)的設計 2050次閱讀

- 基于定點DSP系列ADSP2181芯片實現(xiàn)通用多DSP目標系統(tǒng)的設計 1252次閱讀

- UML軟件分析與建模技術(shù)在嵌入式指紋門禁系統(tǒng)中的應用研究 1791次閱讀

- 基于ISA總線技術(shù)實現(xiàn)多路DDS同步和IQ正交輸出的信號源設計 2279次閱讀

- 如何使用FlexChannel進行多總線系統(tǒng)調(diào)試控制 891次閱讀

- 英創(chuàng)信息技術(shù)ISA總線的CE設備驅(qū)動程序介紹 1501次閱讀

- 精簡ISA擴展總線接口讀寫操作 5167次閱讀

- Tesla Model 3整車的空調(diào)系統(tǒng)分析 2.4w次閱讀

- 基于FPGA的CAM所搭建的空間目標碰撞預警系統(tǒng)分析詳解 2196次閱讀

- 怎樣設計實現(xiàn)一個基于DSP和PCI總線的通信數(shù)據(jù)采集系統(tǒng)? 1690次閱讀

- SEMCAD軟件在電磁兼容、天線系統(tǒng)分析設計中的應用案例 2240次閱讀

- 現(xiàn)場總線在DCS系統(tǒng)中的集成設計 1113次閱讀

- 基于ISA總線多通道控制電路的設計 5664次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費下載

- 0.00 MB | 1489次下載 | 免費

- 2單片機典型實例介紹

- 18.19 MB | 91次下載 | 1 積分

- 3S7-200PLC編程實例詳細資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關(guān)電源原理及各功能電路詳解

- 0.38 MB | 9次下載 | 免費

- 6基于AT89C2051/4051單片機編程器的實驗

- 0.11 MB | 4次下載 | 免費

- 7基于單片機和 SG3525的程控開關(guān)電源設計

- 0.23 MB | 3次下載 | 免費

- 8基于單片機的紅外風扇遙控

- 0.23 MB | 3次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費

- 4LabView 8.0 專業(yè)版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費

- 5555集成電路應用800例(新編版)

- 0.00 MB | 33562次下載 | 免費

- 6接口電路圖大全

- 未知 | 30319次下載 | 免費

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費

- 8開關(guān)電源設計實例指南

- 未知 | 21539次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537791次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233045次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191183次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183277次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138039次下載 | 免費

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評論