通過FPGA的多重配置可以有效地精簡控制結構的設計,同時可以用邏輯資源較少的FPGA器件實現需要很大資源才能實現的程序。以Virtex5系列開發板和配置存儲器SPI FLASH為基礎,從硬件電路

2014-01-24 14:17:22 13670

13670

在FPGA中實現在應用編程(In Application Pro—gramming,IAP)有兩種方法:一種是,在電路板上加外電路。例如用MCU或CPLD來接收配置數據,在被動串行(PS)模式

2020-07-22 16:41:32 1693

1693

隨著FPGA芯片密度的增加,串行PROM已不能適應高密度的FPGA的配置。大容量的并行PROM所要求的尋址方式又不能直接與FPGA接口,這時可以采用XC9500 CPLD和PROM對高密度FPGA

2020-07-23 16:58:08 797

797

的面陣CCD驅動時序發生器設計,基于CPLD的面陣CCD驅動時序發生器設計及其硬件實現,基于CPLD的線陣CCD驅動電路的設計,基于CPLD的線陣CCD驅動電路設計與實現,基于CPLD的線陣CCD驅動

2019-06-03 16:45:25

本人新手,在設計一個cpld的控制電路,需要從flash中讀取數據傳送給其他模塊。由于數據量比較大,cpld內部的flash容量不夠,需要在外部配置一塊存儲量較大的flash芯片,flash芯片中的數據以后會有更新,那么請問除了燒寫器外我用什么方式將數據燒寫進flash?

2013-07-31 11:23:19

電源、地連接到下載線即可。(特權同學,版權所有)說到FPGA的配置,這里不得不提一下他們和CPLD內部存儲介質的不同。CPLD由于大都是基于PROM或FLASH來實現可編程特性,因此對他們進行在線編程

2019-01-30 02:34:52

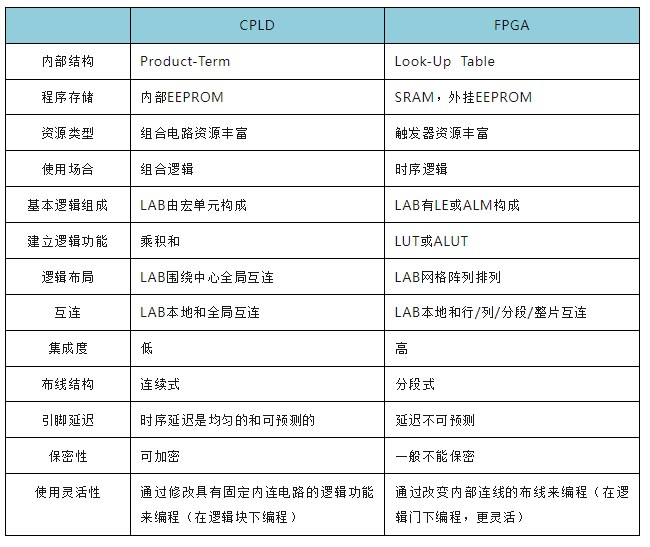

FPGA與CPLD的辨別和分類主要是根據其結構特點和工作原理。通常的分類方法是:將以乘積項結構方式構成邏輯行為的器件稱為CPLD,如Lattice的ispLSI系列、Xilinx的XC9500系列

2019-07-01 07:36:55

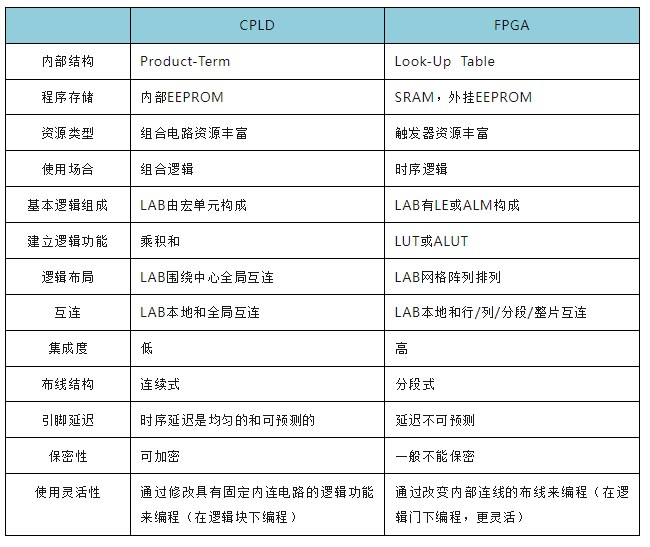

FPGA與CPLD的區別

盡管很多人聽說過CPLD,但是關于CPLD與FPGA之間的區別,了解的人可能不是很多。雖然FPGA與CPLD都是“可反復編程的邏輯器件”,但是在技術上卻有一些差異。簡單

2011-09-27 09:49:48

、路由性能極好,用戶可以改變他們的設計同時保持引腳輸出不變。與FPGA相比,CPLD的I/O更多,尺寸更小。如今,通信系統使用很多標準,必須根據客戶的需要配置設備以支持不同的標準。CPLD可讓設備做出

2012-10-26 08:10:36

和CPLD最大的區別是他們的存儲結構不一樣,這同時也決定了他們的規模不一樣。但是從使用和實現的角度來看,其實他們所使用的語言以及開發流程的各個步驟幾乎是一致的。對于大多數的初學者來說,學FPGA還是

2019-02-21 06:19:27

用CPLD實現。 (2)數據密集型,需要大量的數據處理能力,但邏輯相對簡單,對輸入要求少,適合FPGA實現。7、配置不同 CPLD:采用EPROM,E2PROM工藝,直接寫入,保密性好。 FPGA:采用SRAM工藝,故需外加ROM芯片,用于存儲配置信息。其保密性較差。可實現動態重構。高端FPGA具備加密功能

2020-08-28 15:41:47

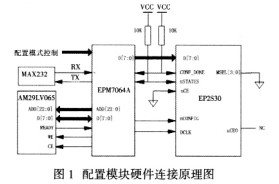

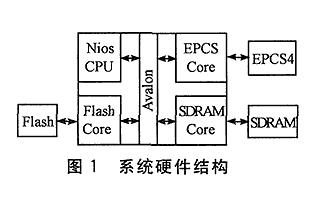

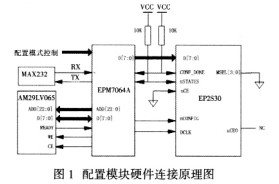

]圖1]3 基于CPLD 的FPGA 加載方案3.1]在 設備端通信產品中,基于CPLD 的FPGA 從并加載框如圖2 所示,配置數據存儲在FLASH 中,且在加載數據之前,CPU 通過局部總線和雙倍

2019-07-12 07:00:09

用“與—或”表達式來描述,所以該“與或陣列”結構能實現大量的組合邏輯功能) 簡單的“與或”陣列:(PAL、GAL、CPLD) 含查找表的邏輯單元:(FPGA) CPLD和FPGA的主要

2020-07-16 10:46:21

電源、地連接到下載線即可。(特權同學,版權所有)說到FPGA的配置,這里不得不提一下他們和CPLD內部存儲介質的不同。CPLD由于大都是基于PROM或FLASH來實現可編程特性,因此對他們進行在線編程

2015-04-13 12:29:55

和CPLD最大的區別是他們的存儲結構不一樣,這同時也決定了他們的規模不一樣。但是從使用和實現的角度來看,其實他們所使用的語言以及開發流程的各個步驟幾乎是一致的。對于大多數的初學者來說,學FPGA還是

2015-03-12 13:54:42

用vhdl實現cpld配置fpga,配置成功后在usermode下設置一個重新配置信號,當信號有效時對fpga進行重新配置;fpga配置程序放在flash內;現在遇到的問題是,上電cpld能夠正常配置fpga并且進入usermode ,但是加上重新配置語句過后就不能成功配置fpga,求高人指點~

2013-01-17 22:35:39

Altera FPGA/CPLD設計與Verilog數字系統設計教程從網上找到了一些Altera FPGA/CPLD經典教材,包含夏宇聞老師的Verilog數字系統設計教程(第2版)Altera FPGA/CPLD設計與Verilog數字系統設計教程

2014-02-17 09:22:18

立題簡介:內容:MCU+CPLD/FPGA實現GPIO擴展與控制;來源:實際得出;作用:MCU+CPLD/FPGA實現GPIO擴展與控制;仿真環境:Quartus II 11.0;日期

2021-11-04 07:42:16

] execute successfully..”即已完成 FPGA 或 CPLD的下載。

2. FPGA 的 Flash 固化

(1)FPGA 的 flash 固化需要先將.sbit 文件轉換成 flash

2023-06-26 10:52:38

XILINX FPGA/CPLD ISE下載教程 第一章 XILINX FPGA/CPLD ISE下載教程——下載.bit文件第二章 XILINX FPGA/CPLD ISE下載教程——燒錄Flash 圖文詳細資料!

2019-08-15 00:32:31

`內容簡介· · · · · ·CPLD/FPGA是目前應用最為廣泛的兩種可編程專用集成電路(ASIC),特別適合于產品的樣品開發與小批量生產。本書從現代電子系統設計的角度出發,以全球著名

2018-03-29 17:11:59

NOR閃存廣泛用作FPGA的配置設備。FPGA在工業和通信及汽車ADAS應用中的使用取決于NOR Flash的低延遲和高數據吞吐量特性。快速啟動時間要求的一個很好的例子是汽車環境中的攝像頭系統。點火

2020-09-18 15:18:38

FPGA的配置,這里不得不提一下他們和CPLD內部存儲介質的不同。CPLD由于大都是基于PROM或Flash來實現可編程特性,因此對他們進行在線編程時就已將配置數據流固化好了,重新上電后還能夠運行固有

2016-07-27 16:45:59

請問哪位仁兄用過MCU、DSP或CPLD之類的芯片通過JTAG實現spartan-3AN(自帶Flash)FPGA配置的?目前使用DSP+FPGA的架構硬件,想通過DSP實現FPGA的升級,目前想到

2014-08-05 16:18:37

、地連接到下載線即可。說到FPGA的配置,這里不得不提一下他們和CPLD內部存儲介質的不同。CPLD由于大都是基于PROM或Flash來實現可編程特性,因此對他們進行在線編程時就已將配置數據流固化好了

2017-10-24 21:26:26

本文介紹了通過處理機用CPLD和Flash實現FPGA配置文件下載更新的方法。

2021-04-28 06:11:19

本文應用EDA技術,基于FPGA/CPLD器件設計與實現UART。

2021-05-07 06:33:09

伙計們,我的電路板提供了在FPGA處于硬復位狀態時讀取SPI閃存的能力(這種能力獨立于FPGA;可以說是“側讀”)。假設我有一個具有有效FPGA配置的SPI Flash。如何確定SPI Flash中

2020-06-09 13:28:04

大家下午好,我計劃使用主fpga板的IO引腳配置目標cpld板,即菊花鏈。我使用主fpga板的IO引腳連接cpld的JTAG頭。如何編程master fpga的IO引腳來配置目標cpld?請發送與此相關的任何文件....謝謝問候Vimala

2020-03-24 06:43:09

從外部存儲器將FPGA配置文件下載更新的方式有哪幾種?如何用CPLD和Flash實現FPGA配置?

2021-04-08 06:07:22

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2019-08-19 06:15:33

),有時我們不需要使用完整的UART的功能和這些輔助功能。或者設計上用到了FPGA/CPLD器件,那么我們就可以將所需要的UART功能集成到FPGA內部。使用VHDL將UART的核心功能集成,從而使整個設計更加緊湊、穩定且可靠。本文應用EDA技術,基于FPGA/CPLD器件設計與實現UART。

2012-05-23 19:37:24

FPGA/CPLD怎么驗證是否正常工作? 現在手頭上有一塊板子,里面有FPGA/CPLD電路,芯片是Spartan-6系列的,現在已經有此芯片的FLASH燒寫程序,也通過燒寫器燒進flash,焊上

2020-06-14 09:04:40

如何通過添加一個簡單的RC電路至FPGA或CPLD 的LVDS輸入來實現模數轉換器?請問怎么實現低頻率(DC至1K Hz)和高頻率(高達50K Hz)ADC?

2021-04-15 06:29:55

XC2S200型FPGA器件實現。采用Spansion公司的NOR Flash存儲器來存放配置文件,其型號為S29GL512N,容量為512 Mb。系統總體框圖如圖3所示。上位機軟件包括Flash燒寫

2019-05-30 05:00:05

針對基于SRAM工藝的器件的下載配置問題,本文介紹采用AT89S2051單片機配合串行E2PROM存儲器,實現CPLD/FPGA器件的被動串行(PS)模式的下載配置。

2021-04-13 06:25:40

《Altera FPGA/CPLD設計(高級篇)》結合作者多年工作經驗,深入地討論了Altera FPGA/CPLD的設計、優化技巧。在討論FPGA/CPLD設計指導原則的基礎上,介紹了Altera器件的高級應用;引領讀者

2009-02-12 09:19:12 4799

4799 結合繼電保護測試裝置的研制體會,介紹基于DSP 的CPLD 多方案現場可編程配置方法,給出硬件的配置連接、CPLD 配置數據的獲取與存儲方法和CPLD 在DSP 控制下的被動串行配置過程。設

2009-04-15 08:50:55 29

29 為配合某電力測量儀表的開發,對Xilinx 公司的SpartanII 系列FPGA 的配置方案進行了探索。該方案采用大容量串行e- Flash 存儲器MM36SB010 存放FPGA 配置文件,MCU 讀取該配置文件并在被動串

2009-04-15 08:58:40 29

29 結合繼電保護測試裝置的研制體會,介紹基于DSP 的CPLD 多方案現場可編程配置方法,給出硬件的配置連接、CPLD 配置數據的獲取與存儲方法和CPLD 在DSP 控制下的被動串行配置過程。設

2009-05-18 14:33:24 16

16 altera fpga/cpld設計 基礎篇結合作者多年工作經驗,系統地介紹了FPGA/CPLD的基本設計方法。在介紹FPGA/CPLD概念的基礎上,介紹了Altera主流FPGA/CPLD的結構與特點,并通過豐富的實例講解

2009-07-10 17:35:45 57

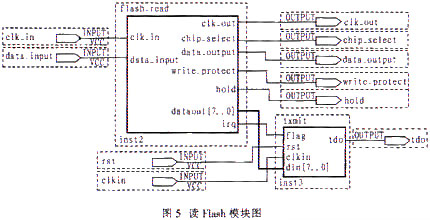

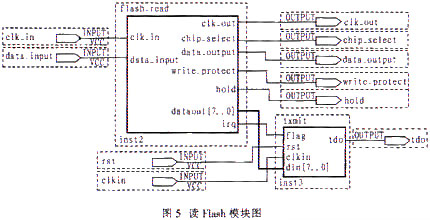

57 在使用Flash 存儲數據時,有時需要對其設計讀寫控制邏輯。本文介紹了用VHDL 語言在CPLD內部編程,實現對Flash 中數據的讀取控制的具體方法,并給出

2009-09-04 09:29:36 35

35 UART 是廣泛使用的串行數據通訊電路。本設計包含UART 發送器、接收器和波特率發生器。設計應用EDA 技術,基于FPGA/CPLD 器件設計與實現UART。關鍵詞 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 23

23 基于單片機的CPLD/FPGA被動串行下載配置的實現:介紹采用AT89S2051單片機配合串行E2PROM存儲器,實現CPLD/FPGA器件的被動串行模式的下載配置,闡述了其原理及軟硬件設計。 &nb

2009-10-29 21:57:22 19

19 CPLD是復雜的可編程邏輯器件(Complex Programable Logic Device)的簡稱,FPGA是可編程門現場可編程門陣列,不同廠家有不同的稱呼,Xilinx把SRAM工藝,要外掛配置用的EPROM的PLD叫FPGA,把Flash工

2009-11-12 14:22:36 117

117 當利用CPLD/FPGA開發系統完成數字電路或系統的開發設計并仿真校驗通過之后,就需要將獲得的CPLD/FPGA編程配置數據下載到CPLD/FPGA芯片中,以便最后獲得所設計的硬件數字電路或系

2010-06-01 10:14:46 23

23 本文舉例分析了DSP的引導裝載過程和FPGA的配置流程,并據此提出了一種使用單個FLASH存儲器實現上述兩個功能的方法。

2010-07-21 17:14:42 12

12 摘 要 :UART是廣泛使用的串行數據通訊電路。本設計包含UART發送器、接收器和波特率發生器。設計應用EDA技術,基于FPGA/CPLD器件設計與實現UART。

2009-06-20 13:14:52 982

982

基于CPLD/FPGA的多功能分頻器的設計與實現

引言

分頻器在CPLD/FPGA設計中使用頻率比較高,盡管目前大部分設計中采用芯片廠家集成的鎖相環資源 ,但是對于要求

2009-11-23 10:39:48 1139

1139

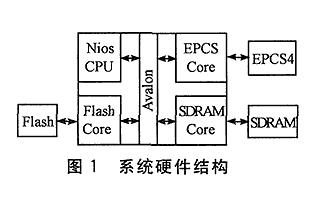

基于FPGA的串行Flash擴展實現

FPGA憑借其方便靈活、可重復編程等優點而日益被廣泛應用;閃速存儲器(Flash Memory)以其集成度高、成本低、使用方便等優點,在眾多領域中

2010-01-12 10:39:55 1363

1363

FPGA重復配置和測試的實現

從制造的角度來講,FPGA測試是指對FPGA器件內部的邏輯塊、可編程互聯線、輸入輸出塊等資源的檢測。完整的FPGA測試包括兩步,一是配置FPGA

2010-01-26 09:39:56 544

544

常用FPGA/CPLD四種設計技巧

FPGA/CPLD的設計思想與技巧是一個非常大的話題,本文僅介紹一些常用的設計思想與技巧,包括乒乓球操作、串并轉換、流水線操作和數據接口

2010-05-12 11:10:43 766

766

基于FPGA和CPLD數字邏輯實現ADC技術

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現

2010-05-25 09:39:10 1309

1309

本文討論的四種常用FPGA/CPLD設計思想與技巧:乒乓操作、串并轉換、流水線操作、數據接口同步化,都是FPGA/CPLD邏輯設計的內在規律的

2010-11-04 10:11:28 625

625

本章將首先介紹FPGA配置方式和配置過程,然后簡單介紹了配置芯片、配置文件的種類以及配置電路設計要點,本章最后講述了配置文件下載、Flash編程等方面的內容,其中Flash編程包括

2011-03-22 10:53:46 801

801 SPI方式FPGA配置和SPI flash編程

2011-05-16 18:01:02 164

164 本文結合具體應用需求,介紹了利用嵌入式CPU Leon3軟核處理器對Virtex系列FPGA的配置進行控制的方法。此系統能夠實現FPGA配置數據的重構,并且減少了外圍CPU和CPLD器件的使用,具有很好

2011-07-04 10:13:41 3151

3151

UART 是廣泛使用的串行數據通訊電路。本設計包含UART 發送器、接收器和波特率發生器。設計應用EDA 技術,基于FPGA/CPLD 器件設計與實現UART。

2011-12-17 00:15:00 57

57 FPGA和CPLD的區別,以及設計思路思想

2016-02-17 11:20:56 38

38 SVPWM算法優化及其FPGA_CPLD實現

2016-04-13 15:42:35 18

18 基于FPGA/CPLD的UART功能設計

2017-01-23 20:45:37 30

30 的橋接的,難道FPGA內部有專用的電路去實現這一功能嗎? 其實不是的。FPGA內部并沒有設計(預留)專用的電路去實現JTAG到Flash的轉換,在我們通過JTAG燒寫Flash時,電腦其實是先要預下載

2017-02-08 02:40:11 6513

6513

CPLD和FPGA都是我們經常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區分,把他們都叫做FPGA。那么兩者到底有什么區別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區別。

2017-09-18 16:35:32 5

5 FPGA/CPLD能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA/CPLD來實現。 FPGA/CPLD如同一張白紙或是一堆積木,工程師可以通過傳統的原理圖輸入法

2017-10-09 09:52:20 14

14 隨著FPGA的廣泛應用, 其實現的功能也越來越多, FPGA 的動態重構設計就顯得愈發重要。在分析Xilinx Vertex II Pro系列FPGA配置流程、時序要求的基礎上, 設計了基于CPLD

2017-11-22 07:55:01 937

937

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2018-04-26 11:53:00 1121

1121

在FPGA中實現在應用編程(In Application Programming,IAP)有兩種方法:一種是,在電路板上加外電路。例如用MCU或CPLD來接收配置數據,在被動串行(PS)模式

2017-12-13 13:58:10 24009

24009

FPGA LAB和CPLD的LAB設計不同。CPLD LAB由宏單元構成,包括自己的本地可編程陣列,而FPGA LAB由大量的邏輯模塊構成,這些模塊被稱為邏輯單元,即LE,而且本地互連和邏輯分開。LE看起來可能和CPLD宏單元相似,但更容易配置,有更豐富的特性來提高性能,減少邏輯資源的浪費。

2018-04-17 17:02:00 1979

1979

CPLD和FPGA都是我們經常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區分,把他們都叫做FPGA。那么兩者到底有什么區別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區別。

2018-05-24 02:03:00 49472

49472

現代高速度FPGA運行時需將其配置數據加載到內部SDRAM中,改變SDRAM里面的數據,可使FPGA實現不同的功能,即所謂的可重構技術。可重構技術包括靜態系統重構和動態系統重構。在FPGA處于工作

2019-06-10 08:17:00 2799

2799

CPLD通常用于實現前面提到的簡單組合邏輯功能,并負責“引導”FPGA以及控制整個電路板的復位和引導順序。

2018-09-27 11:56:01 6191

6191 介紹了采用CPLD和Flash器件對FPGA 實現快速并行配置,并給出了具體的硬件電路設計和關鍵模塊的內部編程思路。

2018-10-24 15:15:49 7

7 Altera FPGA支持AS,PS,JTAG等幾種較常見的配置方法。 當為AS配置模式時,FPGA為主設備,加載外部FLASH中的數據至內部RAM中運行。當為PS配置模式時,FPGA為從設備,外部

2018-11-18 18:05:01 481

481 本文檔詳細介紹的是FPGA教程之CPLD與FPGA的基礎知識說明主要內容包括了:一、復雜可編程邏輯器件簡介二、CPLD的組成與特點三、FPGA的組成與特點四、CPLD與FPGA的異同五、主要的PLD廠商

2019-02-27 17:09:32 32

32 本文檔詳細介紹的是FPGA教程之CPLD和FPGA的配置與下載的詳細資料說明主要內容包括了:一、CPLD/FPGA器件的配置,二、MAX系列非易失性器件的下載配置,三、FLEX/ACEX系列FPGA的下載配置,四、ALTERA的編程文件

2019-02-28 09:56:18 17

17 與CPLD不同,FPGA是基于SRAM結構的(Actel也有基于Flash結構的FPGA,但不是今天討論的重點),所以FPGA每次上電都需要重新配置,而不像CPLD那樣能夠直接運行固化在芯片內的代碼

2019-03-05 14:16:27 6

6 對于CPLD/FPGA初學者而言,如何實現雙向信號往往是個難題。duoduo 當年初接觸CPLD/FPGA的時候也為這個問題頭疼過。讓我們透過下面這個簡單的例子看看CPLD/FPGA設計中如何實現雙向信號。

2019-06-11 16:13:51 15

15 CPLD和FPGA都是我們經常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區分,把他們都叫做FPGA。

2019-09-13 14:58:00 5135

5135 FPGA/CPLD能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA/CPLD來實現。

2020-01-20 09:29:00 3264

3264 Altera CPLD和配置設備,并配置Altera FPGA設備。在你的設計成功編譯后,你可以使用Quartus II程序員來編程或配置你的設備。

2020-09-17 14:41:00 32

32 本文主要介紹CPLD和FPGA的基本結構。 CPLD是復雜可編程邏輯器件(Complex Programable Logic Device)的簡稱,FPGA是現場可編程門陣列(Field

2020-09-25 14:56:33 12233

12233

CPLD/FPGA的基本知識講解。

2021-03-30 09:55:18 27

27 FPGA_ASIC-DSP和FPGA共用FLASH進行配置的方法(哪些專業適合嵌入式開發)-該文檔為FPGA_ASIC-DSP和FPGA共用FLASH進行配置的方法講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 11:16:55 21

21 廣義的來說,FPGA的配置包括直接使用下載電纜對FPGA器件進行編程、對外部EEPROM和FLASH進行編程、使用MPU對FPGA器件進行編程、外部EEPROM和FLASH對器件進行編程

2021-09-06 09:41:56 6052

6052 FPGA CPLD可編程邏輯器件的在系統配置方法(深圳市村田電源技術有限公司)-FPGA CPLD可編程邏輯器件的在系統配置方法? ? ? ? ? ? ? ? ? ?

2021-09-18 10:51:20 13

13 Altera FPGA CPLD學習筆記(肇慶理士電源技術有限)-Altera FPGA CPLD學習筆記? ? ? ? ? ? ? ? ?

2021-09-18 10:54:41 79

79 FPGA CPLD中的Verilog設計小技巧(肇慶理士電源技術有限)-FPGA CPLD中的Verilog設計小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 35

35 立題簡介:內容:MCU+CPLD/FPGA實現GPIO擴展與控制;來源:實際得出;作用:MCU+CPLD/FPGA實現GPIO擴展與控制;仿真環境:Quartus II 11.0;日期

2021-10-29 10:21:11 2

2 都是FPGA/CPLD邏輯設計的內在規律的體現,合理地采用這些設計思想能在FPGA/CPLD設計工作種取得事半功倍的效果。

2023-05-18 08:56:57 350

350

CPLD和FPGA都是由邏輯陣列模塊構成的,但是CPLD的LAB基于乘積和宏單元,而FPGA的LAB使用基于LUT的邏輯單元。

2023-06-28 11:28:04 862

862

可編程邏輯包括 PAL、GAL、PLD 等。通過不斷發展,它已經發展成為現在的CPLD/FPGA。CPLD(復雜可編程邏輯器件)和FPGA(現場可編程門陣列)的功能基本相同,只是實現原理略有不同

2023-07-03 14:33:38 6041

6041

FPGA(現場可編程門陣列)是一種高度靈活的硬件設備,可以根據特定的需求進行重新配置。FPGA通常用于處理大量數據和實時計算。然而,FPGA通常并沒有內置大容量的數據存儲器,例如硬盤或固態硬盤。這就

2023-12-15 15:42:51 544

544

電子發燒友App

電子發燒友App

評論