資料介紹

15.3 高速緩沖存儲器Cache

當?shù)谝淮?a target='_blank' class='arckwlink_none'>RISC微處理器剛出現(xiàn)時,標準存儲器元件的速度比當時微處理器的速度快。很快,半導體工藝技術的進展被用來提高微處理器的速度。標準DRAM部件雖然也快了一些,但其發(fā)展的主要精力則放在提高存儲容量上。

1980年,典型DRAM部件的容量為4KB。1981年和1982年開發(fā)出了16KB芯片。這些部件的隨機訪問速率為3MHz或4MHz,局部訪問(頁模式)時速率大約快1倍。當時的微處理器每秒需要訪問存儲器2M次。

到2000年,DRAM部件每片的容量到達256Mbit,隨機訪問速率在30MHz左右。微處理器每秒需要訪問存儲器幾百兆次。如果處理器速率遠高于存儲器,那么只能借助Cache才能滿足其全部性能。

Cache存儲器是一個容量小但存取速度非常快的存儲器,它保存最近用到的存儲器數(shù)據(jù)拷貝。對于程序員來說,Cache是透明的。它自動決定保存哪些數(shù)據(jù)、覆蓋哪些數(shù)據(jù)。現(xiàn)在Cache通常與處理器在同一芯片上實現(xiàn)。Cache能夠發(fā)揮作用是因為程序具有局部性特性。所謂局部性就是指,在任何特定的時間,微處理器趨于對相同區(qū)域的數(shù)據(jù)(如堆棧)多次執(zhí)行相同的指令(如循環(huán))。

Cache經常與寫緩存器(write buffer)一起使用。寫緩存器是一個非常小的先進先出(FIFO)存儲器,位于處理器核與主存之間。使用寫緩存的目的是,將處理器核和Cache從較慢的主存寫操作中解脫出來。當CPU向主存儲器做寫入操作時,它先將數(shù)據(jù)寫入到寫緩存區(qū)中,由于寫緩存器的速度很高,這種寫入操作的速度也將很高。寫緩存區(qū)在CPU空閑時,以較低的速度將數(shù)據(jù)寫入到主存儲器中相應的位置。

通過引入Cache和寫緩存區(qū),存儲系統(tǒng)的性能得到了很大的提高,但同時也帶來了一些問題。比如,由于數(shù)據(jù)將存在于系統(tǒng)中的不同的物理位置,可能造成數(shù)據(jù)的不一致性;由于寫緩存區(qū)的優(yōu)化作用,可能有些寫操作的執(zhí)行順序不是用戶期望的順序,從而造成操作錯誤。

15.3.1 Cache的分類

Cache有多種構造方法。在最高層次,微處理器可以采用下面兩種組織中的一組。

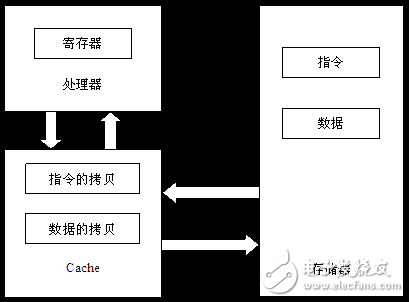

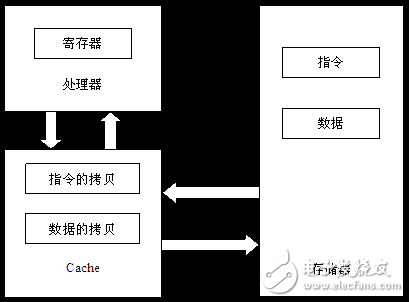

(1)統(tǒng)一Cache。指令和數(shù)據(jù)用同一個Cache。結構如圖15.8所示。

圖15.8 統(tǒng)一的指令Cache和數(shù)據(jù)Cache

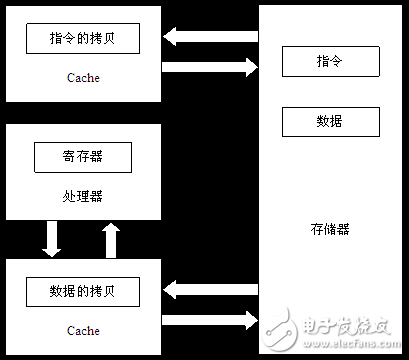

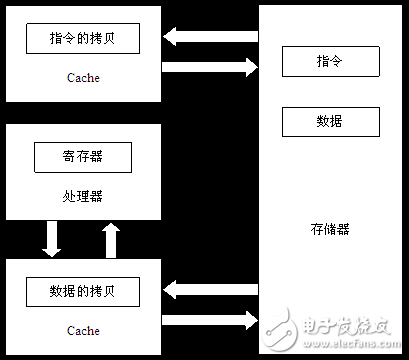

(2)指令和數(shù)據(jù)分開的Cache。有時這種組織方式也被稱為改進的哈佛結構。

圖15.9顯示了這種組織方式。

這兩種組織方式各有優(yōu)缺點。統(tǒng)一Cache能夠根據(jù)當前程序的需要自動調整指令在Cache存儲器的比例,比固定劃分的有更好的性能。另一方面,分開的Cache使Load/Store指令能夠單周期執(zhí)行。

15.3.2 Cache性能的衡量

只有當所需要的Cache存儲器內容已經在Cache時,微處理器才能以高時鐘速率工作。因此,系統(tǒng)的總體性能就可以用存儲器訪問中命中Cache的比例來衡量。當要訪問的內容在Cache時稱為命中(hit),而要訪問的內容不在Cache時稱為未命中(miss)。在給定時間間隔內,Cache命中的次數(shù)與總的存儲器請求次數(shù)的比值被稱為命中率。

圖15.9 指令Cache和數(shù)據(jù)分開的Cache

命中率用下面的公式進行計算:

命中率=(Cache命中次數(shù)÷存儲器請求次數(shù))×100%

未命中率與命中率形式相似,即在給定時間間隔內,Cache未命中的總次數(shù)除以總的存儲器請求次數(shù)所得的百分比。未命中率與命中率之和等于100。

目前設計良好的處理器,Cache的未命中率只有百分之幾。未命中率依賴多個Cache參數(shù),包括Cache大小和組織。

15.3.3 Cache工作原理

Cache的基本存儲單元為Cache行(Cache line)。存儲系統(tǒng)把Cache和主存儲器都劃分為相同大小的行。Cache與主存儲器交換數(shù)據(jù)是以行為基本單位進行的。每一個Cache行都對應于主存中的一個存儲塊(memory block)。

Cache行的大小通常是2L字節(jié)。通常情況下是16字節(jié)(4個字)和32字節(jié)(8個字)。如果Cache行的大小為2L字節(jié),那么對主存的訪問通常是2L字節(jié)對齊的。所以對于一個虛擬地址來說,它的bit[31∶L]位,是Cache行的一個標識。當CPU發(fā)出的虛擬地址的bit[31∶L]和Cache中的某行bit[31∶L]相同,那么Cache中包含CPU要訪問的數(shù)據(jù),即成為一次Cache命中。

為了加快Cache訪問的速度,又將多個Cache行劃分成一個Cache組(Cache Set)。Cache組中包含的Cache行的個數(shù)通常也為2的N次方的倍數(shù)。為了方便起見,取N=S。這樣,一個Cache組中就包含2S個Cache行。這時,虛擬地址中的bit[L+S-1∶L]為Cache組的標識。虛擬地址中余下的位bit[31∶L+S]成為一個Cache標(Cache-tag)。它標識了Cache行中的內容和主存間的對應關系。

當?shù)谝淮?a target='_blank' class='arckwlink_none'>RISC微處理器剛出現(xiàn)時,標準存儲器元件的速度比當時微處理器的速度快。很快,半導體工藝技術的進展被用來提高微處理器的速度。標準DRAM部件雖然也快了一些,但其發(fā)展的主要精力則放在提高存儲容量上。

1980年,典型DRAM部件的容量為4KB。1981年和1982年開發(fā)出了16KB芯片。這些部件的隨機訪問速率為3MHz或4MHz,局部訪問(頁模式)時速率大約快1倍。當時的微處理器每秒需要訪問存儲器2M次。

到2000年,DRAM部件每片的容量到達256Mbit,隨機訪問速率在30MHz左右。微處理器每秒需要訪問存儲器幾百兆次。如果處理器速率遠高于存儲器,那么只能借助Cache才能滿足其全部性能。

Cache存儲器是一個容量小但存取速度非常快的存儲器,它保存最近用到的存儲器數(shù)據(jù)拷貝。對于程序員來說,Cache是透明的。它自動決定保存哪些數(shù)據(jù)、覆蓋哪些數(shù)據(jù)。現(xiàn)在Cache通常與處理器在同一芯片上實現(xiàn)。Cache能夠發(fā)揮作用是因為程序具有局部性特性。所謂局部性就是指,在任何特定的時間,微處理器趨于對相同區(qū)域的數(shù)據(jù)(如堆棧)多次執(zhí)行相同的指令(如循環(huán))。

Cache經常與寫緩存器(write buffer)一起使用。寫緩存器是一個非常小的先進先出(FIFO)存儲器,位于處理器核與主存之間。使用寫緩存的目的是,將處理器核和Cache從較慢的主存寫操作中解脫出來。當CPU向主存儲器做寫入操作時,它先將數(shù)據(jù)寫入到寫緩存區(qū)中,由于寫緩存器的速度很高,這種寫入操作的速度也將很高。寫緩存區(qū)在CPU空閑時,以較低的速度將數(shù)據(jù)寫入到主存儲器中相應的位置。

通過引入Cache和寫緩存區(qū),存儲系統(tǒng)的性能得到了很大的提高,但同時也帶來了一些問題。比如,由于數(shù)據(jù)將存在于系統(tǒng)中的不同的物理位置,可能造成數(shù)據(jù)的不一致性;由于寫緩存區(qū)的優(yōu)化作用,可能有些寫操作的執(zhí)行順序不是用戶期望的順序,從而造成操作錯誤。

15.3.1 Cache的分類

Cache有多種構造方法。在最高層次,微處理器可以采用下面兩種組織中的一組。

(1)統(tǒng)一Cache。指令和數(shù)據(jù)用同一個Cache。結構如圖15.8所示。

圖15.8 統(tǒng)一的指令Cache和數(shù)據(jù)Cache

(2)指令和數(shù)據(jù)分開的Cache。有時這種組織方式也被稱為改進的哈佛結構。

圖15.9顯示了這種組織方式。

這兩種組織方式各有優(yōu)缺點。統(tǒng)一Cache能夠根據(jù)當前程序的需要自動調整指令在Cache存儲器的比例,比固定劃分的有更好的性能。另一方面,分開的Cache使Load/Store指令能夠單周期執(zhí)行。

15.3.2 Cache性能的衡量

只有當所需要的Cache存儲器內容已經在Cache時,微處理器才能以高時鐘速率工作。因此,系統(tǒng)的總體性能就可以用存儲器訪問中命中Cache的比例來衡量。當要訪問的內容在Cache時稱為命中(hit),而要訪問的內容不在Cache時稱為未命中(miss)。在給定時間間隔內,Cache命中的次數(shù)與總的存儲器請求次數(shù)的比值被稱為命中率。

圖15.9 指令Cache和數(shù)據(jù)分開的Cache

命中率用下面的公式進行計算:

命中率=(Cache命中次數(shù)÷存儲器請求次數(shù))×100%

未命中率與命中率形式相似,即在給定時間間隔內,Cache未命中的總次數(shù)除以總的存儲器請求次數(shù)所得的百分比。未命中率與命中率之和等于100。

目前設計良好的處理器,Cache的未命中率只有百分之幾。未命中率依賴多個Cache參數(shù),包括Cache大小和組織。

15.3.3 Cache工作原理

Cache的基本存儲單元為Cache行(Cache line)。存儲系統(tǒng)把Cache和主存儲器都劃分為相同大小的行。Cache與主存儲器交換數(shù)據(jù)是以行為基本單位進行的。每一個Cache行都對應于主存中的一個存儲塊(memory block)。

Cache行的大小通常是2L字節(jié)。通常情況下是16字節(jié)(4個字)和32字節(jié)(8個字)。如果Cache行的大小為2L字節(jié),那么對主存的訪問通常是2L字節(jié)對齊的。所以對于一個虛擬地址來說,它的bit[31∶L]位,是Cache行的一個標識。當CPU發(fā)出的虛擬地址的bit[31∶L]和Cache中的某行bit[31∶L]相同,那么Cache中包含CPU要訪問的數(shù)據(jù),即成為一次Cache命中。

為了加快Cache訪問的速度,又將多個Cache行劃分成一個Cache組(Cache Set)。Cache組中包含的Cache行的個數(shù)通常也為2的N次方的倍數(shù)。為了方便起見,取N=S。這樣,一個Cache組中就包含2S個Cache行。這時,虛擬地址中的bit[L+S-1∶L]為Cache組的標識。虛擬地址中余下的位bit[31∶L+S]成為一個Cache標(Cache-tag)。它標識了Cache行中的內容和主存間的對應關系。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- EE-271: 高速缓冲存储器在Blackfin处理器中的应用0次下载

- EE-271: 高速缓冲存储器在Blackfin®处理器中的应用8次下载

- PLC系统的存储器分类详细资料介绍4次下载

- 如何使用eMMC阵列进行高速固态存储器的研究与设计33次下载

- 单片机存储器的工作原理和结构与半导体存储器的分类说明4次下载

- SDRAM存储器相关资料下载49次下载

- Trace32高速缓冲寄存器18次下载

- 低功耗的高性能四路组相联CMOS高速缓冲存储器12次下载

- 存储器和高速缓存技术67次下载

- S698M SoC芯片中Cache控制器的设计与实现9次下载

- ML2308双通道录音/播放LSI,内置缓冲存储器34次下载

- 半导体存储器电路及结构89次下载

- 存储器.ppt0次下载

- 存储器接口50次下载

- 存储器的分类及原理20次下载

- 內存儲器的分類和特點是什么 1040次閱讀

- 內存儲器分為隨機存儲器和什么 1354次閱讀

- 內存儲器與外存儲器的主要區(qū)別 5552次閱讀

- 存儲器的定義和分類 1465次閱讀

- PLC系統(tǒng)的存儲器分類介紹 6769次閱讀

- 存儲器分類及各自優(yōu)劣勢介紹 5860次閱讀

- 計算機存儲器的作用和分類說明 1w次閱讀

- 半導體存儲器有哪些類型 1.6w次閱讀

- 內存儲器和外存儲器的分類與區(qū)別 4w次閱讀

- 隨機存取存儲器為什么叫隨機存取存儲器(結構、特點、分類、優(yōu)缺點) 2.1w次閱讀

- 計算機的存儲器主要作用_計算機的存儲器的分類介紹 1.1w次閱讀

- Cache是什么 CPU和GPU對于cache的應用 8708次閱讀

- 高速緩沖存儲器基礎知識詳細介紹 1w次閱讀

- 高速緩沖存儲器的作用是什么_有什么特點 2w次閱讀

- 存儲器分類及各自特點有哪些 1.7w次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費下載

- 0.00 MB | 1490次下載 | 免費

- 2單片機典型實例介紹

- 18.19 MB | 92次下載 | 1 積分

- 3S7-200PLC編程實例詳細資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關電源原理及各功能電路詳解

- 0.38 MB | 10次下載 | 免費

- 6基于AT89C2051/4051單片機編程器的實驗

- 0.11 MB | 4次下載 | 免費

- 7藍牙設備在嵌入式領域的廣泛應用

- 0.63 MB | 3次下載 | 免費

- 89天練會電子電路識圖

- 5.91 MB | 3次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費

- 4LabView 8.0 專業(yè)版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費

- 5555集成電路應用800例(新編版)

- 0.00 MB | 33562次下載 | 免費

- 6接口電路圖大全

- 未知 | 30320次下載 | 免費

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費

- 8開關電源設計實例指南

- 未知 | 21539次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537791次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233045次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191183次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183277次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138039次下載 | 免費

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評論