資料介紹

1引言

目前,集成電路的嵌入式技術(shù)發(fā)展越來越快,各色嵌入式產(chǎn)品也越來越受歡迎,尤其是以大屏幕多功能的手機(jī)、平板電腦等為典型代表,做為其控制核心的高性能、低功耗的微控制器(MCU)起到了決定性作用。因此以CPU為核心MCU的設(shè)計(jì)也成為了諸多高等院校、各大公司進(jìn)行市場(chǎng)競(jìng)爭(zhēng)的一個(gè)主流發(fā)展方向。

2 MCU選型技術(shù)

微控制器(MCU)的應(yīng)用領(lǐng)域非常廣泛,如消費(fèi)類電子市場(chǎng)中的手機(jī)、照相機(jī)、攝像機(jī)、MP3、MP4、平板電腦、筆記本電腦、PC機(jī)、各種遙控電動(dòng)玩具等,還有汽車電子的電子鑰匙、控制系統(tǒng)、導(dǎo)航、倒車影像、倒車?yán)走_(dá)等,還有各種安全防衛(wèi)系統(tǒng)、醫(yī)療器械、工業(yè)控制、武器裝備、航空航天等各個(gè)領(lǐng)域。因此在設(shè)計(jì)MCU之前需要進(jìn)行明確的市場(chǎng)定位,從而使目標(biāo)產(chǎn)品有的放矢,并在高性能、低成本、多功能、輕體積、低功耗、高可靠、散熱好、抗輻照、抗單粒子、適應(yīng)超高溫和超低溫等方面具有很強(qiáng)的競(jìng)爭(zhēng)力。MCU硬件設(shè)計(jì)主要包括兩大部分:CPU選型和外圍IP核的選取。

3 CPU選型

CPU作為MCU的大腦,起到控制核心的作用,基本上決定了MCU的目標(biāo)應(yīng)用領(lǐng)域,因此CPU的選型是設(shè)計(jì)MCU的關(guān)鍵。目前,可以用于集成電路嵌入式設(shè)計(jì)的CPU主要有CISC架構(gòu)的80386EX,RISC架構(gòu)的ARM7TDMI/EJ、ARM926EJS/946ES/968ES、ARM1136/56/76、ARMCortex-A5/7/8/9/15、ARMCortex-R4/5/7、ARMCortex-M0/0+/1/3/4、SecurCore000/100/300、MIPS32M4K/4K/14K/24K/34K/74K/1004K/1074K、microMIPS32、SmartMIPS、Nios/NiosII、PowerPC40x/60x/70x/90x、SPARCv7/8/9、LEON2/3/4、OR1000/1200等,其中以ARM系列嵌入式CPU發(fā)展的勢(shì)頭最為迅猛,占據(jù)了嵌入式處理器絕大部分的市場(chǎng)份額,而且還在繼續(xù)增長(zhǎng)。各家公司的每種處理器都有自己的特點(diǎn),可以滿足不同的應(yīng)用需求。此外,開發(fā)環(huán)境的完備性、總線接口協(xié)議的高效性、技術(shù)支持的專業(yè)性、IP核種類的豐富性、設(shè)計(jì)資源的開放性以及設(shè)計(jì)者的使用習(xí)慣等,都會(huì)對(duì)CPU的選型產(chǎn)生決定性的影響。

4外圍IP選取

對(duì)于應(yīng)用領(lǐng)域而言,外圍IP核起到了很好的支撐作用,因?yàn)槿绻袽CU比作“人”,則外圍IP核相當(dāng)于MCU的“眼”“耳”“口”“鼻”等重要器官,所以外圍IP核的選取也同樣至關(guān)重要。IP核的選取包括通用IP核和特定用途IP核兩種。

4.1通用IP選取

目前,通用IP核的種類比較繁多,按照總線接口協(xié)議可以分為IBM公司的Core Connect、ARM公司的AMBA(Advanced Microcontroller Bus Architecture)和Silicore Corp公司的Wishbone等;按功能分為接口類IP核如DMA、GPIO、UART、USART、Timer、WDT、I2C、I2S、SPI、CAN、存儲(chǔ)器控制器,圖像處理類IP核等;存儲(chǔ)器類IP核如ROM、RAM、SRAM、FLASH等。根據(jù)功能不同可以進(jìn)行不同的選擇,還可以集成幾個(gè)相同功能的IP核,如UARTx4有4個(gè)UART接口,I2Cx2則是有2個(gè)I2C接口等。

4.2特定用途IP選取

特定功能的IP核種類也很多,如時(shí)鐘類的PLL、片上高精度振蕩器,模數(shù)轉(zhuǎn)換類的AD、DA,網(wǎng)絡(luò)類的ETHERNETMAC/PHY、Modem,圖像處理類的H.264、JPEG,接口類的USB2.0/3.0、IDE、SATA等,高速接口類的LVDS、RapidIO、SerDes等,還有各種傳感器等,需要根據(jù)市場(chǎng)定位來確定。

5 MCU設(shè)計(jì)

5.1硬件設(shè)計(jì)

目前,Samsung、FreeScale、Atmel、NXP、TI、ST等大公司已經(jīng)大規(guī)模推出各類MCU,而且各具特色,因此設(shè)計(jì)具有自主知識(shí)產(chǎn)權(quán)的MCU應(yīng)在系統(tǒng)架構(gòu)等方面有別于這些大公司,一是避免侵權(quán),二是更有利于市場(chǎng)競(jìng)爭(zhēng)。同時(shí)應(yīng)做好產(chǎn)品的規(guī)劃:從簡(jiǎn)單到復(fù)雜,從單一產(chǎn)品到系列產(chǎn)品,設(shè)計(jì)平臺(tái)不斷維護(hù)與更新,設(shè)計(jì)軟件不斷維護(hù)與升級(jí),設(shè)計(jì)人員的水平不斷提高。主要包括以下幾個(gè)方面:

(1)體系架構(gòu)分析、設(shè)計(jì)和驗(yàn)證

依據(jù)設(shè)計(jì)規(guī)格書中的性能指標(biāo)和功能指標(biāo),首先需要制定設(shè)計(jì)方案:選取幾款CPU以及所有用到的IP核進(jìn)行系統(tǒng)級(jí)設(shè)計(jì),從整體上評(píng)估MCU的系統(tǒng)架構(gòu)、CPU的性能指標(biāo)、IP核的功能特性等方面。基于幾種選定的目標(biāo)工藝給出相應(yīng)的數(shù)據(jù)分析,確認(rèn)是否能夠滿足設(shè)計(jì)目標(biāo)的要求,從而確定基本的設(shè)計(jì)方案,然后再根據(jù)具體的設(shè)計(jì)結(jié)果進(jìn)行相應(yīng)的優(yōu)化。

(2)時(shí)鐘和復(fù)位方案設(shè)計(jì)

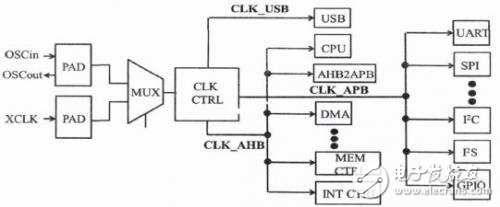

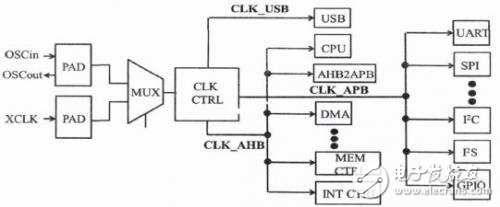

時(shí)鐘和復(fù)位對(duì)整個(gè)電路而言起到了至關(guān)重要的作用。如果這兩路信號(hào)有問題,則電路不能正常工作。因此,需要作出詳盡的時(shí)鐘方案和復(fù)位方案,需要給不同的外設(shè)提供不同的時(shí)鐘:USB單獨(dú)時(shí)鐘、CPU等高速外設(shè)一個(gè)時(shí)鐘、UART等低速外設(shè)一個(gè)時(shí)鐘,如圖1示。

圖1時(shí)鐘方案示意圖

(3)總線方案設(shè)計(jì)

采用何種總線、何種組合方式、總線的數(shù)量等關(guān)系到MCU性能的發(fā)揮。以AMBA總線為例,通常的用法是AHB接高速外設(shè),再通過AHB到APB總線橋來訪問低速外設(shè)。有時(shí)為了提高外設(shè)的訪問速度,一個(gè)MCU內(nèi)部可能有兩條APB總線;也可能有兩條AHB總線。指令和數(shù)據(jù)分離,一條用來數(shù)據(jù)傳輸或圖像處理,另一條用來通用控制。還可能有多層AHB的互連矩陣,便于多個(gè)Master可以同時(shí)訪問多個(gè)不同的高速外設(shè),從而大幅度提高M(jìn)CU系統(tǒng)性能。因此,總線方案的制定須依據(jù)產(chǎn)品的具體應(yīng)用來確定。

(4)功耗管理方案設(shè)計(jì)

低功耗是MCU的突出特點(diǎn)之一,因?yàn)镸CU中集成了多種低功耗管理策略:不僅在邏輯上采用門控時(shí)鐘、門級(jí)優(yōu)化的方式,而且還在物理上采用多閾值電壓、多電源域、門控電源等方式;同時(shí)更在功能模式上采用了多種模式:正常運(yùn)行模式、睡眠模式、深度睡眠模式、掉電模式等,并嚴(yán)格規(guī)定各種模式下運(yùn)行和關(guān)閉IP核的種類以及各種模式之間的進(jìn)入和退出流程。這既保證了電路的功能,又保證了電路的性能。

(5)中斷處理方案設(shè)計(jì)

中斷是MCU一項(xiàng)很重要的功能。通過中斷控制,CPU可以快速響應(yīng)外設(shè)的請(qǐng)求。中斷處理一般包括中斷源的數(shù)量、優(yōu)先級(jí)、是否可屏蔽、是一般中斷還是快速中斷等,通常需要設(shè)計(jì)一個(gè)專用模塊來進(jìn)行中斷處理。有時(shí)為了提高設(shè)計(jì)效率,IP銷售商也提供標(biāo)準(zhǔn)的基于AHB或APB等總線接口協(xié)議的IP核。如果此類IP核能夠滿足系統(tǒng)對(duì)于中斷處理情況的要求,也可以選用。

(6)存儲(chǔ)器管理方案設(shè)計(jì)

存儲(chǔ)器是MCU中占面積較大的模塊。一個(gè)MCU中可能同時(shí)含有ROM、SRAM和FLASH三種存儲(chǔ)器:ROM用于放置Boot Loader、IP Drivers等,SRAM用于提高軟件運(yùn)行速度、存放臨時(shí)數(shù)據(jù),F(xiàn)LASH用于存放應(yīng)用程序和數(shù)據(jù)。由于FLASH的讀寫速度比較慢,為了提高FLASH的讀寫速度,可以采用預(yù)取緩沖器和寫緩沖器來加速指令和數(shù)據(jù)的緩沖。由于各個(gè)存儲(chǔ)器都有自己的地址空間,因此很方便用戶訪問。為了便于系統(tǒng)管理,通常設(shè)計(jì)一個(gè)存儲(chǔ)器管理模塊,并在系統(tǒng)控制模塊中設(shè)計(jì)對(duì)應(yīng)的控制寄存器。

(7)在線調(diào)試方案設(shè)計(jì)

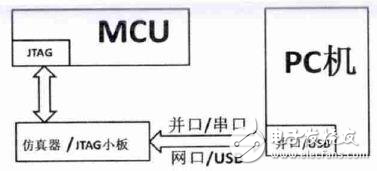

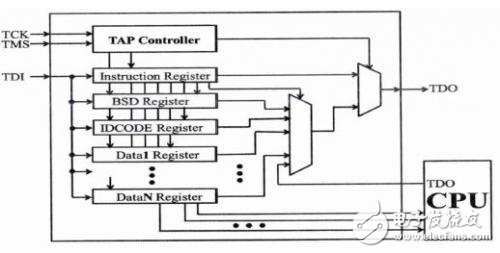

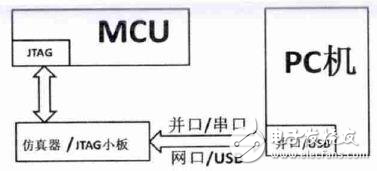

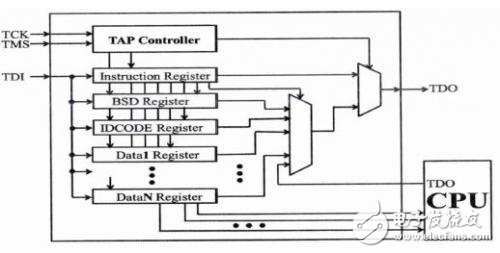

目前,比較常用的在線調(diào)試方式為串行調(diào)試,如JTAG、EJTAG、UART等,使用PC機(jī)的并口、串口、網(wǎng)口或是USB接口,使得在線調(diào)試簡(jiǎn)單方便,成本低廉,如圖2所示。由于被調(diào)試的程序要在目標(biāo)板上運(yùn)行,而且MCU必須正常工作,因此需要設(shè)計(jì)一個(gè)專用的調(diào)試模塊以保證上位機(jī)軟件可以調(diào)用CPU來進(jìn)行軟硬件的在線調(diào)試,并且符合IEEE1149.1的協(xié)議標(biāo)準(zhǔn),此模塊的基本結(jié)構(gòu)如圖3所示。

圖2典型在線調(diào)試系統(tǒng)示意圖

圖3調(diào)試結(jié)構(gòu)示意圖

(8)測(cè)試方案設(shè)計(jì)

MCU的測(cè)試方案主要包括物理測(cè)試、功能測(cè)試和性能測(cè)試幾部分內(nèi)容。先要根據(jù)時(shí)鐘方案和復(fù)位方案對(duì)MCU進(jìn)行時(shí)鐘測(cè)試,確保時(shí)鐘電路工作正常;再對(duì)CPU進(jìn)行功能測(cè)試,因?yàn)镃PU是MCU的控制核心,只有CPU正確運(yùn)行才能對(duì)其他IP核進(jìn)行測(cè)試;然后再依據(jù)設(shè)計(jì)規(guī)格書對(duì)MCU外圍的數(shù)字IP核和模擬IP核進(jìn)行功能測(cè)試和性能測(cè)試。

5.2系統(tǒng)級(jí)驗(yàn)證

為了確保設(shè)計(jì)的正確性,流片之前必須對(duì)MCU進(jìn)行全功能驗(yàn)證。因此需要使用多種IIP和VIP來搭建一個(gè)系統(tǒng)級(jí)驗(yàn)證平臺(tái),依據(jù)設(shè)計(jì)規(guī)格書制定詳細(xì)的驗(yàn)證方案,通過仿真工具,采用定向和隨機(jī)的方式或采用比較流行的OVM、VMM和UVM等驗(yàn)證方法學(xué)、逐個(gè)IP核來驗(yàn)證MCU的全部功能是正確的,重點(diǎn)是系統(tǒng)控制單元、總線仲裁器、功耗管理等為系統(tǒng)功能定制設(shè)計(jì)的非標(biāo)準(zhǔn)模塊。

5.3 FPGA原型驗(yàn)證

由于系統(tǒng)級(jí)驗(yàn)證使用的是EDA工具進(jìn)行軟件仿真,仿真的速度比較慢,因此可以通過FPGA原型驗(yàn)證的方式來加速系統(tǒng)級(jí)驗(yàn)證的速度,尤其是需要將那些功能比較復(fù)雜、規(guī)模比較大的模塊下載到FPGA中,而且應(yīng)盡可能使用規(guī)模比較大的FPGA,如Virtex-7系列、ArriaV系列等。搭建FPGA驗(yàn)證平臺(tái)時(shí),不僅可以使用一塊FPGA,也可以使用多塊FPGA,最好能夠?qū)⒃O(shè)計(jì)的所有模塊全部下載到FPGA中。FPGA原型驗(yàn)證不僅要驗(yàn)證硬件的正確性,還要驗(yàn)證IP核驅(qū)動(dòng)程序的正確性,同時(shí)也可以驗(yàn)證目標(biāo)應(yīng)用程序的正確性。

5.4物理設(shè)計(jì)

在對(duì)MCU系統(tǒng)級(jí)驗(yàn)證和FPGA原型驗(yàn)證后,需要進(jìn)行物理設(shè)計(jì):依據(jù)設(shè)計(jì)規(guī)格書制定合理設(shè)計(jì)約束,從邏輯綜合到自動(dòng)布局布線,再到物理驗(yàn)證、形式驗(yàn)證、靜態(tài)時(shí)序分析和功能驗(yàn)證,完成從RTL到GDSII的轉(zhuǎn)換過程,最后將數(shù)據(jù)發(fā)送至代工廠進(jìn)行加工制造。

5.5文檔設(shè)計(jì)

文檔是MCU設(shè)計(jì)過程中很重要而且很必要的環(huán)節(jié),且應(yīng)該在設(shè)計(jì)的不同階段,以模板的形式規(guī)定在此階段所要完成的文檔設(shè)計(jì),并由項(xiàng)目負(fù)責(zé)人進(jìn)行詳細(xì)審查,從而確保一旦設(shè)計(jì)中出現(xiàn)了任何問題,都可以查找相關(guān)的設(shè)計(jì)文件以及對(duì)應(yīng)的設(shè)計(jì)文檔,尤其是設(shè)計(jì)的細(xì)節(jié)需要體現(xiàn)的很完整。

6結(jié)束語(yǔ)

以上只是簡(jiǎn)要概述了MCU硬件設(shè)計(jì)的主要方面。若要設(shè)計(jì)一個(gè)性價(jià)比高、競(jìng)爭(zhēng)力強(qiáng)的MCU,還需要進(jìn)行大量的、詳細(xì)的工作,尤其是電路的全功能驗(yàn)證和詳盡測(cè)試,并搭建一個(gè)MCU平臺(tái)來進(jìn)行系列產(chǎn)品的開發(fā),以保證產(chǎn)品可以源源不斷地進(jìn)入嵌入式市場(chǎng)。

?

目前,集成電路的嵌入式技術(shù)發(fā)展越來越快,各色嵌入式產(chǎn)品也越來越受歡迎,尤其是以大屏幕多功能的手機(jī)、平板電腦等為典型代表,做為其控制核心的高性能、低功耗的微控制器(MCU)起到了決定性作用。因此以CPU為核心MCU的設(shè)計(jì)也成為了諸多高等院校、各大公司進(jìn)行市場(chǎng)競(jìng)爭(zhēng)的一個(gè)主流發(fā)展方向。

2 MCU選型技術(shù)

微控制器(MCU)的應(yīng)用領(lǐng)域非常廣泛,如消費(fèi)類電子市場(chǎng)中的手機(jī)、照相機(jī)、攝像機(jī)、MP3、MP4、平板電腦、筆記本電腦、PC機(jī)、各種遙控電動(dòng)玩具等,還有汽車電子的電子鑰匙、控制系統(tǒng)、導(dǎo)航、倒車影像、倒車?yán)走_(dá)等,還有各種安全防衛(wèi)系統(tǒng)、醫(yī)療器械、工業(yè)控制、武器裝備、航空航天等各個(gè)領(lǐng)域。因此在設(shè)計(jì)MCU之前需要進(jìn)行明確的市場(chǎng)定位,從而使目標(biāo)產(chǎn)品有的放矢,并在高性能、低成本、多功能、輕體積、低功耗、高可靠、散熱好、抗輻照、抗單粒子、適應(yīng)超高溫和超低溫等方面具有很強(qiáng)的競(jìng)爭(zhēng)力。MCU硬件設(shè)計(jì)主要包括兩大部分:CPU選型和外圍IP核的選取。

3 CPU選型

CPU作為MCU的大腦,起到控制核心的作用,基本上決定了MCU的目標(biāo)應(yīng)用領(lǐng)域,因此CPU的選型是設(shè)計(jì)MCU的關(guān)鍵。目前,可以用于集成電路嵌入式設(shè)計(jì)的CPU主要有CISC架構(gòu)的80386EX,RISC架構(gòu)的ARM7TDMI/EJ、ARM926EJS/946ES/968ES、ARM1136/56/76、ARMCortex-A5/7/8/9/15、ARMCortex-R4/5/7、ARMCortex-M0/0+/1/3/4、SecurCore000/100/300、MIPS32M4K/4K/14K/24K/34K/74K/1004K/1074K、microMIPS32、SmartMIPS、Nios/NiosII、PowerPC40x/60x/70x/90x、SPARCv7/8/9、LEON2/3/4、OR1000/1200等,其中以ARM系列嵌入式CPU發(fā)展的勢(shì)頭最為迅猛,占據(jù)了嵌入式處理器絕大部分的市場(chǎng)份額,而且還在繼續(xù)增長(zhǎng)。各家公司的每種處理器都有自己的特點(diǎn),可以滿足不同的應(yīng)用需求。此外,開發(fā)環(huán)境的完備性、總線接口協(xié)議的高效性、技術(shù)支持的專業(yè)性、IP核種類的豐富性、設(shè)計(jì)資源的開放性以及設(shè)計(jì)者的使用習(xí)慣等,都會(huì)對(duì)CPU的選型產(chǎn)生決定性的影響。

4外圍IP選取

對(duì)于應(yīng)用領(lǐng)域而言,外圍IP核起到了很好的支撐作用,因?yàn)槿绻袽CU比作“人”,則外圍IP核相當(dāng)于MCU的“眼”“耳”“口”“鼻”等重要器官,所以外圍IP核的選取也同樣至關(guān)重要。IP核的選取包括通用IP核和特定用途IP核兩種。

4.1通用IP選取

目前,通用IP核的種類比較繁多,按照總線接口協(xié)議可以分為IBM公司的Core Connect、ARM公司的AMBA(Advanced Microcontroller Bus Architecture)和Silicore Corp公司的Wishbone等;按功能分為接口類IP核如DMA、GPIO、UART、USART、Timer、WDT、I2C、I2S、SPI、CAN、存儲(chǔ)器控制器,圖像處理類IP核等;存儲(chǔ)器類IP核如ROM、RAM、SRAM、FLASH等。根據(jù)功能不同可以進(jìn)行不同的選擇,還可以集成幾個(gè)相同功能的IP核,如UARTx4有4個(gè)UART接口,I2Cx2則是有2個(gè)I2C接口等。

4.2特定用途IP選取

特定功能的IP核種類也很多,如時(shí)鐘類的PLL、片上高精度振蕩器,模數(shù)轉(zhuǎn)換類的AD、DA,網(wǎng)絡(luò)類的ETHERNETMAC/PHY、Modem,圖像處理類的H.264、JPEG,接口類的USB2.0/3.0、IDE、SATA等,高速接口類的LVDS、RapidIO、SerDes等,還有各種傳感器等,需要根據(jù)市場(chǎng)定位來確定。

5 MCU設(shè)計(jì)

5.1硬件設(shè)計(jì)

目前,Samsung、FreeScale、Atmel、NXP、TI、ST等大公司已經(jīng)大規(guī)模推出各類MCU,而且各具特色,因此設(shè)計(jì)具有自主知識(shí)產(chǎn)權(quán)的MCU應(yīng)在系統(tǒng)架構(gòu)等方面有別于這些大公司,一是避免侵權(quán),二是更有利于市場(chǎng)競(jìng)爭(zhēng)。同時(shí)應(yīng)做好產(chǎn)品的規(guī)劃:從簡(jiǎn)單到復(fù)雜,從單一產(chǎn)品到系列產(chǎn)品,設(shè)計(jì)平臺(tái)不斷維護(hù)與更新,設(shè)計(jì)軟件不斷維護(hù)與升級(jí),設(shè)計(jì)人員的水平不斷提高。主要包括以下幾個(gè)方面:

(1)體系架構(gòu)分析、設(shè)計(jì)和驗(yàn)證

依據(jù)設(shè)計(jì)規(guī)格書中的性能指標(biāo)和功能指標(biāo),首先需要制定設(shè)計(jì)方案:選取幾款CPU以及所有用到的IP核進(jìn)行系統(tǒng)級(jí)設(shè)計(jì),從整體上評(píng)估MCU的系統(tǒng)架構(gòu)、CPU的性能指標(biāo)、IP核的功能特性等方面。基于幾種選定的目標(biāo)工藝給出相應(yīng)的數(shù)據(jù)分析,確認(rèn)是否能夠滿足設(shè)計(jì)目標(biāo)的要求,從而確定基本的設(shè)計(jì)方案,然后再根據(jù)具體的設(shè)計(jì)結(jié)果進(jìn)行相應(yīng)的優(yōu)化。

(2)時(shí)鐘和復(fù)位方案設(shè)計(jì)

時(shí)鐘和復(fù)位對(duì)整個(gè)電路而言起到了至關(guān)重要的作用。如果這兩路信號(hào)有問題,則電路不能正常工作。因此,需要作出詳盡的時(shí)鐘方案和復(fù)位方案,需要給不同的外設(shè)提供不同的時(shí)鐘:USB單獨(dú)時(shí)鐘、CPU等高速外設(shè)一個(gè)時(shí)鐘、UART等低速外設(shè)一個(gè)時(shí)鐘,如圖1示。

圖1時(shí)鐘方案示意圖

(3)總線方案設(shè)計(jì)

采用何種總線、何種組合方式、總線的數(shù)量等關(guān)系到MCU性能的發(fā)揮。以AMBA總線為例,通常的用法是AHB接高速外設(shè),再通過AHB到APB總線橋來訪問低速外設(shè)。有時(shí)為了提高外設(shè)的訪問速度,一個(gè)MCU內(nèi)部可能有兩條APB總線;也可能有兩條AHB總線。指令和數(shù)據(jù)分離,一條用來數(shù)據(jù)傳輸或圖像處理,另一條用來通用控制。還可能有多層AHB的互連矩陣,便于多個(gè)Master可以同時(shí)訪問多個(gè)不同的高速外設(shè),從而大幅度提高M(jìn)CU系統(tǒng)性能。因此,總線方案的制定須依據(jù)產(chǎn)品的具體應(yīng)用來確定。

(4)功耗管理方案設(shè)計(jì)

低功耗是MCU的突出特點(diǎn)之一,因?yàn)镸CU中集成了多種低功耗管理策略:不僅在邏輯上采用門控時(shí)鐘、門級(jí)優(yōu)化的方式,而且還在物理上采用多閾值電壓、多電源域、門控電源等方式;同時(shí)更在功能模式上采用了多種模式:正常運(yùn)行模式、睡眠模式、深度睡眠模式、掉電模式等,并嚴(yán)格規(guī)定各種模式下運(yùn)行和關(guān)閉IP核的種類以及各種模式之間的進(jìn)入和退出流程。這既保證了電路的功能,又保證了電路的性能。

(5)中斷處理方案設(shè)計(jì)

中斷是MCU一項(xiàng)很重要的功能。通過中斷控制,CPU可以快速響應(yīng)外設(shè)的請(qǐng)求。中斷處理一般包括中斷源的數(shù)量、優(yōu)先級(jí)、是否可屏蔽、是一般中斷還是快速中斷等,通常需要設(shè)計(jì)一個(gè)專用模塊來進(jìn)行中斷處理。有時(shí)為了提高設(shè)計(jì)效率,IP銷售商也提供標(biāo)準(zhǔn)的基于AHB或APB等總線接口協(xié)議的IP核。如果此類IP核能夠滿足系統(tǒng)對(duì)于中斷處理情況的要求,也可以選用。

(6)存儲(chǔ)器管理方案設(shè)計(jì)

存儲(chǔ)器是MCU中占面積較大的模塊。一個(gè)MCU中可能同時(shí)含有ROM、SRAM和FLASH三種存儲(chǔ)器:ROM用于放置Boot Loader、IP Drivers等,SRAM用于提高軟件運(yùn)行速度、存放臨時(shí)數(shù)據(jù),F(xiàn)LASH用于存放應(yīng)用程序和數(shù)據(jù)。由于FLASH的讀寫速度比較慢,為了提高FLASH的讀寫速度,可以采用預(yù)取緩沖器和寫緩沖器來加速指令和數(shù)據(jù)的緩沖。由于各個(gè)存儲(chǔ)器都有自己的地址空間,因此很方便用戶訪問。為了便于系統(tǒng)管理,通常設(shè)計(jì)一個(gè)存儲(chǔ)器管理模塊,并在系統(tǒng)控制模塊中設(shè)計(jì)對(duì)應(yīng)的控制寄存器。

(7)在線調(diào)試方案設(shè)計(jì)

目前,比較常用的在線調(diào)試方式為串行調(diào)試,如JTAG、EJTAG、UART等,使用PC機(jī)的并口、串口、網(wǎng)口或是USB接口,使得在線調(diào)試簡(jiǎn)單方便,成本低廉,如圖2所示。由于被調(diào)試的程序要在目標(biāo)板上運(yùn)行,而且MCU必須正常工作,因此需要設(shè)計(jì)一個(gè)專用的調(diào)試模塊以保證上位機(jī)軟件可以調(diào)用CPU來進(jìn)行軟硬件的在線調(diào)試,并且符合IEEE1149.1的協(xié)議標(biāo)準(zhǔn),此模塊的基本結(jié)構(gòu)如圖3所示。

圖2典型在線調(diào)試系統(tǒng)示意圖

圖3調(diào)試結(jié)構(gòu)示意圖

(8)測(cè)試方案設(shè)計(jì)

MCU的測(cè)試方案主要包括物理測(cè)試、功能測(cè)試和性能測(cè)試幾部分內(nèi)容。先要根據(jù)時(shí)鐘方案和復(fù)位方案對(duì)MCU進(jìn)行時(shí)鐘測(cè)試,確保時(shí)鐘電路工作正常;再對(duì)CPU進(jìn)行功能測(cè)試,因?yàn)镃PU是MCU的控制核心,只有CPU正確運(yùn)行才能對(duì)其他IP核進(jìn)行測(cè)試;然后再依據(jù)設(shè)計(jì)規(guī)格書對(duì)MCU外圍的數(shù)字IP核和模擬IP核進(jìn)行功能測(cè)試和性能測(cè)試。

5.2系統(tǒng)級(jí)驗(yàn)證

為了確保設(shè)計(jì)的正確性,流片之前必須對(duì)MCU進(jìn)行全功能驗(yàn)證。因此需要使用多種IIP和VIP來搭建一個(gè)系統(tǒng)級(jí)驗(yàn)證平臺(tái),依據(jù)設(shè)計(jì)規(guī)格書制定詳細(xì)的驗(yàn)證方案,通過仿真工具,采用定向和隨機(jī)的方式或采用比較流行的OVM、VMM和UVM等驗(yàn)證方法學(xué)、逐個(gè)IP核來驗(yàn)證MCU的全部功能是正確的,重點(diǎn)是系統(tǒng)控制單元、總線仲裁器、功耗管理等為系統(tǒng)功能定制設(shè)計(jì)的非標(biāo)準(zhǔn)模塊。

5.3 FPGA原型驗(yàn)證

由于系統(tǒng)級(jí)驗(yàn)證使用的是EDA工具進(jìn)行軟件仿真,仿真的速度比較慢,因此可以通過FPGA原型驗(yàn)證的方式來加速系統(tǒng)級(jí)驗(yàn)證的速度,尤其是需要將那些功能比較復(fù)雜、規(guī)模比較大的模塊下載到FPGA中,而且應(yīng)盡可能使用規(guī)模比較大的FPGA,如Virtex-7系列、ArriaV系列等。搭建FPGA驗(yàn)證平臺(tái)時(shí),不僅可以使用一塊FPGA,也可以使用多塊FPGA,最好能夠?qū)⒃O(shè)計(jì)的所有模塊全部下載到FPGA中。FPGA原型驗(yàn)證不僅要驗(yàn)證硬件的正確性,還要驗(yàn)證IP核驅(qū)動(dòng)程序的正確性,同時(shí)也可以驗(yàn)證目標(biāo)應(yīng)用程序的正確性。

5.4物理設(shè)計(jì)

在對(duì)MCU系統(tǒng)級(jí)驗(yàn)證和FPGA原型驗(yàn)證后,需要進(jìn)行物理設(shè)計(jì):依據(jù)設(shè)計(jì)規(guī)格書制定合理設(shè)計(jì)約束,從邏輯綜合到自動(dòng)布局布線,再到物理驗(yàn)證、形式驗(yàn)證、靜態(tài)時(shí)序分析和功能驗(yàn)證,完成從RTL到GDSII的轉(zhuǎn)換過程,最后將數(shù)據(jù)發(fā)送至代工廠進(jìn)行加工制造。

5.5文檔設(shè)計(jì)

文檔是MCU設(shè)計(jì)過程中很重要而且很必要的環(huán)節(jié),且應(yīng)該在設(shè)計(jì)的不同階段,以模板的形式規(guī)定在此階段所要完成的文檔設(shè)計(jì),并由項(xiàng)目負(fù)責(zé)人進(jìn)行詳細(xì)審查,從而確保一旦設(shè)計(jì)中出現(xiàn)了任何問題,都可以查找相關(guān)的設(shè)計(jì)文件以及對(duì)應(yīng)的設(shè)計(jì)文檔,尤其是設(shè)計(jì)的細(xì)節(jié)需要體現(xiàn)的很完整。

6結(jié)束語(yǔ)

以上只是簡(jiǎn)要概述了MCU硬件設(shè)計(jì)的主要方面。若要設(shè)計(jì)一個(gè)性價(jià)比高、競(jìng)爭(zhēng)力強(qiáng)的MCU,還需要進(jìn)行大量的、詳細(xì)的工作,尤其是電路的全功能驗(yàn)證和詳盡測(cè)試,并搭建一個(gè)MCU平臺(tái)來進(jìn)行系列產(chǎn)品的開發(fā),以保證產(chǎn)品可以源源不斷地進(jìn)入嵌入式市場(chǎng)。

?

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 深度學(xué)習(xí)嵌入式系統(tǒng)

- 嵌入式

- 基于dSPACE的嵌入式車輛動(dòng)力學(xué)仿真平臺(tái)開發(fā)的探究

- DSP與MCU在嵌入式系統(tǒng)中的應(yīng)用

- 嵌入式系統(tǒng)是如何組成的

- 嵌入式硬件系統(tǒng)教程之嵌入式存儲(chǔ)技術(shù)的詳細(xì)資料說明 14次下載

- 學(xué)習(xí)嵌入式系統(tǒng)有哪些方向?

- 嵌入式系統(tǒng)教程之嵌入式硬件系統(tǒng)設(shè)計(jì)與應(yīng)用實(shí)例資料免費(fèi)下載 54次下載

- 嵌入式系統(tǒng)硬件可靠性分析 1次下載

- 嵌入式硬件設(shè)計(jì)資料 49次下載

- 嵌入式硬件 Jack Ganssle 83次下載

- 嵌入式硬件系統(tǒng)設(shè)計(jì)與開發(fā)實(shí)例詳解 12次下載

- 嵌入式硬件設(shè)計(jì)

- 32位ARM7嵌入式硬件平臺(tái)簡(jiǎn)介

- 嵌入式系統(tǒng)USB接口的研究及設(shè)計(jì)

- 嵌入式硬件電路設(shè)計(jì)必須掌握的6大基本功 1114次閱讀

- 嵌入式硬件設(shè)計(jì)中需要注意的事項(xiàng) 826次閱讀

- 什么是嵌入式技術(shù) 1w次閱讀

- 淺談嵌入式MCU的中斷處理 8872次閱讀

- 設(shè)計(jì)嵌入式系統(tǒng)硬件電路時(shí)需要考慮哪些問題 3896次閱讀

- 嵌入式硬件電路設(shè)計(jì)中的六大要點(diǎn) 4640次閱讀

- 基于SoPC的嵌入式硬件平臺(tái)系統(tǒng)設(shè)計(jì)詳解 1893次閱讀

- 淺析嵌入式MCU硬件設(shè)計(jì)方案 4671次閱讀

- 淺談嵌入式硬件設(shè)計(jì)大神與小白的區(qū)別 1.2w次閱讀

- ARM嵌入式系統(tǒng)硬件設(shè)計(jì)及應(yīng)用實(shí)例詳解 1w次閱讀

- 嵌入式軟件工程師和嵌入式硬件工程師有什么區(qū)別 7w次閱讀

- 嵌入式硬件電路設(shè)計(jì)基礎(chǔ)知識(shí)梳理 1.1w次閱讀

- mcu和電源的選擇讓您的嵌入式電路設(shè)計(jì)更高效 5291次閱讀

- 嵌入式硬件電路設(shè)計(jì)的六個(gè)基礎(chǔ)知識(shí) 1810次閱讀

- 嵌入式硬件電路設(shè)計(jì)六大基本功,你都掌握了嗎? 5218次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費(fèi)下載

- 0.00 MB | 1491次下載 | 免費(fèi)

- 2單片機(jī)典型實(shí)例介紹

- 18.19 MB | 95次下載 | 1 積分

- 3S7-200PLC編程實(shí)例詳細(xì)資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識(shí)別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關(guān)電源原理及各功能電路詳解

- 0.38 MB | 11次下載 | 免費(fèi)

- 6100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 7基于單片機(jī)和 SG3525的程控開關(guān)電源設(shè)計(jì)

- 0.23 MB | 4次下載 | 免費(fèi)

- 8基于AT89C2051/4051單片機(jī)編程器的實(shí)驗(yàn)

- 0.11 MB | 4次下載 | 免費(fèi)

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費(fèi)

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費(fèi)

- 4LabView 8.0 專業(yè)版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費(fèi)

- 5555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33562次下載 | 免費(fèi)

- 6接口電路圖大全

- 未知 | 30320次下載 | 免費(fèi)

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費(fèi)

- 8開關(guān)電源設(shè)計(jì)實(shí)例指南

- 未知 | 21539次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費(fèi)

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537793次下載 | 免費(fèi)

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費(fèi)

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費(fèi)

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費(fèi)

- 6電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191183次下載 | 免費(fèi)

- 7十天學(xué)會(huì)AVR單片機(jī)與C語(yǔ)言視頻教程 下載

- 158M | 183277次下載 | 免費(fèi)

- 8proe5.0野火版下載(中文版免費(fèi)下載)

- 未知 | 138039次下載 | 免費(fèi)

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評(píng)論