資料介紹

隨著雷達數據處理技術的快速發展,需要高速采集雷達回波信號。然而激光雷達的發射波及回波信號經光電器件轉換后,形成的電信號脈寬窄,幅度低,而且背景噪聲大,如采用低速的數據采集系統進行采集,存在數據精度不高等問題。同時,為避免數據傳輸不及時,發生數據丟失,影響系統的可靠性和實時性,需設計開發高速數據采集系統。

設計中針對前端輸出約-25~25 mV,帶寬為20 MHz的信號,采用高帶寬,低噪聲,高數據傳輸率,高分辨率數模轉換芯片AD9235;利用XC2V250內部的大小為6 KB的異步FIFO實現AD9235轉換器與TMS320C6201間的高速數據傳輸。采集系統的采樣率為30 MHz,分辨率為12位,內部異步緩存FIFO為6 KB,滿足高速數據采集要求。

1 系統設計

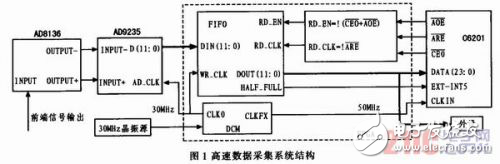

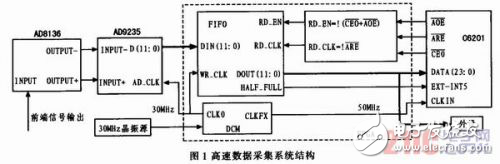

如果A/D直接與DSP的外部存儲接口EMIF連接,會使DSP的負荷過重,另一方面DSP還需擴展外設,與采樣輸入共用一條外部總線,進行外部設備的讀寫,不允許數據采集始終占用外部總線。如果不能及時接收數據,上次存儲的數據會被覆蓋,造成數據丟失。異步FIFO能實現不同時鐘域的數據傳輸,可將它作為A/D轉換器和EMIF之間的橋梁,每寫入一塊數據,便通知EMIF從FIFO取走數據。基于以上分析,圖1為高速數據采集系統結構框圖。

FPGA內部DCM為A/D轉換器和DSP提供采樣時鐘和外部振蕩源,A/D轉換器與DSP工作在不同時鐘,在FPGA內部生成一個異步FIFO作為數據傳輸緩存。A/D轉換器把采樣值寫入FIFO,FIFO寫使能WR_EN一直有效,系統上電后,A/D轉換器一直處于工作狀態,每寫入一塊數據便向DSP發出中斷信號,在中斷中讀取FIFO中的數據。FIFO輸入數據寬度12位,輸出數據寬度為24位,FIFO讀時鐘高于寫時鐘,DSP讀取數據比A/D向FIFO寫數據快,而且DSP內部數據處理時間較快,可保證系統高速實時采集。

2 A/D轉換電路

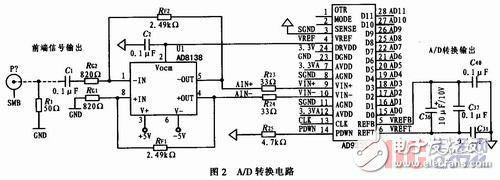

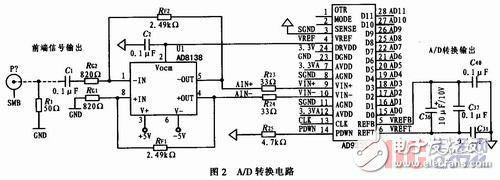

A/D轉換電路是整個系統的重要組成部分。對前端輸出約-25~25 mV,帶寬為20 MHz的射頻信號數字化,設計采用模數轉換器芯片AD9235,最大采樣率40 Mb/s,12 bit數據輸出,信噪比RSN=70 dB。AD9235是差分輸入,單端信號輸入需要A/D驅動芯片,選用低失真差分A/D驅動芯片AD8138,圖2為A/D轉換電路,AD9235模擬輸入設置在2VPP,參考電壓VREF采用內部1 V參考電壓,同時還作為驅動芯片AD8138的共模電壓。利用AD8138對輸入信號進行放大,放大倍數RF/RG=2.49 kΩ/820 Ω≈3。因此,經過AD8138單端差分轉換及放大輸入信號范圍為25~175 mV。

3 FPGA接口設計

3.1 時鐘設計

采用30 MHz外部晶振作為整個系統的時鐘源,利用XCV250內部的時鐘管理器DCM,分別為AD9235、異步FIFO、TMS320C6201提供時鐘源。 DCM輸出CLK0的30 MHz時鐘作為AD9235采樣時鐘和異步FIFO的寫周期WR_CLK。

利用DCM數字頻率合成器輸出CLKFX作為TMS320C6201的時鐘源。公式:DCM輸出CLKFX的頻率=輸入時鐘CLKIN的頻率×(M/D),取M/D=5/3。這樣DCM為TMS320C6201提供50 MHz時鐘,經過4倍頻,DSP系統時鐘為200 MHz,外部存儲EMIF時鐘CLKOUT1為200 MHz。設置CE0空間控制寄存器的參數,使FIFO讀時序SETUP、HOLD等于一個CLKOUT1周期,STROPE等于兩個CLKOUT1周期,讀時序如圖3所示,讀第一個數時,EMIF會自動維護最小2個時鐘周期的建立時間,后續數據讀取,建立時間為1個時鐘周期。FIFO讀時鐘周期約為50 MHz,比A/D向FIFO寫數據時間快,保證系統實時采集。

設計中針對前端輸出約-25~25 mV,帶寬為20 MHz的信號,采用高帶寬,低噪聲,高數據傳輸率,高分辨率數模轉換芯片AD9235;利用XC2V250內部的大小為6 KB的異步FIFO實現AD9235轉換器與TMS320C6201間的高速數據傳輸。采集系統的采樣率為30 MHz,分辨率為12位,內部異步緩存FIFO為6 KB,滿足高速數據采集要求。

1 系統設計

如果A/D直接與DSP的外部存儲接口EMIF連接,會使DSP的負荷過重,另一方面DSP還需擴展外設,與采樣輸入共用一條外部總線,進行外部設備的讀寫,不允許數據采集始終占用外部總線。如果不能及時接收數據,上次存儲的數據會被覆蓋,造成數據丟失。異步FIFO能實現不同時鐘域的數據傳輸,可將它作為A/D轉換器和EMIF之間的橋梁,每寫入一塊數據,便通知EMIF從FIFO取走數據。基于以上分析,圖1為高速數據采集系統結構框圖。

FPGA內部DCM為A/D轉換器和DSP提供采樣時鐘和外部振蕩源,A/D轉換器與DSP工作在不同時鐘,在FPGA內部生成一個異步FIFO作為數據傳輸緩存。A/D轉換器把采樣值寫入FIFO,FIFO寫使能WR_EN一直有效,系統上電后,A/D轉換器一直處于工作狀態,每寫入一塊數據便向DSP發出中斷信號,在中斷中讀取FIFO中的數據。FIFO輸入數據寬度12位,輸出數據寬度為24位,FIFO讀時鐘高于寫時鐘,DSP讀取數據比A/D向FIFO寫數據快,而且DSP內部數據處理時間較快,可保證系統高速實時采集。

2 A/D轉換電路

A/D轉換電路是整個系統的重要組成部分。對前端輸出約-25~25 mV,帶寬為20 MHz的射頻信號數字化,設計采用模數轉換器芯片AD9235,最大采樣率40 Mb/s,12 bit數據輸出,信噪比RSN=70 dB。AD9235是差分輸入,單端信號輸入需要A/D驅動芯片,選用低失真差分A/D驅動芯片AD8138,圖2為A/D轉換電路,AD9235模擬輸入設置在2VPP,參考電壓VREF采用內部1 V參考電壓,同時還作為驅動芯片AD8138的共模電壓。利用AD8138對輸入信號進行放大,放大倍數RF/RG=2.49 kΩ/820 Ω≈3。因此,經過AD8138單端差分轉換及放大輸入信號范圍為25~175 mV。

3 FPGA接口設計

3.1 時鐘設計

采用30 MHz外部晶振作為整個系統的時鐘源,利用XCV250內部的時鐘管理器DCM,分別為AD9235、異步FIFO、TMS320C6201提供時鐘源。 DCM輸出CLK0的30 MHz時鐘作為AD9235采樣時鐘和異步FIFO的寫周期WR_CLK。

利用DCM數字頻率合成器輸出CLKFX作為TMS320C6201的時鐘源。公式:DCM輸出CLKFX的頻率=輸入時鐘CLKIN的頻率×(M/D),取M/D=5/3。這樣DCM為TMS320C6201提供50 MHz時鐘,經過4倍頻,DSP系統時鐘為200 MHz,外部存儲EMIF時鐘CLKOUT1為200 MHz。設置CE0空間控制寄存器的參數,使FIFO讀時序SETUP、HOLD等于一個CLKOUT1周期,STROPE等于兩個CLKOUT1周期,讀時序如圖3所示,讀第一個數時,EMIF會自動維護最小2個時鐘周期的建立時間,后續數據讀取,建立時間為1個時鐘周期。FIFO讀時鐘周期約為50 MHz,比A/D向FIFO寫數據時間快,保證系統實時采集。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 基于PIC总线的高速数据采集系统13次下载

- 使用PCI总线设计高速数据采集系统的资料说明4次下载

- 如何使用FPGA进行高速雷达数据采集系统的设计概述21次下载

- 基于FPGA的高速多路数据采集系统的设计方案详细资料说明14次下载

- DSP和USB的高速数据采集与处理系统设计方案16次下载

- DSP和ADS8364的高速数据采集处理系统设计方案解析0次下载

- 基于FPGA高速数据采集的解决方案13次下载

- 高速数据采集与存储系统技术方案69次下载

- 基于USB-6281的高速数据采集系统的设计30次下载

- 高速数据采集系统中精确时标的cpld实现方法19次下载

- 基于PCI-1716的高速数据采集系统设计61次下载

- 高速数据采集系统的设计22次下载

- 基于PCI总线的高速数据采集卡系统设计与实现55次下载

- 基于PCI-1714的高速数据采集系统方案设计31次下载

- 基于DSP的高速数据采集与处理系统17次下载

- 康谋应用 | 基于多传感器融合的海洋数据采集系统480次阅读

- 高精度数据采集系统设计方案2912次阅读

- 基于USB接口的数据采集系统总体结构解析2951次阅读

- 基于FPGA的DMA方式高速实时数据采集系统设计方案2821次阅读

- 基于ARM7 LPC2220的嵌入式高速数据采集系统1997次阅读

- 基于SOPC技术实现雷达数据采集和图像大屏幕显示5568次阅读

- 基于TLC549的数据采集系统设计7071次阅读

- 利用AD574A设计基于FPGA的高速数据采集系统8636次阅读

- 高速高精度的数据采集系统的设计与实现4715次阅读

- 高速USB数据采集系统方案设计2480次阅读

- 一种高速图像数据采集板的设计方案2304次阅读

- 一种高速实时数据采集系统的设计方案5052次阅读

- 基于PCI总线的微弱信号采集模块的设计方案2053次阅读

- 基于单片机的PSD数据采集电路的设计方案10754次阅读

- 基于CPLD的高速数据采集系统的实现1778次阅读

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費下載

- 0.00 MB | 1491次下載 | 免費

- 2單片機典型實例介紹

- 18.19 MB | 95次下載 | 1 積分

- 3S7-200PLC編程實例詳細資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關電源原理及各功能電路詳解

- 0.38 MB | 11次下載 | 免費

- 6100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 7基于單片機和 SG3525的程控開關電源設計

- 0.23 MB | 4次下載 | 免費

- 8基于AT89C2051/4051單片機編程器的實驗

- 0.11 MB | 4次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費

- 4LabView 8.0 專業版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費

- 5555集成電路應用800例(新編版)

- 0.00 MB | 33562次下載 | 免費

- 6接口電路圖大全

- 未知 | 30320次下載 | 免費

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費

- 8開關電源設計實例指南

- 未知 | 21539次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537793次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191183次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183277次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138039次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論