資料介紹

電子產品中數字信號處理(DSP)芯片的使用率正急劇增加。現場可編程門陣列(FPGA)可支持數百萬個門,并以DSP為中心,這種特性使其性能比標準的DSP芯片有了大幅提升。此外,FPGA還可進行中小型批量生產,能支持非常強大的原型設計與驗證技術,以實現DSP算法的實時仿真。但為FPGA和ASIC創建可移植性算法IP也面臨著諸多挑戰與要求。

本文將介紹如何通過ESL綜合技術大幅縮短在FPGA或ASIC上實現算法所需的時間,并簡化相關工作。

FPGA和ASIC之間RTL移植所面臨的挑戰

盡管RTL支持邏輯級的移植性,但卻不支持架構層移植。如果將同一RTL在不同的目標器件上實現,會導致結果不夠理想;在不同目標器件中,綜合結果可能在功能上正確,但卻根本沒有優化。

如何選擇算法架構取決于一個基本問題,即滿足算法的采樣率和吞吐能力要求,需要進行多少流水線、并行和串行優化處理。此外,FIR、FFT、正弦、余弦、除法等基本的DSP功能根據目標技術的不同,有著不同的優化實現要求。比如,FIR濾波器的直接形式與轉置形式(transposed form)就是一個很好的例子,一種適用于特定的FPGA器件,而另一種則更適用于ASIC技術。

根據FPGA和ASIC的不同要求,我們往往需要不同的架構。眾所周知,FPGA器件傾向于以寄存器為中心,而許多ASIC到FPGA移植指南也建議增加流水線設計,對所有端口進行寄存,并將組合邏輯分解為較小的部分。這樣的設計在ASIC上實現就會增加面積,但這是滿足FPGA時序要求所必需的。

如果以ASIC為目標,我們往往需要完全相反的做法。這時我們建議將寄存器最小化,以盡可能減小占用面積與功耗。我們可以采用時分復用和資源共享的辦法來提高時鐘速度,從而最小化乘法器及其他浪費資源的操作。消費類及無線產品市場領域中的近期設計趨勢就是仔細平衡上述做法的結果。

ASIC RTL和FPGA RTL之間不可避免的差別之一在于存儲器的使用。就FPGA而言,器件內置了標準存儲器。根據FPGA工具流程和廠商的不同,我們需要特定的編碼風格來描述存儲陣列和存儲器。高質量FPGA綜合工具會自動將RTL代碼映射到存儲器上實現。不過,在ASIC領域中,IP和制造庫廠商(fab library vendor)的存儲器選項多種多樣,用戶要根據具體的配置選擇和編輯存儲器,并在RTL設計中進行例化。

許多文章和資料都介紹了在 FPGA 和 ASIC 之間轉移 IP 的編碼風格及移植技術問題。在不同器件類型之間移植實施方案,需要進行大量的編碼與驗證工作,并擁有精湛的的專業技術。

如果首先用FPGA進行原型設計,再移植為ASIC設計,那么還要面臨更多的挑戰。在需要實時刺激和實際速度驗證的情況下,就會出現上述問題。為了滿足上述要求,我們應當保證仿真模型之間的位和采樣準確度,特別是FPGA實現和ASIC模型不能出問題。這要求我們做大量工作,尤其是實現方案不同或經常變化時更應如此。此外,我們還必須手動修改、比較和調試測試工具。

ESL 綜合解決方案

ESL 綜合解決方案能提供強大的性,有助于解決上述諸多問題。

● 使用電子系統層級 (ESL) 模型,支持高級架構與硬件抽象;

● 根據用戶定義的采樣率進行自動優化;

● 用戶選擇目標技術;

● 為多速率設計提供原生支持。

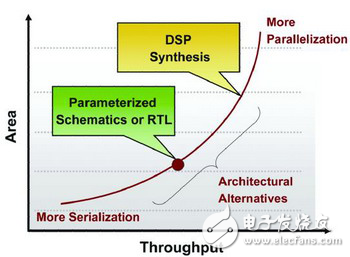

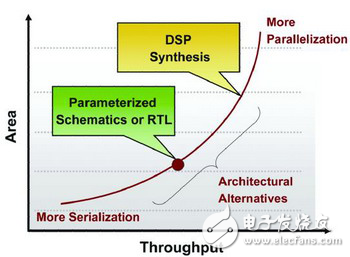

圖1 從統一 ESL 模型快速實現設計方案

利用上述特性,DSP 綜合引擎可根據用戶定義的約束條件在了解目標的基礎上進行整個系統優化,對不同的 RTL進行綜合。這些為優化架構和特定編碼風格而定的RTL 隨后可進入標準化的邏輯綜合流程。

利用ESL綜合技術,我們可以在一個高度抽象的層面完成設計工作,這不僅提高了可移植性,縮短了開發時間,而且還提高了工程設計的工作效率。除了保持RTL級的IP之外,我們還能在算法模型層保持IP,從而提高可移植性以及算法開發人員的工作效率。

如圖1所示,DSP綜合技術使用戶能通過統一的算法模型快速生成并實現多種不同實施方案。FPGA可使用完全并行的流水線架構,也可像ASIC一樣采用占用面積更小的串聯架構。此外,不同實施方案能自動保持位和采樣的準確度,并通過標準化的RTL仿真工具實現完整的驗證路徑。與此形成對比的是,參數化的原理圖輸入法,和那些需要用戶在了解面積、延遲特性之前就確定具體架構的RTL方法,其移植到新的實施目標時往往需要進行大量的修改。

本文將介紹如何通過ESL綜合技術大幅縮短在FPGA或ASIC上實現算法所需的時間,并簡化相關工作。

FPGA和ASIC之間RTL移植所面臨的挑戰

盡管RTL支持邏輯級的移植性,但卻不支持架構層移植。如果將同一RTL在不同的目標器件上實現,會導致結果不夠理想;在不同目標器件中,綜合結果可能在功能上正確,但卻根本沒有優化。

如何選擇算法架構取決于一個基本問題,即滿足算法的采樣率和吞吐能力要求,需要進行多少流水線、并行和串行優化處理。此外,FIR、FFT、正弦、余弦、除法等基本的DSP功能根據目標技術的不同,有著不同的優化實現要求。比如,FIR濾波器的直接形式與轉置形式(transposed form)就是一個很好的例子,一種適用于特定的FPGA器件,而另一種則更適用于ASIC技術。

根據FPGA和ASIC的不同要求,我們往往需要不同的架構。眾所周知,FPGA器件傾向于以寄存器為中心,而許多ASIC到FPGA移植指南也建議增加流水線設計,對所有端口進行寄存,并將組合邏輯分解為較小的部分。這樣的設計在ASIC上實現就會增加面積,但這是滿足FPGA時序要求所必需的。

如果以ASIC為目標,我們往往需要完全相反的做法。這時我們建議將寄存器最小化,以盡可能減小占用面積與功耗。我們可以采用時分復用和資源共享的辦法來提高時鐘速度,從而最小化乘法器及其他浪費資源的操作。消費類及無線產品市場領域中的近期設計趨勢就是仔細平衡上述做法的結果。

ASIC RTL和FPGA RTL之間不可避免的差別之一在于存儲器的使用。就FPGA而言,器件內置了標準存儲器。根據FPGA工具流程和廠商的不同,我們需要特定的編碼風格來描述存儲陣列和存儲器。高質量FPGA綜合工具會自動將RTL代碼映射到存儲器上實現。不過,在ASIC領域中,IP和制造庫廠商(fab library vendor)的存儲器選項多種多樣,用戶要根據具體的配置選擇和編輯存儲器,并在RTL設計中進行例化。

許多文章和資料都介紹了在 FPGA 和 ASIC 之間轉移 IP 的編碼風格及移植技術問題。在不同器件類型之間移植實施方案,需要進行大量的編碼與驗證工作,并擁有精湛的的專業技術。

如果首先用FPGA進行原型設計,再移植為ASIC設計,那么還要面臨更多的挑戰。在需要實時刺激和實際速度驗證的情況下,就會出現上述問題。為了滿足上述要求,我們應當保證仿真模型之間的位和采樣準確度,特別是FPGA實現和ASIC模型不能出問題。這要求我們做大量工作,尤其是實現方案不同或經常變化時更應如此。此外,我們還必須手動修改、比較和調試測試工具。

ESL 綜合解決方案

ESL 綜合解決方案能提供強大的性,有助于解決上述諸多問題。

● 使用電子系統層級 (ESL) 模型,支持高級架構與硬件抽象;

● 根據用戶定義的采樣率進行自動優化;

● 用戶選擇目標技術;

● 為多速率設計提供原生支持。

圖1 從統一 ESL 模型快速實現設計方案

利用上述特性,DSP 綜合引擎可根據用戶定義的約束條件在了解目標的基礎上進行整個系統優化,對不同的 RTL進行綜合。這些為優化架構和特定編碼風格而定的RTL 隨后可進入標準化的邏輯綜合流程。

利用ESL綜合技術,我們可以在一個高度抽象的層面完成設計工作,這不僅提高了可移植性,縮短了開發時間,而且還提高了工程設計的工作效率。除了保持RTL級的IP之外,我們還能在算法模型層保持IP,從而提高可移植性以及算法開發人員的工作效率。

如圖1所示,DSP綜合技術使用戶能通過統一的算法模型快速生成并實現多種不同實施方案。FPGA可使用完全并行的流水線架構,也可像ASIC一樣采用占用面積更小的串聯架構。此外,不同實施方案能自動保持位和采樣的準確度,并通過標準化的RTL仿真工具實現完整的驗證路徑。與此形成對比的是,參數化的原理圖輸入法,和那些需要用戶在了解面積、延遲特性之前就確定具體架構的RTL方法,其移植到新的實施目標時往往需要進行大量的修改。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 綜合能源解決方案(空調+儲能)

- 基于DSP的開關功率放大器控制方案 17次下載

- 如何提高WINCC組態的效率 41次下載

- 手機電源管理設計系統方案的綜合考慮資料下載

- 終端區管制運行效率的集成綜合評估模型 5次下載

- ESR,ESL,如何影響電容?資料下載

- 集成音頻放大器DSP如何提高音頻放大器的效率

- 如何提高功率因數校正的效率從待機到滿負荷的詳細解決方案概述 9次下載

- 便攜式DSP解決方案中不同電源的比較 9次下載

- 用于電話和數據傳真調制解調器的DSP的解決方案增強技術的功能的概述 2次下載

- 基于DSP的電源解決方案 1次下載

- TI手提超聲系統DSP解決方案 8次下載

- TI DSP行業應用解決方案 59次下載

- 基于GPS/GPRS網絡的綜合物流調度管理應用方案

- 基于ESL方法的DSP微處理器行為模型設計

- 高效率、易管理的智能照明解決方案 934次閱讀

- 反饋電路提高了升壓轉換器電流源的效率 573次閱讀

- LFPAK88是提高效率的捷徑 678次閱讀

- 智能電路提高電荷泵和線性穩壓器解決方案的效率 1183次閱讀

- 如何使用SBR提高電源轉換效率 2989次閱讀

- 如何通過提高效率來提高CATV放大器的下行帶寬和上行容量 2389次閱讀

- 綜合電源解決方案TPS84621RUQ的性能特性及應用 2564次閱讀

- 如何才能提高隔離式電源的效率 1172次閱讀

- 實現ARM和DSP或協處理器的通信和協同工作,有什么解決方案和實現指南 1546次閱讀

- 關于多電壓軌FPGA和DSP應用的電源解決方案全解 1091次閱讀

- 教你如何提高LED的發光效率 2.5w次閱讀

- 滿足多種需求的DSP架構解決方案 2269次閱讀

- 一種用AD7858提高DSP采樣精度的新方法 1705次閱讀

- 一種基于DSP的視頻監控系統解決方案 3360次閱讀

- 基于現代DSP技術的QPSK調制器的設計 2154次閱讀

下載排行

本周

- 1開關電源設計原理手冊

- 1.83 MB | 4次下載 | 免費

- 2PL4807單節鋰離子電池充電器中文手冊

- 1.36 MB | 2次下載 | 免費

- 3智能小車proteus仿真+C源程序

- 0.02 MB | 1次下載 | 免費

- 4TMR技術在電流傳感器中的應用

- 616.47 KB | 1次下載 | 免費

- 5BQ769142技術參考手冊

- 2.99MB | 1次下載 | 免費

- 6CBM8605_8606_8608-運算放大器【中文排版】-202406271735

- 2.70 MB | 1次下載 | 免費

- 701-07-06-CBM8655_CBM8656精密運算放大器

- 4.49 MB | 1次下載 | 免費

- 8LLC 電路基本原理分析及公式推導

- 551.94 KB | 1次下載 | 免費

本月

- 1XL4015+LM358恒壓恒流電路圖

- 0.38 MB | 155次下載 | 1 積分

- 2PCB布線和布局電路設計規則

- 0.40 MB | 45次下載 | 免費

- 3GB/T4706.1-2024 家用和類似用途電器的安全第1部分:通用要求

- 7.43 MB | 14次下載 | 1 積分

- 4智能門鎖原理圖

- 0.39 MB | 13次下載 | 免費

- 5JESD79-5C_v1.30-2024 內存技術規范

- 2.71 MB | 10次下載 | 免費

- 6elmo直線電機驅動調試細則

- 4.76 MB | 9次下載 | 6 積分

- 7WIFI智能音箱原理圖完整版

- 0.09 MB | 7次下載 | 10 積分

- 8PC1013三合一快充數據線充電芯片介紹

- 1.03 MB | 7次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935115次下載 | 10 積分

- 2開源硬件-PMP21529.1-4 開關降壓/升壓雙向直流/直流轉換器 PCB layout 設計

- 1.48MB | 420061次下載 | 10 積分

- 3Altium DXP2002下載入口

- 未知 | 233084次下載 | 10 積分

- 4電路仿真軟件multisim 10.0免費下載

- 340992 | 191367次下載 | 10 積分

- 5十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183333次下載 | 10 積分

- 6labview8.5下載

- 未知 | 81581次下載 | 10 積分

- 7Keil工具MDK-Arm免費下載

- 0.02 MB | 73806次下載 | 10 積分

- 8LabVIEW 8.6下載

- 未知 | 65985次下載 | 10 積分

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論