資料介紹

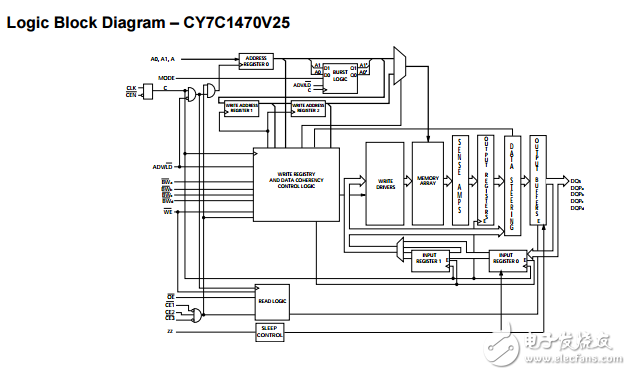

The CY7C1470V25/CY7C1472V25/CY7C1474V25 are 2.5 V, 2M × 36/4M × 18/1M × 72 synchronous pipelined burst SRAMs with No Bus Latency? (NoBL?? logic, respectively. They are designed to support unlimited true back-to-back read/write operations with no wait states. The CY7C1470V25/CY7C1472V25/CY7C1474V25 are equipped with the advanced (NoBL) logic required to enable consecutive read/write operations with data being transferred on every clock cycle. This feature dramatically improves the throughput of data in systems that require frequent write/read transitions. The CY7C1470V25/CY7C1472V25/CY7C1474V25 are pin-compatible and functionally equivalent to ZBT devices. All synchronous inputs pass through input registers controlled by the rising edge of the clock. All data outputs pass through output registers controlled by the rising edge of the clock. The clock input is qualified by the clock enable (CEN) signal, which when deasserted suspends operation and extends the previous clock cycle. Write operations are controlled by the Byte Write Selects (BWa–BWh for CY7C1474V25, BWa–BWd for CY7C1470V25 and BWa–BWb for CY7C1472V25) and a write enable (WE) input. All writes are conducted with on-chip synchronous self-timed write circuitry. Three synchronous chip enables (CE1, CE2, CE3) and an asynchronous output enable (OE) provide for easy bank selection and output tri-state control. In order to avoid bus contention, the output drivers are synchronously tri-stated during the data portion of a write sequence. For a complete list of related documentation, click here.

- 12bit200MSPS時間交織流水線ADC研究與設(shè)計

- 18兆位DCD同步SRAM的流水線cy7c1386d 4次下載

- cy7c1354c 9-mbit流水線結(jié)構(gòu)的SRAM?諾伯 4次下載

- cy7c1353g 4兆位(256K SRAM×18)流過諾博?架構(gòu) 3次下載

- CY7C1350G 4兆位流水線結(jié)構(gòu)的SRAM?諾伯 2次下載

- cy7c1370dv25/cy7c1372dv25,18-mbit 流水線SRAM 諾博(TM)體系結(jié)構(gòu) 4次下載

- cy7c1347g 4兆位(128K的×36)流水線同步SRAM 6次下載

- cy7c1360c 9-mbit流水線SRAM 14次下載

- cy7c1460av33/cy7c1462av33,36-mbit流水線SRAM諾博(TM)體系結(jié)構(gòu) 5次下載

- CY7C1380D-167AXC,18兆位(512K的×36/1M×18)流水線SRAM 2次下載

- cy7c1440av33,36-mbit(1M×36)流水線同步SRAM 6次下載

- 72兆位流水線結(jié)構(gòu)的SRAM?諾伯CY7C1470V33-167AXI 12次下載

- 流水線狀態(tài)機20進(jìn)制,101序列檢測,8位加法器流水線的程序 0次下載

- 一種改進(jìn)運放共享結(jié)構(gòu)的11位流水線ADC設(shè)計 3次下載

- 周期精確的流水線仿真模型

- 新版本Jenkins推薦使用聲明式流水線 603次閱讀

- Google GPipe為代表的流水線并行范式 890次閱讀

- 如何通過Vivado Synthesis中的URAM矩陣自動流水線化來實現(xiàn)最佳時序性能 1436次閱讀

- 一個典型的流水線設(shè)計 1093次閱讀

- 報文解析規(guī)則定義 流水線劃分提取方案 809次閱讀

- 采用28納米CMOS技術(shù)的12-b 10-GS/s交錯式流水線ADC 2095次閱讀

- CPU流水線優(yōu)缺點 3908次閱讀

- 一文詳細(xì)了解流水線設(shè)計 4608次閱讀

- FPGA中流水線的原因和方式 5707次閱讀

- 通過并行流水線結(jié)構(gòu)實現(xiàn)直接型FIR濾波器的系統(tǒng)設(shè)計方案 3319次閱讀

- 流水線設(shè)計的思想介紹與設(shè)計實例 7896次閱讀

- OYES 200系列PLC在瓶裝流水線中的應(yīng)用 1215次閱讀

- 淺談GPU的渲染流水線實現(xiàn) 3757次閱讀

- 一文讀懂處理器流水線 2.2w次閱讀

- 新型流水線實現(xiàn)高速低功耗ADC的原理及方法 4426次閱讀

下載排行

本周

- 1TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 2開關(guān)電源基礎(chǔ)知識

- 5.73 MB | 6次下載 | 免費

- 3100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 4嵌入式linux-聊天程序設(shè)計

- 0.60 MB | 3次下載 | 免費

- 5基于FPGA的光纖通信系統(tǒng)的設(shè)計與實現(xiàn)

- 0.61 MB | 2次下載 | 免費

- 651單片機窗簾控制器仿真程序

- 1.93 MB | 2次下載 | 免費

- 751單片機大棚環(huán)境控制器仿真程序

- 1.10 MB | 2次下載 | 免費

- 8基于51單片機的RGB調(diào)色燈程序仿真

- 0.86 MB | 2次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33564次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關(guān)電源設(shè)計實例指南

- 未知 | 21549次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數(shù)字電路基礎(chǔ)pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅(qū)動電路設(shè)計》 溫德爾著

- 0.00 MB | 6653次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537796次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191185次下載 | 免費

- 7十天學(xué)會AVR單片機與C語言視頻教程 下載

- 158M | 183279次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評論