資料介紹

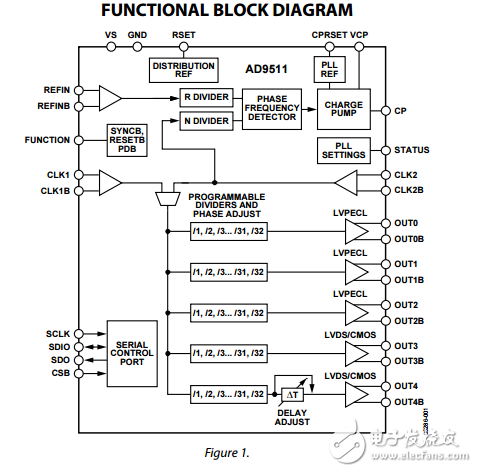

The AD9511 provides a multi-output clock distribution function along with an on-chip PLL core. The design emphasizes low jitter and phase noise to maximize data converter performance. Other applications with demanding phase noise and jitter requirements also benefit from this part. The PLL section consists of a programmable reference divider (R); a low noise phase frequency detector (PFD); a precision charge pump (CP); and a programmable feedback divider (N)。 By connecting an external VCXO or VCO to the CLK2/CLK2B pins, frequencies up to 1.6 GHz may be synchronized to the input reference. There are five independent clock outputs. Three outputs are LVPECL (1.2 GHz), and two are selectable as either LVDS (800 MHz) or CMOS (250 MHz) levels. Each output has a programmable divider that may be bypassed or set to divide by any integer up to 32. The phase of one clock output relative to another clock output may be varied by means of a divider phase select function that serves as a coarse timing adjustment. One of the LVDS/CMOS outputs features a programmable delay element with full-scale ranges up to 10 ns of delay. This fine tuning delay block has 5-bit resolution, giving 32 possible delays from which to choose for each full-scale setting. The AD9511 is ideally suited for data converter clocking applications where maximum converter performance is achieved by encode signals with subpicosecond jitter. The AD9511 is available in a 48-lead LFCSP and can be operated from a single 3.3 V supply. An external VCO, which requires an extended voltage range, can be accommodated by connecting the charge pump supply (VCP) to 5.5 V. The temperature range is ?40°C to +85°C.

- CDC2510C鎖相環時鐘驅動器數據表

- CDCVF2510A鎖相環(PLL)時鐘驅動器數據表

- CDCVF2505時鐘鎖相環時鐘驅動器數據表

- CDCU2A877鎖相環時鐘驅動器數據表

- LMK01000高性能時鐘緩沖器、分頻器和分配器數據表

- AD9515 1.6 GHz時鐘分配IC,分頻器,延遲調整,雙輸出數據表

- AD800/AD802:時鐘恢復和數據重定時鎖相環數據表

- AD9576:雙鎖相環異步時鐘發生器數據表

- AD9573:PCI-Express時鐘發生器IC,PLL內核,分頻器,雙輸出數據表

- AD9577:帶雙鎖相環、擴頻和余量的時鐘發生器數據表

- AD9515:1.6 GHz時鐘分配IC、分頻器、延遲調整、雙輸出數據表

- AD9512:1.2 GHz時鐘分配IC,1.6 GHz輸入,分頻器,延遲調整,五輸出數據表

- AD9508:1.65 GHz時鐘扇出緩沖器,集成輸出分頻器和延遲調整

- AD9510:1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,8路輸出

- AD9511: 1.2 GHz Clock Distribution IC, PLL Core, Dividers, Delay Adjust, Five Outputs Data Sheet

- 鎖相環的基本原理和主要作用 2250次閱讀

- 硬件電路設計之鎖相環電路設計 1977次閱讀

- 鎖相環的構成和工作原理講解 2881次閱讀

- 鎖相環電路設計的解決方案 鎖相環的基本構成和主要應用 1096次閱讀

- 使用MAX9382的鎖相環應用 953次閱讀

- 12GHz、超低相位噪聲小數N分頻鎖相環的設計 1101次閱讀

- 鎖相環PLL的基礎知識 4644次閱讀

- 鎖相環中的分頻器 2792次閱讀

- 如何實現高性能的鎖相環(PLL)設計 3654次閱讀

- CD4046鎖相環的應用詳細介紹 1w次閱讀

- 關于2.4 GHz的低噪聲亞采樣鎖相環設計 9568次閱讀

- 為什么要使用電子分頻器_電子分頻器工作原理及調整方法 2.5w次閱讀

- 鎖相環PLL的電路原理以及基本構成 4.7w次閱讀

- 鎖相環的作用是什么_鎖相環的主要作用_什么是鎖相環 3.5w次閱讀

- 鎖相環的電源管理設計 3863次閱讀

下載排行

本周

- 1TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 2開關電源基礎知識

- 5.73 MB | 6次下載 | 免費

- 3100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 4嵌入式linux-聊天程序設計

- 0.60 MB | 3次下載 | 免費

- 5基于FPGA的光纖通信系統的設計與實現

- 0.61 MB | 2次下載 | 免費

- 651單片機窗簾控制器仿真程序

- 1.93 MB | 2次下載 | 免費

- 751單片機大棚環境控制器仿真程序

- 1.10 MB | 2次下載 | 免費

- 8基于51單片機的RGB調色燈程序仿真

- 0.86 MB | 2次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應用800例(新編版)

- 0.00 MB | 33564次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關電源設計實例指南

- 未知 | 21549次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數字電路基礎pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅動電路設計》 溫德爾著

- 0.00 MB | 6653次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537796次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191185次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183279次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論