資料介紹

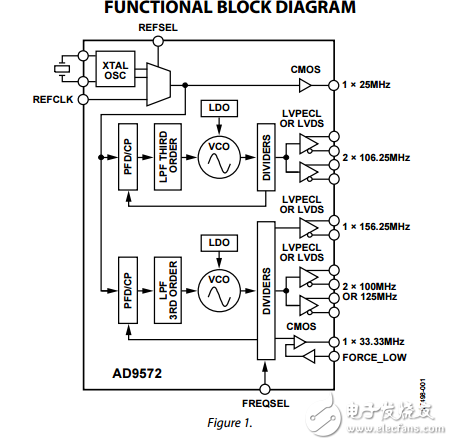

The AD9572 provides a multioutput clock generator function along with two on-chip PLL cores, optimized for fiber channel line card applications that include an Ethernet interface. The integer-N PLL design is based on the Analog Devices, Inc., proven portfolio of high performance, low jitter frequency synthesizers to maximize network performance. Other applications with demanding phase noise and jitter requirements also benefit from this part. The PLL section consists of a low noise phase frequency detector (PFD), a precision charge pump (CP), a low phase noise voltage controlled oscillator (VCO), and a preprogrammed feedback divider and output divider. By connecting an external crystal or reference clock to the REFCLK pin, frequencies up to 156.25 MHz can be locked to the input reference. Each output divider and feedback divider ratio is preprogrammed for the required output rates. A second PLL also operates as an integer-N synthesizer and drives two LVPECL or LVDS output buffers for 106.25 MHz operation. No external loop filter components are required, thus conserving valuable design time and board space. The AD9572 is available in a 40-lead, 6 mm × 6 mm lead frame chip scale package (LFCSP) and can be operated from a single 3.3 V supply. The temperature range is ?40°C to +85°C

- 集成2.5 GHz壓控振蕩器數(shù)據(jù)表的AD9517-1 12輸出時鐘發(fā)生器

- 集成2.0 GHz壓控振蕩器數(shù)據(jù)表的AD9518-3 6輸出時鐘發(fā)生器

- 集成2.2 GHz壓控振蕩器數(shù)據(jù)表的AD9517-2 12輸出時鐘發(fā)生器

- AD9516-3:14輸出時鐘發(fā)生器,集成2.0 GHz壓控振蕩器數(shù)據(jù)表

- AD9531:3通道時鐘發(fā)生器,24輸出數(shù)據(jù)表

- AD9575:網(wǎng)絡(luò)時鐘發(fā)生器,雙輸出數(shù)據(jù)表

- AD9517-4:12輸出時鐘發(fā)生器,集成1.6 GHz壓控振蕩器數(shù)據(jù)表

- AD9522-5:12 LVDS/24 CMOS輸出時鐘發(fā)生器數(shù)據(jù)表

- AD9516-5:14-輸出時鐘發(fā)生器數(shù)據(jù)表

- AD9520-5:12 LVPECL/24 CMOS輸出時鐘發(fā)生器數(shù)據(jù)表

- AD9571:以太網(wǎng)時鐘發(fā)生器,10個時鐘輸出

- AD9517-1:12輸出時鐘發(fā)生器,集成2.5 GHz壓控振蕩器數(shù)據(jù)表

- AD9517-2:12輸出時鐘發(fā)生器,集成2.2 GHz壓控振蕩器數(shù)據(jù)表

- AD9518-3:6輸出時鐘發(fā)生器,集成2.0 GHz壓控振蕩器數(shù)據(jù)表

- AD9518-1:6輸出時鐘發(fā)生器,集成2.5 GHz壓控振蕩器數(shù)據(jù)表

- 時鐘合成器和時鐘發(fā)生器的區(qū)別 586次閱讀

- 超低抖動時鐘發(fā)生器如何優(yōu)化串行鏈路系統(tǒng)性能 582次閱讀

- 評估低抖動PLL時鐘發(fā)生器的電源噪聲抑制 1238次閱讀

- 雙環(huán)路時鐘發(fā)生器清除抖動,提供多個高頻輸出 1105次閱讀

- 時鐘發(fā)生器性能對數(shù)據(jù)轉(zhuǎn)換器的影響 1216次閱讀

- 一個帶有COB的1Hz時鐘發(fā)生器電路 2323次閱讀

- 基于HFCT-53D5光纖收發(fā)器的千兆位以太網(wǎng)解決方案 2908次閱讀

- MB86R02“ Jade-D”的擴(kuò)頻時鐘生成單元應(yīng)用 2371次閱讀

- 如何選擇合適的時鐘發(fā)生器 2853次閱讀

- 基于VersaClock6系列的多輸出可編程時鐘發(fā)生器的應(yīng)用研究 903次閱讀

- 慎重考慮時鐘發(fā)生器的相位噪聲、抖動性能 6324次閱讀

- MCU UPD78F0527的三種系統(tǒng)時鐘 1675次閱讀

- 時鐘發(fā)生器的基本構(gòu)造_時鐘發(fā)生器對主機(jī)板的作用 1.1w次閱讀

- 集成晶體的可編程時鐘可提供多種設(shè)計優(yōu)勢而無性能折衷 994次閱讀

- 雙環(huán)路時鐘發(fā)生器可清除抖動并提供多個高頻輸出 7642次閱讀

下載排行

本周

- 1TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 2開關(guān)電源基礎(chǔ)知識

- 5.73 MB | 6次下載 | 免費

- 3100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 4嵌入式linux-聊天程序設(shè)計

- 0.60 MB | 3次下載 | 免費

- 5基于FPGA的光纖通信系統(tǒng)的設(shè)計與實現(xiàn)

- 0.61 MB | 2次下載 | 免費

- 651單片機(jī)窗簾控制器仿真程序

- 1.93 MB | 2次下載 | 免費

- 751單片機(jī)大棚環(huán)境控制器仿真程序

- 1.10 MB | 2次下載 | 免費

- 8基于51單片機(jī)的RGB調(diào)色燈程序仿真

- 0.86 MB | 2次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33564次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關(guān)電源設(shè)計實例指南

- 未知 | 21549次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數(shù)字電路基礎(chǔ)pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅(qū)動電路設(shè)計》 溫德爾著

- 0.00 MB | 6653次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537796次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191185次下載 | 免費

- 7十天學(xué)會AVR單片機(jī)與C語言視頻教程 下載

- 158M | 183279次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評論