資料介紹

高分辨率圖像實(shí)時(shí)處理在通信、醫(yī)學(xué)、軍事、航天航空、信息安全等領(lǐng)域有著廣泛的應(yīng)用和發(fā)展。在圖像實(shí)時(shí)處理的過程中,下層圖像預(yù)處理的數(shù)據(jù)量大,運(yùn)算簡(jiǎn)單,但是要求運(yùn)算速率高,可以用FPGA硬件來處理,上層所處理的數(shù)據(jù)量少,算法結(jié)構(gòu)復(fù)雜,適于運(yùn)算速度快,尋址靈活的DSP數(shù)字信號(hào)處理器進(jìn)行處理。這里提出了一種FPGA+DSP相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng),并應(yīng)用于傳像光線束傳遞圖像。CMOS實(shí)際采集的是光線束的出端圖像,F(xiàn)PGA將CMOS采集的Bayer格式的圖像轉(zhuǎn)換為RGB格式的亮度信號(hào)。由于光纖出、入端結(jié)構(gòu)不同,需要DSP準(zhǔn)確每根光纖的中心位置,重新排序才能輸出正確的圖像信息。該系統(tǒng)充分發(fā)揮了FPGA和DSP各自的優(yōu)勢(shì),能更好地提高圖像處理的實(shí)時(shí)性,降低成本。

1Bayer圖像格式

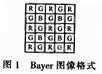

CMOS圖像傳感器作為一種基礎(chǔ)器件可以實(shí)現(xiàn)信息的采集、轉(zhuǎn)換以及視覺功能的擴(kuò)展,并能直觀真實(shí)地給出可視圖像信息。系統(tǒng)中CMOS圖像傳感器輸出2 592x1 944x12 bit的Bayer格式的圖像(該格式的圖像本身就是數(shù)字信號(hào),因此無需對(duì)圖像進(jìn)行模數(shù)轉(zhuǎn)換),Bayer圖像格式如圖1所示。在圖l中,每個(gè)方格代表一個(gè)像素,并且只含有R、G、B中的一種顏色分量,奇數(shù)行由G、R像素交替構(gòu)成,偶數(shù)行由B、G像素交替進(jìn)行,其中G像素分量占所有像素的一半,R像素和G像素占另一半。因?yàn)镚像素分量是R、B像素分量的2倍,所以如果G像素分量采用好的插值方法,不僅可以提高G像素分量的質(zhì)量,也能提高R和B像素分量的質(zhì)量。由于TMS320DM642的video port capture接口的數(shù)據(jù)總線是8位或者16位(該系統(tǒng)采用了更適合DSP處理的8位數(shù)據(jù)),所以為了后續(xù)的DSP能夠更好的處理數(shù)據(jù)并減少DSP的運(yùn)算量,需要使用FPGA先將輸出的圖像數(shù)據(jù)取高8位,然后依據(jù)每個(gè)像素點(diǎn)與相鄰8個(gè)像素點(diǎn)之間的關(guān)系,使用雙線性插值法將Bayer圖像格式轉(zhuǎn)換成24位的RGB圖像格式和亮度信號(hào),然后將處理后的數(shù)據(jù)發(fā)送給DSP。

2圖像數(shù)據(jù)處理的工作原理

2.1Bayer圖像的格式轉(zhuǎn)換

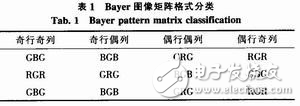

雙線性插值法具有算法計(jì)算量少,算法結(jié)構(gòu)簡(jiǎn)單,易于實(shí)現(xiàn),占硬件資源少等優(yōu)點(diǎn),本系統(tǒng)中更適合FPGA實(shí)現(xiàn)。雙線性插值法的基本原理是將每個(gè)像素位置上缺少的另外兩種色彩分量通過該像素本身為中心的領(lǐng)域內(nèi)具有相同分量的像素平均獲得,即將每個(gè)像素的RGB分量都以該點(diǎn)像素為中心的3x3像素矩陣進(jìn)行線性插值而成。按照這種思路可以將圖像中的3x3矩陣分成4類,如表1所示。

1Bayer圖像格式

CMOS圖像傳感器作為一種基礎(chǔ)器件可以實(shí)現(xiàn)信息的采集、轉(zhuǎn)換以及視覺功能的擴(kuò)展,并能直觀真實(shí)地給出可視圖像信息。系統(tǒng)中CMOS圖像傳感器輸出2 592x1 944x12 bit的Bayer格式的圖像(該格式的圖像本身就是數(shù)字信號(hào),因此無需對(duì)圖像進(jìn)行模數(shù)轉(zhuǎn)換),Bayer圖像格式如圖1所示。在圖l中,每個(gè)方格代表一個(gè)像素,并且只含有R、G、B中的一種顏色分量,奇數(shù)行由G、R像素交替構(gòu)成,偶數(shù)行由B、G像素交替進(jìn)行,其中G像素分量占所有像素的一半,R像素和G像素占另一半。因?yàn)镚像素分量是R、B像素分量的2倍,所以如果G像素分量采用好的插值方法,不僅可以提高G像素分量的質(zhì)量,也能提高R和B像素分量的質(zhì)量。由于TMS320DM642的video port capture接口的數(shù)據(jù)總線是8位或者16位(該系統(tǒng)采用了更適合DSP處理的8位數(shù)據(jù)),所以為了后續(xù)的DSP能夠更好的處理數(shù)據(jù)并減少DSP的運(yùn)算量,需要使用FPGA先將輸出的圖像數(shù)據(jù)取高8位,然后依據(jù)每個(gè)像素點(diǎn)與相鄰8個(gè)像素點(diǎn)之間的關(guān)系,使用雙線性插值法將Bayer圖像格式轉(zhuǎn)換成24位的RGB圖像格式和亮度信號(hào),然后將處理后的數(shù)據(jù)發(fā)送給DSP。

2圖像數(shù)據(jù)處理的工作原理

2.1Bayer圖像的格式轉(zhuǎn)換

雙線性插值法具有算法計(jì)算量少,算法結(jié)構(gòu)簡(jiǎn)單,易于實(shí)現(xiàn),占硬件資源少等優(yōu)點(diǎn),本系統(tǒng)中更適合FPGA實(shí)現(xiàn)。雙線性插值法的基本原理是將每個(gè)像素位置上缺少的另外兩種色彩分量通過該像素本身為中心的領(lǐng)域內(nèi)具有相同分量的像素平均獲得,即將每個(gè)像素的RGB分量都以該點(diǎn)像素為中心的3x3像素矩陣進(jìn)行線性插值而成。按照這種思路可以將圖像中的3x3矩陣分成4類,如表1所示。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 基于FPGA+DSP彈載SAR信號(hào)處理系統(tǒng)設(shè)計(jì)

- 如何使用FPGA和DSP實(shí)現(xiàn)CCD圖像相關(guān)處理系統(tǒng) 140次下載

- 如何使用FPGA和DSP實(shí)現(xiàn)高速CCD信號(hào)采集處理系統(tǒng)的設(shè)計(jì) 24次下載

- 基于FPGA+DSP的圖像處理系統(tǒng)解析 12次下載

- 基于DSP和FPGA的模塊化實(shí)時(shí)圖像處理系統(tǒng)設(shè)計(jì) 9次下載

- 基于FPGA和DSP的高速圖像處理系統(tǒng) 20次下載

- 基于FPGA的視頻圖像處理系統(tǒng)設(shè)計(jì)_李蓮 21次下載

- 基于雙DSP和雙FPGA的高速圖像處理系統(tǒng)設(shè)計(jì)_吳雷 2次下載

- 基于FPGA+DSP實(shí)時(shí)圖像采集處理系統(tǒng)設(shè)計(jì) 9次下載

- 基于FPGA的玻璃缺陷圖像采集預(yù)處理系統(tǒng)設(shè)計(jì) 13次下載

- 基于DSP和FPGA架構(gòu)的嵌入式圖像處理系統(tǒng)設(shè)計(jì) 62次下載

- FPGA+DSP的紅外圖像數(shù)據(jù)采集與顯示 87次下載

- 基于DSP與雙目CMOS攝像頭的數(shù)字圖像處理系統(tǒng) 489次下載

- 基于ADSP21060和Virtex II的圖像處理系統(tǒng)設(shè)計(jì)

- 基于FPGA和DSP的光纖信號(hào)實(shí)時(shí)處理系統(tǒng)

- 基于MATLAB的信號(hào)處理系統(tǒng)與分析 625次閱讀

- 基于OMAP5910雙核處理器實(shí)現(xiàn)實(shí)時(shí)圖像處理系統(tǒng)的應(yīng)用設(shè)計(jì) 2287次閱讀

- 以FPGA+DSP為核心架構(gòu)的實(shí)時(shí)三維圖像信息處理系統(tǒng)設(shè)計(jì) 1395次閱讀

- 基于FPGA和四端口存儲(chǔ)器的三DSP圖像處理系統(tǒng)詳解 901次閱讀

- 以FPGA和TMS320DM642為核心的實(shí)時(shí)圖像采集和處理系統(tǒng)設(shè)計(jì)詳解 2781次閱讀

- 基于HD-SDI技術(shù)的高清圖像處理系統(tǒng)設(shè)計(jì) 2301次閱讀

- 基于FPGA+DSP的視頻控制的智能交通燈設(shè)計(jì) 2043次閱讀

- 一種基于DSP+FPGA視頻圖像采集處理系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn) 4763次閱讀

- 基于DSP+FPGA的實(shí)時(shí)圖像去霧增強(qiáng)系統(tǒng)設(shè)計(jì) 3636次閱讀

- 基于FPGA的視頻圖像處理系統(tǒng)的設(shè)計(jì) 4779次閱讀

- 基于FPGA+DSP的跳頻電臺(tái)傳輸系統(tǒng)的設(shè)計(jì)方案分析 2179次閱讀

- 基于多DSP與FPGA的實(shí)時(shí)圖像處理系統(tǒng)設(shè)計(jì) 4178次閱讀

- 基于FPGA+DSP架構(gòu)視頻處理系統(tǒng)設(shè)計(jì) 1255次閱讀

- FPGA+DSP的高速通信接口設(shè)計(jì)與實(shí)現(xiàn) 7623次閱讀

- 基于DSP的最小圖像采集處理系統(tǒng)設(shè)計(jì) 2375次閱讀

下載排行

本周

- 1TC358743XBG評(píng)估板參考手冊(cè)

- 1.36 MB | 330次下載 | 免費(fèi)

- 2開關(guān)電源基礎(chǔ)知識(shí)

- 5.73 MB | 6次下載 | 免費(fèi)

- 3100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 4嵌入式linux-聊天程序設(shè)計(jì)

- 0.60 MB | 3次下載 | 免費(fèi)

- 5基于FPGA的光纖通信系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

- 0.61 MB | 2次下載 | 免費(fèi)

- 6基于FPGA的C8051F單片機(jī)開發(fā)板設(shè)計(jì)

- 0.70 MB | 2次下載 | 免費(fèi)

- 751單片機(jī)窗簾控制器仿真程序

- 1.93 MB | 2次下載 | 免費(fèi)

- 8基于51單片機(jī)的RGB調(diào)色燈程序仿真

- 0.86 MB | 2次下載 | 免費(fèi)

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費(fèi)

- 2555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33564次下載 | 免費(fèi)

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費(fèi)

- 4開關(guān)電源設(shè)計(jì)實(shí)例指南

- 未知 | 21548次下載 | 免費(fèi)

- 5電氣工程師手冊(cè)免費(fèi)下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費(fèi)

- 6數(shù)字電路基礎(chǔ)pdf(下載)

- 未知 | 13750次下載 | 免費(fèi)

- 7電子制作實(shí)例集錦 下載

- 未知 | 8113次下載 | 免費(fèi)

- 8《LED驅(qū)動(dòng)電路設(shè)計(jì)》 溫德爾著

- 0.00 MB | 6653次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費(fèi)

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537796次下載 | 免費(fèi)

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費(fèi)

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費(fèi)

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費(fèi)

- 6電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191185次下載 | 免費(fèi)

- 7十天學(xué)會(huì)AVR單片機(jī)與C語言視頻教程 下載

- 158M | 183278次下載 | 免費(fèi)

- 8proe5.0野火版下載(中文版免費(fèi)下載)

- 未知 | 138040次下載 | 免費(fèi)

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評(píng)論