資料介紹

摘要:

介紹以TMS320F240為核心,設計IDE接口仿零點器的硬件和軟件設計方法。突出特點是硬件設計簡練實用,監控軟件精巧靈活。在設計嵌入式系統調試工具中具有典型性和實用性,對其它系統的調試也借鑒作用。 關鍵詞:仿真器 監控程序 硬件調試 IDE接口 隨著航空電子系統數字化的發展,機載嵌入式計算機逐步擺脫了“純粹嵌入”時代,開始以主要控制角色而顯露頭腳。其存儲系統也和地面計算機系統一樣,提出了“海量存儲”的要求。借鑒和使用IDE接品時一條重要途徑。但在調試時一般缺乏IDE接口主方(Host)控制器。PC機雖然帶有兩個標準的集成在主板上的IDE接口,但在目前的Widows系統下卻是透明的,無法在硬件調試級進行控制驅動。“工欲善其事,必先利其器”。為解決調試工具,筆者在此前自己動手,設計了一個IDE接口仿真器。硬件極其簡練實用,軟件精巧靈活。介紹出來,與大家切磋。

1 仿真器硬件設計

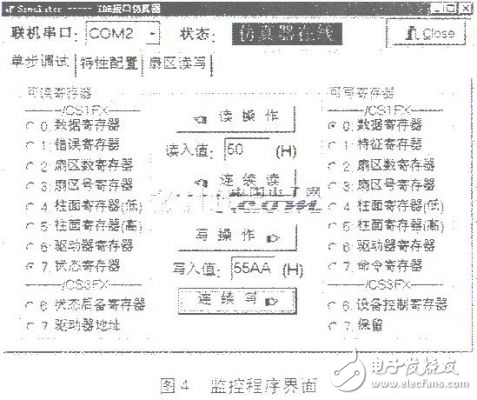

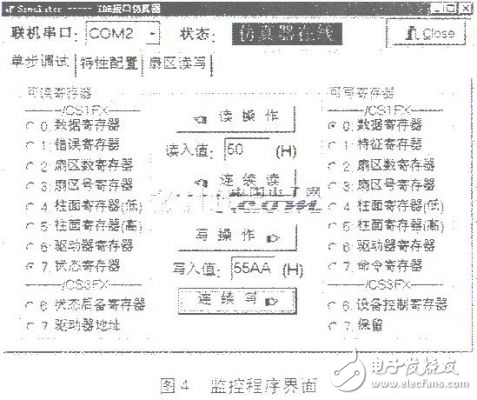

眾所周知,IDE/ATA接口是16位總線,映像在主機的I/O空間,由主機對接口內的2組寄存器操作來完成“海量存儲”。這些寄存器僅由2根片選(CS1FX、CS3FX)和3根地址線(A2、A1、A0)尋址。仿真器硬件只要能在監控程序的控制下產生對應控制信號,便能真實地仿真IDE調試所需的環境。需要仿真處理的主要信號如表1所列。信號方向以仿真器為參照,輸出(Output)方向由仿真器驅動,輸入(Input)信號由IDE設備驅動。 表1 主要仿真處理的信號 信號名方 向有效電平功 能 HDRST O(輸出) L(低)復位IDE設備 CS1FX O(輸出) L(低)第一組寄存器片選 CS3FX O(輸出) L(低)第二組寄存器片選 A2~A0 O(輸出)組合值接口內寄存器偏移地址 IOR O(輸出) L(低)寄存器讀信號 IOW O(輸出) L(低)寄存器寫信號 D15D0 I/O(雙向)組合值數據總線,寫時由仿真器驅動,讀時由IDE設備驅動 DRQ I(輸入) H(高) DMA請求 IRQ I(輸入) H(高)中斷請求 IDE接口的讀寫時序和一般CPU外設時序波形相似,其讀取周期為70ns,具體波形不再給出。使用TI公司的TMS320F240(以下簡稱F240)可以方便地仿真出IDE的時序波形。只要使用外部READY信號,把I/O周期延長到70ns以上,就可以保證仿真數據讀寫可靠。以F240為核心,仿真器硬件設計真數據讀寫可靠。以F240為核心,仿真器硬件設計就非常簡練。其全部硬件電路如圖1、圖2和圖3所示。除去初期調試和驅動芯片外,整個核心就是F240和GAL16V8,已經仿真全部的IDE時序波形,圖1是仿真器自身調試仿真監控程序時電路。使用2片CY7C199,組成32K%26;#215;16位的片外RAM程序存儲器空間。當程序調試完成后,斷開H1,將監控程序通過JTAG口直接燒入F240,就可以拔去2片外部程序存儲器CY7C199。 圖1 調試時的程序存儲器配置 當仿真監控程序調試完成后,正式定型的仿真核心電路如圖2所示。電路設計總的原則是簡練實用,所以復位采用普通的RC電路,外加手工復位開關SW保證仿真器自身復位;利用RS232和主機之間通信,減少硬件額外開銷;IDE接口的中斷請求HIRQ直接接F240的外部中斷XINT1(因為HIRQ高電平有效,所以將蓁不用的外部斷XINT2等接地,保證蓁中斷源不產生中斷請求,減少軟件中斷響應多重判斷環節);將F240的PB端口設置為輸出端口,DMA請求HDRQ接到PB端口的最低位PB0,可以直接由硬件檢測DRQ狀態即可,并不真正需要DMA控制器;將F240的PC端口設置為輸出端品,最高位PC7為復位IDE端口信號,當該位設置為0(低電平)時,產生復位IDE設備信號HDRST,該位設置為1時結束復位。其復位時間可由軟件控制。IDE設備的寄存器映像在F240的I/O空間從0000H開始的16位地址。外部I/O只有IDE接口,不必采用全譯碼,直接由I/O片選IS和地址A3區分產生CFIFX和CS3FX即可。接口內偏移地址直接由A2~A0提供。F240的寫信號WR可以直接作為接口寫信號。但是F240的讀信號是狀態信號,在連續讀操作中保持低電平,并無上升沿,所以需要專門產生讀信號。PC主機通過串口和仿真器通信,監控仿真器,從而驅動調試的IDE設備。仿真器和IDE設備通過標準的硬盤電纜連接。為提高信號的抗干擾能力,這些信號經過總線驅動器驅動。圖3是驅動和接口電路。 數據通路用16路驅動的IDT74LS16245實現,開門信號直接由I/O片選信號IS控制,方向端由寫信號WR控制。而單向提供給IDE設備的其它信號,都經過54F244驅動。所有控制信號由GAL16V8實現。以下是其控制邏輯代碼,信號名稱和功能可參見 。 圖2 核心仿真控制電路 …… EQUATIONS !HRST=!POR#!HRST;//RC上電復位和F240設置復位都產生IDE復位 !CS1FX=!IS%26;amp;!A3; //A3=0;產生第一組寄存器片選CS1FX=!IS %26;amp; A3; //A3=1:產生第二組寄存器片選CS3FX !IOR=!IS %26;amp; !RD; //*專門產生寄存器讀信號。 [Q1,Q0].CLK=CPUCLK; [Q1,Q0].OE=!OE; [Q1,Q0].AR=!POR; //復位 //============================================== //F240系統控制狀態機 //時鐘20MHz,每一拍50ns //程序存儲器CY7C199讀寫周期≤35ns,無需等待 //IDE接口寄存器讀寫周期≥70ns,等待2拍 //=============================================== State_Diagram [Q1,Q0]; State S0: //空閑狀態 READY=H; //支持CY7C199訪問 if(!IS)then //要訪問IDE接口寄存器 S1 with {READY240=L;} State S1: //開始等待 READY240=L; Goto S2; State S2: READY240=L; Goto S3; State3: //時間到 READY240=H; Goto S0; //F240對READY信號只采樣一次 END 仿真硬件的核心只有1片F240和1片GAL16V8。 驅動與接口電路 2 仿真器監控軟件設計 軟件設計包括駐留F240的監控程序和PC宿主機的監控程序,兩者之間通過串口配合工作。這當然降低了IDE接口的數據吞吐率,但在邏輯仿真調試時不是主要焦點。為簡約起見,避免復雜的詞法分析,主從之間采用單字符監控命令。其串口監控命令通信幀定義如下: 0 1 2…n-2 n-1 幀標志(AAH)命令字符(Cmd)參數項校驗和CheckSum 其校驗和為前n-1個字節代數和的補碼,即 CheckSum=-∑Bi(i=0,1…n-1) 下面介紹幾個主要命令和程序實現方法,其中寄存器名稱和地址可參考圖4界面。

(1)1命令:讀IDE寄存器 當監控程序識別出1命令后,根據參數提供的寄存器索引,映射為對應的I/O地址。F240的輸入/輸出命令與x86系列不同,它在指令中必須直接給出地址。 … LACC Reg BZ IsDatReg ;0號索引,即讀數據寄存器 SUB #1 BZ IsError ;/*號索引,即讀錯誤類型寄存器 … BZ IsAltReg ;8號索引,即讀后備狀態寄存器 SUB #1 BZ IsDrvAddrReg ;9號索引,即讀驅動器地址寄存器 … IsDatReg IN Value,DatReg ;讀數據寄存器 RET IsAltReg: IN Value,DevAddrReg;讀驅動器地址寄存器 RET 當I命令執行完畢后,應該將寄存器讀入值回送PC主機。

(2)0命令:寫IDE寄存器 寄存器輸出命令參數需要提供寄存器索引和映射為對應的I/O地址。

(3)H命令:硬件復位IDE設備 硬件復位時應將F240的IOPC7引腳設置為低電平10ms以上。 LDP #00E1h ;DP=00E1H:708H~70FFH的頁址 LACL #8000H ;D15=1:IOPC7:作輸出 D7=0;設置IOPC7=0 SACL PCDATDIR ;寫PC端口,設置HRST信號為低電平 CALL Delay 10ms ;保持復位信號10ms的低電平 LACL #8080H ;D15=1:IOPC7:作輸出 ;D7=1:設置IOPC7=1 SACL PCDATDIR ;恢復HRST信號為高電平 類似地,監測DMA請求HDRQ狀態時,可以設置端為輸入屬性,然后讀入IOPB0。監測中斷請求HIRQ時,可以直接讀XINT1狀態,即讀7070H處的XINT1CR寄存器。

(4)S命令:軟件復位IDE設備 軟件復位時可以向IDE接口的DevCtrlReg(設備控制寄存器)寫入適當值實現。 LDP #0 ;指向.bss變量區 SPLK=#000EH,Value ;D2=SW Rst=1:軟件強制復位 ;D1=/IEn=1:禁止IDE發中斷 OUT Value,DevCtrlReg ;復位IDE設備 CALL Delay 10ms ;保持復位狀態10ms SPLK #000AH,Value ;D2=SW Rst=0:結束復位狀態 OUT Value,DevCtrlReg CALL Delay 10ms SPLK #000EH,Value ;D6=LBA=1:采用邏輯塊尋址模式 OUT Value,DrvHeadReg ;設置驅動器寄存器

(5)C命令:讀取IDE設備ID號和相關配置 IDE設備內的相關配置對其它操作影響較大,主機應該掌握這些參數。諸如柱面數、磁頭數、每個磁道的扇區數以及最大扇區號等。這段程序稍微復雜一些。 CALL WaitRDY ;讀狀態寄存器,等待D6=1,亦即IDE設備完成上次命令 SPLK#000EH,Value OUT Value,DrvHeadReg ;選擇主從驅動器 SPLK #00ECH,Value OUT Value,CmdReg ;發命令,讀取配置參數 CALL WaitDRQ ;讀狀態寄存器,等待D6=1并且D3=1,亦即RDY并發出DRQ請求 MAR *,AR1 ;AR1:當前輔助寄存器 LAR AR1,#BufSADDR ;AR1→扇區緩沖區開始地址 RPT #0FFh ;循環次數=FFH+1=256 IN *+,DatReg ;讀入配置數據 讀出配置參數后,再把它送給PC機的監控程序,從中再細分出具體參數。 類似地,讀一個扇區或寫一個扇區的命令與這個命令相似。只是在發命令前應該設置柱面扇區等寄存器定位到具體的扇區。

(6)PC宿主機監控程序功能 PC宿主機監控程序主要通過串口監控仿真器。在底層通信中,應該為每一個監控命令建立對應函數。在應用層,可以將幾個簡單命令有機組合,完成復雜功能,減小仿真器駐留監控難度。例如,在讀取配置參數命令中,分解緩沖數據。在讀寫扇區命令中,將LBA邏輯扇區地址分解成驅動器號、扇區號、柱面號等。 重要的是為用戶提供一個Windows環境下特別容易操作的接口界面,貼近硬件調試,產生所需信號波形,用示波器捕獲分析。圖4是宿主機的一個界面,具體方法細節不再討論。 結語 隨著航空電子新系統研制的智能化和接口標準化,硬件調試對仿真設備和環境要求也越來越高。鑒于成本和上市時間的限制,采用嵌入式CPU研制一些簡單實用的仿真設備,是解決矛盾的一條重要途徑。本文所介紹的IDE接口仿真器硬件簡練、軟件精巧,在多個型號的Flash Disk研制中發揮了重要作用。

介紹以TMS320F240為核心,設計IDE接口仿零點器的硬件和軟件設計方法。突出特點是硬件設計簡練實用,監控軟件精巧靈活。在設計嵌入式系統調試工具中具有典型性和實用性,對其它系統的調試也借鑒作用。 關鍵詞:仿真器 監控程序 硬件調試 IDE接口 隨著航空電子系統數字化的發展,機載嵌入式計算機逐步擺脫了“純粹嵌入”時代,開始以主要控制角色而顯露頭腳。其存儲系統也和地面計算機系統一樣,提出了“海量存儲”的要求。借鑒和使用IDE接品時一條重要途徑。但在調試時一般缺乏IDE接口主方(Host)控制器。PC機雖然帶有兩個標準的集成在主板上的IDE接口,但在目前的Widows系統下卻是透明的,無法在硬件調試級進行控制驅動。“工欲善其事,必先利其器”。為解決調試工具,筆者在此前自己動手,設計了一個IDE接口仿真器。硬件極其簡練實用,軟件精巧靈活。介紹出來,與大家切磋。

1 仿真器硬件設計

眾所周知,IDE/ATA接口是16位總線,映像在主機的I/O空間,由主機對接口內的2組寄存器操作來完成“海量存儲”。這些寄存器僅由2根片選(CS1FX、CS3FX)和3根地址線(A2、A1、A0)尋址。仿真器硬件只要能在監控程序的控制下產生對應控制信號,便能真實地仿真IDE調試所需的環境。需要仿真處理的主要信號如表1所列。信號方向以仿真器為參照,輸出(Output)方向由仿真器驅動,輸入(Input)信號由IDE設備驅動。 表1 主要仿真處理的信號 信號名方 向有效電平功 能 HDRST O(輸出) L(低)復位IDE設備 CS1FX O(輸出) L(低)第一組寄存器片選 CS3FX O(輸出) L(低)第二組寄存器片選 A2~A0 O(輸出)組合值接口內寄存器偏移地址 IOR O(輸出) L(低)寄存器讀信號 IOW O(輸出) L(低)寄存器寫信號 D15D0 I/O(雙向)組合值數據總線,寫時由仿真器驅動,讀時由IDE設備驅動 DRQ I(輸入) H(高) DMA請求 IRQ I(輸入) H(高)中斷請求 IDE接口的讀寫時序和一般CPU外設時序波形相似,其讀取周期為70ns,具體波形不再給出。使用TI公司的TMS320F240(以下簡稱F240)可以方便地仿真出IDE的時序波形。只要使用外部READY信號,把I/O周期延長到70ns以上,就可以保證仿真數據讀寫可靠。以F240為核心,仿真器硬件設計真數據讀寫可靠。以F240為核心,仿真器硬件設計就非常簡練。其全部硬件電路如圖1、圖2和圖3所示。除去初期調試和驅動芯片外,整個核心就是F240和GAL16V8,已經仿真全部的IDE時序波形,圖1是仿真器自身調試仿真監控程序時電路。使用2片CY7C199,組成32K%26;#215;16位的片外RAM程序存儲器空間。當程序調試完成后,斷開H1,將監控程序通過JTAG口直接燒入F240,就可以拔去2片外部程序存儲器CY7C199。 圖1 調試時的程序存儲器配置 當仿真監控程序調試完成后,正式定型的仿真核心電路如圖2所示。電路設計總的原則是簡練實用,所以復位采用普通的RC電路,外加手工復位開關SW保證仿真器自身復位;利用RS232和主機之間通信,減少硬件額外開銷;IDE接口的中斷請求HIRQ直接接F240的外部中斷XINT1(因為HIRQ高電平有效,所以將蓁不用的外部斷XINT2等接地,保證蓁中斷源不產生中斷請求,減少軟件中斷響應多重判斷環節);將F240的PB端口設置為輸出端口,DMA請求HDRQ接到PB端口的最低位PB0,可以直接由硬件檢測DRQ狀態即可,并不真正需要DMA控制器;將F240的PC端口設置為輸出端品,最高位PC7為復位IDE端口信號,當該位設置為0(低電平)時,產生復位IDE設備信號HDRST,該位設置為1時結束復位。其復位時間可由軟件控制。IDE設備的寄存器映像在F240的I/O空間從0000H開始的16位地址。外部I/O只有IDE接口,不必采用全譯碼,直接由I/O片選IS和地址A3區分產生CFIFX和CS3FX即可。接口內偏移地址直接由A2~A0提供。F240的寫信號WR可以直接作為接口寫信號。但是F240的讀信號是狀態信號,在連續讀操作中保持低電平,并無上升沿,所以需要專門產生讀信號。PC主機通過串口和仿真器通信,監控仿真器,從而驅動調試的IDE設備。仿真器和IDE設備通過標準的硬盤電纜連接。為提高信號的抗干擾能力,這些信號經過總線驅動器驅動。圖3是驅動和接口電路。 數據通路用16路驅動的IDT74LS16245實現,開門信號直接由I/O片選信號IS控制,方向端由寫信號WR控制。而單向提供給IDE設備的其它信號,都經過54F244驅動。所有控制信號由GAL16V8實現。以下是其控制邏輯代碼,信號名稱和功能可參見 。 圖2 核心仿真控制電路 …… EQUATIONS !HRST=!POR#!HRST;//RC上電復位和F240設置復位都產生IDE復位 !CS1FX=!IS%26;amp;!A3; //A3=0;產生第一組寄存器片選CS1FX=!IS %26;amp; A3; //A3=1:產生第二組寄存器片選CS3FX !IOR=!IS %26;amp; !RD; //*專門產生寄存器讀信號。 [Q1,Q0].CLK=CPUCLK; [Q1,Q0].OE=!OE; [Q1,Q0].AR=!POR; //復位 //============================================== //F240系統控制狀態機 //時鐘20MHz,每一拍50ns //程序存儲器CY7C199讀寫周期≤35ns,無需等待 //IDE接口寄存器讀寫周期≥70ns,等待2拍 //=============================================== State_Diagram [Q1,Q0]; State S0: //空閑狀態 READY=H; //支持CY7C199訪問 if(!IS)then //要訪問IDE接口寄存器 S1 with {READY240=L;} State S1: //開始等待 READY240=L; Goto S2; State S2: READY240=L; Goto S3; State3: //時間到 READY240=H; Goto S0; //F240對READY信號只采樣一次 END 仿真硬件的核心只有1片F240和1片GAL16V8。 驅動與接口電路 2 仿真器監控軟件設計 軟件設計包括駐留F240的監控程序和PC宿主機的監控程序,兩者之間通過串口配合工作。這當然降低了IDE接口的數據吞吐率,但在邏輯仿真調試時不是主要焦點。為簡約起見,避免復雜的詞法分析,主從之間采用單字符監控命令。其串口監控命令通信幀定義如下: 0 1 2…n-2 n-1 幀標志(AAH)命令字符(Cmd)參數項校驗和CheckSum 其校驗和為前n-1個字節代數和的補碼,即 CheckSum=-∑Bi(i=0,1…n-1) 下面介紹幾個主要命令和程序實現方法,其中寄存器名稱和地址可參考圖4界面。

(1)1命令:讀IDE寄存器 當監控程序識別出1命令后,根據參數提供的寄存器索引,映射為對應的I/O地址。F240的輸入/輸出命令與x86系列不同,它在指令中必須直接給出地址。 … LACC Reg BZ IsDatReg ;0號索引,即讀數據寄存器 SUB #1 BZ IsError ;/*號索引,即讀錯誤類型寄存器 … BZ IsAltReg ;8號索引,即讀后備狀態寄存器 SUB #1 BZ IsDrvAddrReg ;9號索引,即讀驅動器地址寄存器 … IsDatReg IN Value,DatReg ;讀數據寄存器 RET IsAltReg: IN Value,DevAddrReg;讀驅動器地址寄存器 RET 當I命令執行完畢后,應該將寄存器讀入值回送PC主機。

(2)0命令:寫IDE寄存器 寄存器輸出命令參數需要提供寄存器索引和映射為對應的I/O地址。

(3)H命令:硬件復位IDE設備 硬件復位時應將F240的IOPC7引腳設置為低電平10ms以上。 LDP #00E1h ;DP=00E1H:708H~70FFH的頁址 LACL #8000H ;D15=1:IOPC7:作輸出 D7=0;設置IOPC7=0 SACL PCDATDIR ;寫PC端口,設置HRST信號為低電平 CALL Delay 10ms ;保持復位信號10ms的低電平 LACL #8080H ;D15=1:IOPC7:作輸出 ;D7=1:設置IOPC7=1 SACL PCDATDIR ;恢復HRST信號為高電平 類似地,監測DMA請求HDRQ狀態時,可以設置端為輸入屬性,然后讀入IOPB0。監測中斷請求HIRQ時,可以直接讀XINT1狀態,即讀7070H處的XINT1CR寄存器。

(4)S命令:軟件復位IDE設備 軟件復位時可以向IDE接口的DevCtrlReg(設備控制寄存器)寫入適當值實現。 LDP #0 ;指向.bss變量區 SPLK=#000EH,Value ;D2=SW Rst=1:軟件強制復位 ;D1=/IEn=1:禁止IDE發中斷 OUT Value,DevCtrlReg ;復位IDE設備 CALL Delay 10ms ;保持復位狀態10ms SPLK #000AH,Value ;D2=SW Rst=0:結束復位狀態 OUT Value,DevCtrlReg CALL Delay 10ms SPLK #000EH,Value ;D6=LBA=1:采用邏輯塊尋址模式 OUT Value,DrvHeadReg ;設置驅動器寄存器

(5)C命令:讀取IDE設備ID號和相關配置 IDE設備內的相關配置對其它操作影響較大,主機應該掌握這些參數。諸如柱面數、磁頭數、每個磁道的扇區數以及最大扇區號等。這段程序稍微復雜一些。 CALL WaitRDY ;讀狀態寄存器,等待D6=1,亦即IDE設備完成上次命令 SPLK#000EH,Value OUT Value,DrvHeadReg ;選擇主從驅動器 SPLK #00ECH,Value OUT Value,CmdReg ;發命令,讀取配置參數 CALL WaitDRQ ;讀狀態寄存器,等待D6=1并且D3=1,亦即RDY并發出DRQ請求 MAR *,AR1 ;AR1:當前輔助寄存器 LAR AR1,#BufSADDR ;AR1→扇區緩沖區開始地址 RPT #0FFh ;循環次數=FFH+1=256 IN *+,DatReg ;讀入配置數據 讀出配置參數后,再把它送給PC機的監控程序,從中再細分出具體參數。 類似地,讀一個扇區或寫一個扇區的命令與這個命令相似。只是在發命令前應該設置柱面扇區等寄存器定位到具體的扇區。

(6)PC宿主機監控程序功能 PC宿主機監控程序主要通過串口監控仿真器。在底層通信中,應該為每一個監控命令建立對應函數。在應用層,可以將幾個簡單命令有機組合,完成復雜功能,減小仿真器駐留監控難度。例如,在讀取配置參數命令中,分解緩沖數據。在讀寫扇區命令中,將LBA邏輯扇區地址分解成驅動器號、扇區號、柱面號等。 重要的是為用戶提供一個Windows環境下特別容易操作的接口界面,貼近硬件調試,產生所需信號波形,用示波器捕獲分析。圖4是宿主機的一個界面,具體方法細節不再討論。 結語 隨著航空電子新系統研制的智能化和接口標準化,硬件調試對仿真設備和環境要求也越來越高。鑒于成本和上市時間的限制,采用嵌入式CPU研制一些簡單實用的仿真設備,是解決矛盾的一條重要途徑。本文所介紹的IDE接口仿真器硬件簡練、軟件精巧,在多個型號的Flash Disk研制中發揮了重要作用。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- DK10仿真器燒寫TMS320F240的注意事項

- TMS320F240官方數據下載 3次下載

- 基于TMS320F240 DSP的開關磁阻電機控制系統 12次下載

- TMS320F240 DSP求解旋轉變壓器角位置和速度的方法 18次下載

- 基于TMS320F240的三相永磁同步電機速度場定向控制的實現 12次下載

- TMS320F240單片機 3次下載

- TMS320F240與外圍器件的SPI接口設計 25次下載

- TMS320F240在掃描式攝影點陣控制系統中的應用

- 基于TMS320F240的串行通訊設計

- TMS320F240開發板的研制

- 基于TMS320F240 的攝影點陣系統設計

- 基于TMS320F240控制步進電機的調焦系統設計

- TMS320F240 的IDE接口仿真器設計

- TMS320F240在高頻PWM調速器中的應用

- TMS320F240 pdf datasheet

- fpga仿真器接口定義 886次閱讀

- DPLink仿真器-好用的ARM仿真器推薦 1583次閱讀

- 將LCD仿真器與MAX-IDE和IAR嵌入式工作臺開發環境配合使用 1305次閱讀

- 電池仿真器的功能和應用 3405次閱讀

- 基于TMS320DM642和EPM240芯片實現圖像采集與處理系統的設計 3266次閱讀

- 基于DSP芯片TMS320F240實現PWM整流器控制系統的應用設計 2745次閱讀

- 米爾科技ULINKpro D 仿真器介紹 2536次閱讀

- DSP的串行通信接口SCI與PC機的通訊設計 5238次閱讀

- TMS320F28335最小應用系統設計電路 1.6w次閱讀

- CMSIS DAP仿真器的特點介紹 3w次閱讀

- TMS320f28335控制AD7656的硬件電路設計 1.1w次閱讀

- 什么是單片機仿真器_單片機仿真器有什么用_單片機仿真器怎么用 1.6w次閱讀

- 三大電機控制方案之DSP篇(1):TMS320F28335 5.5w次閱讀

- 基于SVPWM算法的變頻調速系統設計方案 4800次閱讀

- 基于DSP的自適應濾波器的設計方案 8236次閱讀

下載排行

本周

- 1TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 2開關電源基礎知識

- 5.73 MB | 6次下載 | 免費

- 3100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 4嵌入式linux-聊天程序設計

- 0.60 MB | 3次下載 | 免費

- 5基于FPGA的光纖通信系統的設計與實現

- 0.61 MB | 2次下載 | 免費

- 6基于FPGA的C8051F單片機開發板設計

- 0.70 MB | 2次下載 | 免費

- 751單片機窗簾控制器仿真程序

- 1.93 MB | 2次下載 | 免費

- 8基于51單片機的RGB調色燈程序仿真

- 0.86 MB | 2次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應用800例(新編版)

- 0.00 MB | 33564次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關電源設計實例指南

- 未知 | 21548次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數字電路基礎pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅動電路設計》 溫德爾著

- 0.00 MB | 6653次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537796次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191185次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183278次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論