資料介紹

描述

您可能已經(jīng)注意到,從版本 2021.1 開始,Vivado 中板預(yù)設(shè)文件的處理方式與 Xilinx Board Store 的引入略有不同。這是一個(gè)方便的添加,因?yàn)樗馕吨辉傩枰謩?dòng)安裝各種常見 Xilinx、Digilent、Avnet 和 Trenz Electronics 板的板預(yù)設(shè)文件。您可以通過簡(jiǎn)單地從板選擇中單擊“下載”來將它們安裝在創(chuàng)建新項(xiàng)目菜單中。

然而,由于Xilinx Board Store比較新,并且有其他供應(yīng)商提供的基于 Xilinx 的開發(fā)板,因此仍然需要手動(dòng)安裝板預(yù)設(shè)文件。這讓我有點(diǎn)難過,因?yàn)?Vivado 的文件結(jié)構(gòu)也發(fā)生了變化,以前版本中手動(dòng)安裝的舊目錄板預(yù)設(shè)文件不再存在。然而,在升級(jí)到 Vivado 2021.2 之后,我需要再次使用我的 ZynqberryZero,它恰好不在Xilinx Board Store 存儲(chǔ)庫中,這迫使我弄清楚板預(yù)設(shè)手動(dòng)安裝。我在 Ubuntu 18.04 上運(yùn)行 Vivado 2021.2。

添加電路板預(yù)設(shè)文件

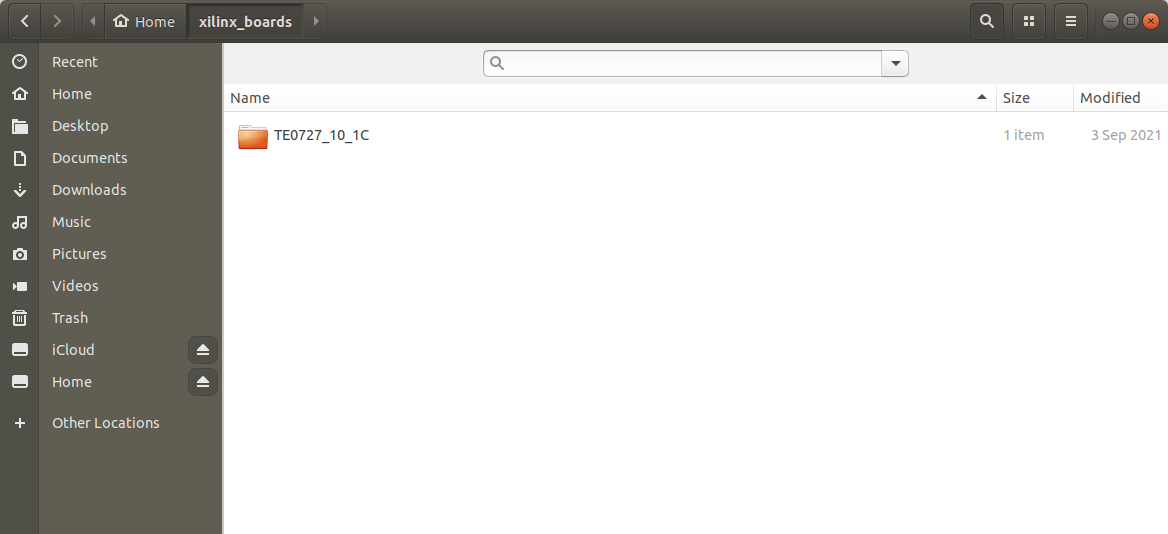

在易于記憶/訪問的地方為電路板預(yù)設(shè)文件創(chuàng)建本地目錄:

~$ mkdir -p xilinx_boards

將目標(biāo)開發(fā)板的板子預(yù)設(shè)文件復(fù)制到其中:

~$ cp -R ./Downloads/zbzerodemo1/board_files/TE0727_10_1C ./xilinx_boards

獲取 Vivado 環(huán)境并啟動(dòng) Vivado,但不要打開項(xiàng)目。

~$ source /tools/Xilinx/Vitis/2021.2/settings64.sh

~$ vivado

從工具菜單中選擇設(shè)置。

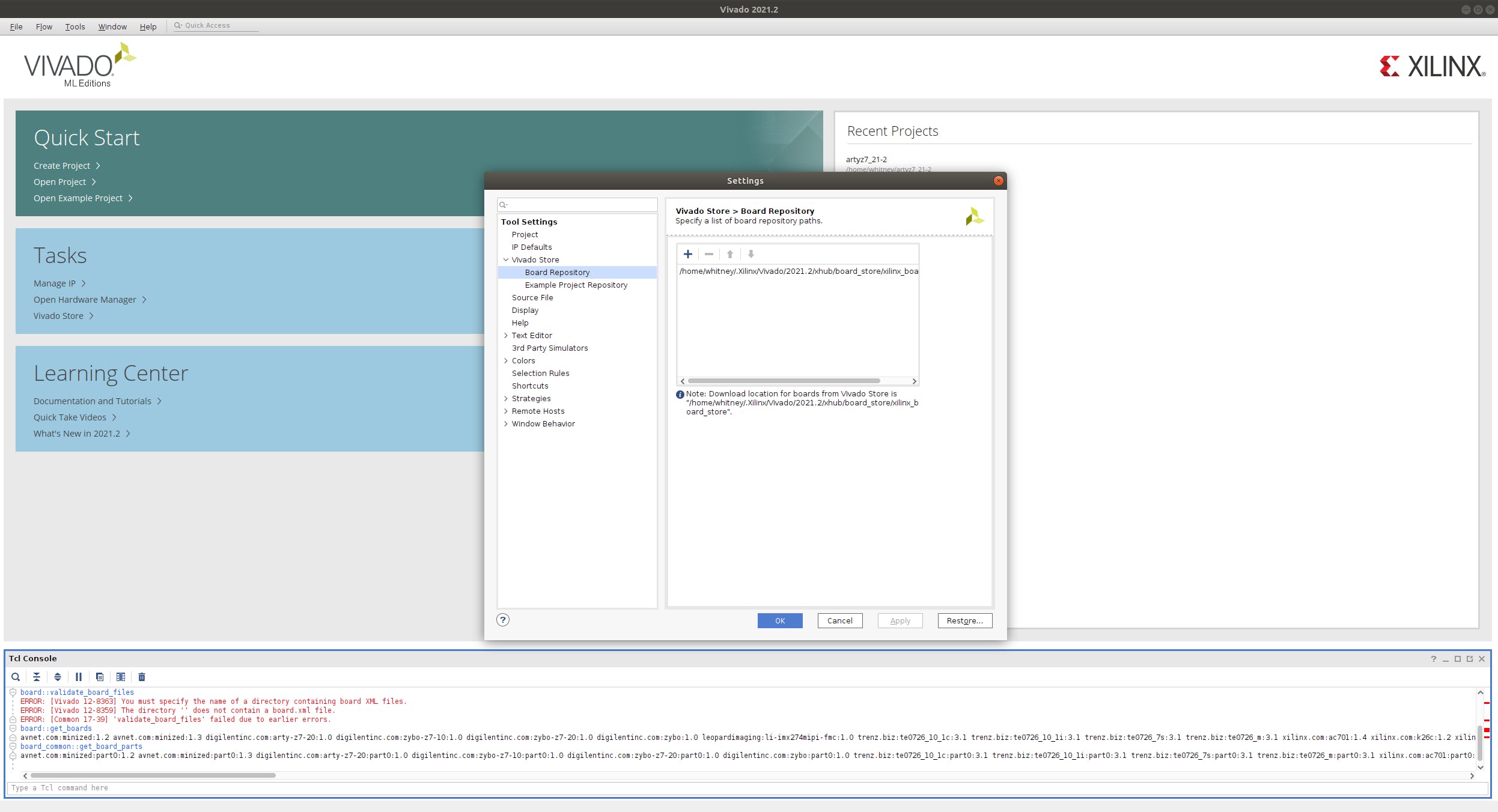

在“設(shè)置”菜單中,導(dǎo)航至Vivado Store > Board Repository 。

單擊+圖標(biāo)并指向我們剛剛在彈出窗口中為電路板預(yù)設(shè)文件創(chuàng)建的本地目錄。單擊“選擇”返回“設(shè)置”窗口。

單擊Apply ,然后單擊 OK將更改保存到 Vivado 并關(guān)閉Settings窗口。

您會(huì)注意到已經(jīng)指定了從Xilinx Board Store下載的電路板文件所在的目錄,剛剛創(chuàng)建的本地目錄將是 Vivado 在其中查找電路板預(yù)設(shè)文件的第二個(gè)位置。您現(xiàn)在可以簡(jiǎn)單地復(fù)制任何新的電路板預(yù)設(shè)將文件復(fù)制到本地目錄,以便在以后的項(xiàng)目中使用。

創(chuàng)建 Vivado 項(xiàng)目

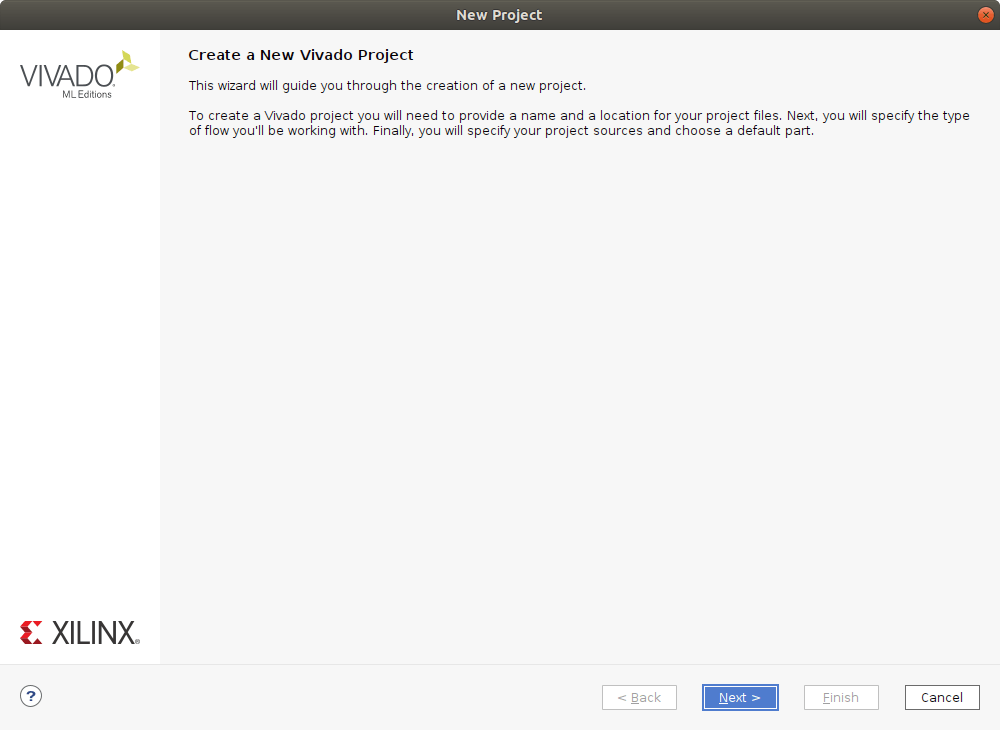

要測(cè)試新的本地板預(yù)設(shè)目錄,請(qǐng)單擊創(chuàng)建項(xiàng)目。為其指定所需的名稱和項(xiàng)目位置,將其指定為RTL 項(xiàng)目并選中選項(xiàng)Do not specify sources at this time 。

對(duì)于Default Part ,切換到Boards選項(xiàng)卡并搜索TE0727 。選擇它并單擊下一步。

和成功!本地板預(yù)設(shè)存儲(chǔ)庫正在運(yùn)行!

ZynqberryZero IP 存儲(chǔ)庫

由于 ZynqberryZero 的官方 IP 庫和塊設(shè)計(jì) TCL 腳本尚不可用,我繼續(xù)手動(dòng)升級(jí)它們并將它們附加到該項(xiàng)目。

在繼續(xù) Vivado 項(xiàng)目中的設(shè)計(jì)之前,將下面附帶的 IP 庫復(fù)制到某個(gè)可訪問的位置。我個(gè)人喜歡將這樣的項(xiàng)目特定 IP 庫復(fù)制到我正在使用它們的相應(yīng) Vivado 項(xiàng)目目錄中。如果我使用一個(gè)來創(chuàng)建塊設(shè)計(jì),我也會(huì)將塊設(shè)計(jì) TCL 腳本放入 Vivado 項(xiàng)目目錄中在這種情況下。

將 IP 庫存儲(chǔ)庫和塊設(shè)計(jì) TCL 腳本復(fù)制到項(xiàng)目中:

~$ mkdir -p //docs

~$ cp ./Downloads/zsys.tcl //docs

~$ cp -R ./Downloads/ip_lib //

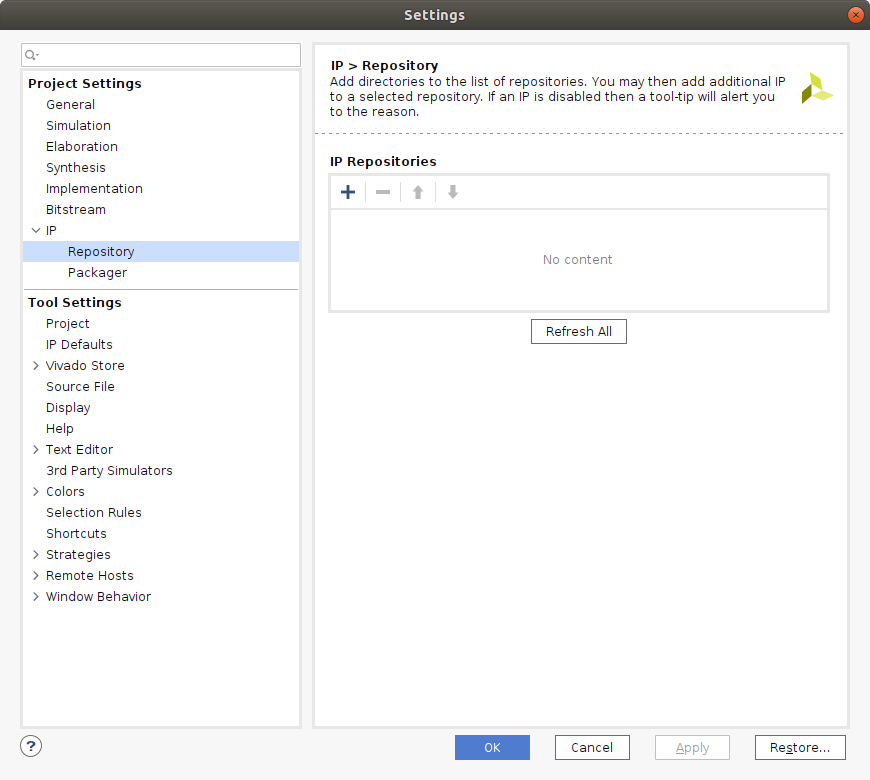

將 IP 庫復(fù)制到 Vivado 工程目錄后,需要將其作為有效的 IP 存儲(chǔ)庫添加到 Vivado 工程設(shè)置中。

在 Vivado 中打開設(shè)置,然后導(dǎo)航到IP下的存儲(chǔ)庫。單擊+按鈕并指向 IP 庫文件夾。

區(qū)塊設(shè)計(jì)

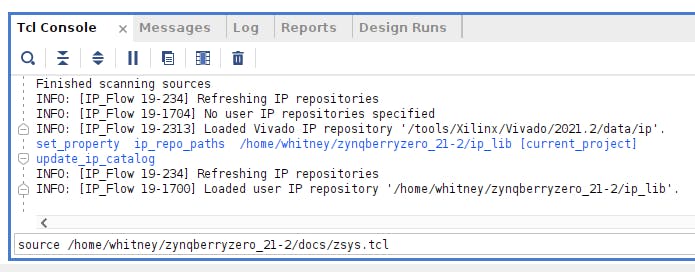

通過從 Vivado 項(xiàng)目的 TCL 控制臺(tái)運(yùn)行以下命令,從 TCL 腳本為 ZynqberryZero 重新創(chuàng)建塊設(shè)計(jì)(從空白的新項(xiàng)目執(zhí)行此操作,在運(yùn)行此腳本之前不要單擊創(chuàng)建塊設(shè)計(jì)):

source //docs/zsys.tcl

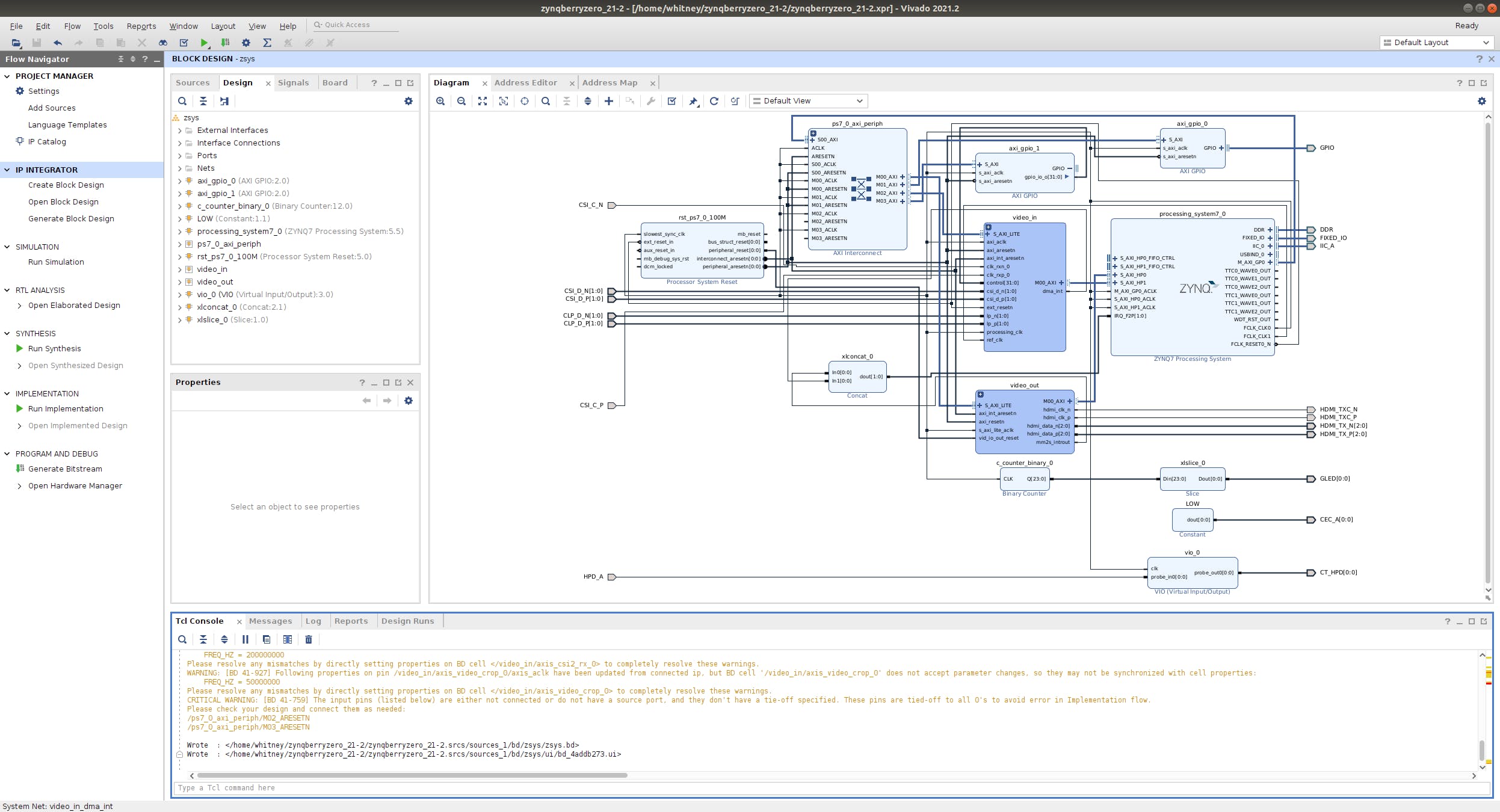

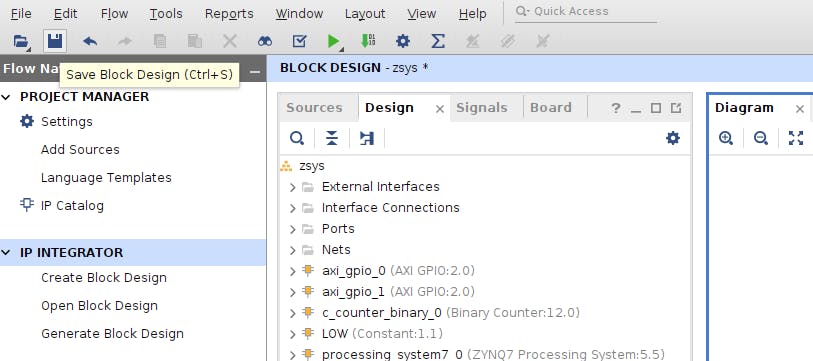

等待設(shè)計(jì)完全填充并發(fā)生所有連接。將有幾個(gè)關(guān)于如何連接重置線的嚴(yán)重警告,但現(xiàn)在可以忽略這些警告。

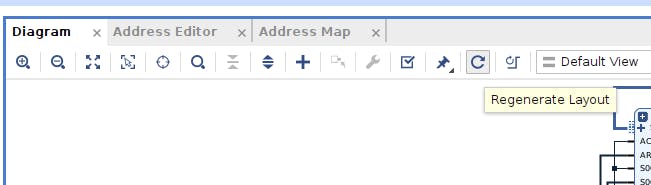

重新生成設(shè)計(jì),使其看起來不那么凌亂:

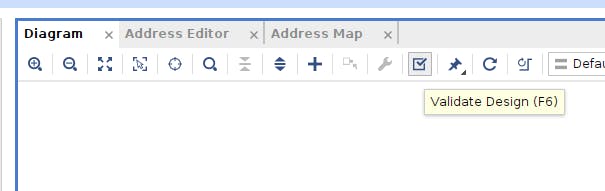

該腳本已經(jīng)運(yùn)行了設(shè)計(jì)驗(yàn)證,但我仍然喜歡手動(dòng)運(yùn)行驗(yàn)證以確保。

保存塊設(shè)計(jì)。

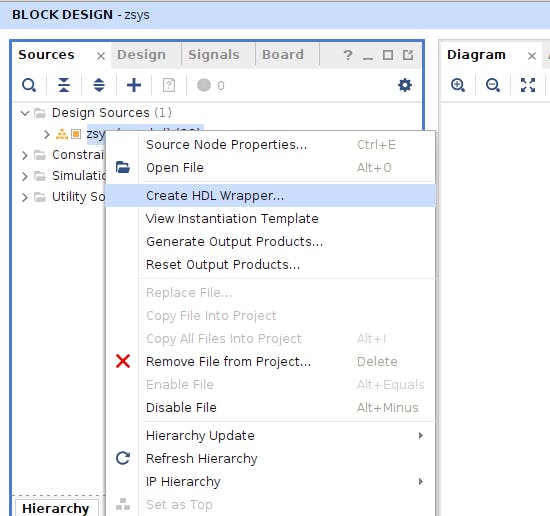

創(chuàng)建 HDL 包裝器以實(shí)例化項(xiàng)目中的模塊設(shè)計(jì)。右鍵單擊Sources選項(xiàng)卡中的模塊設(shè)計(jì)并選擇Create HDL Wrapper...

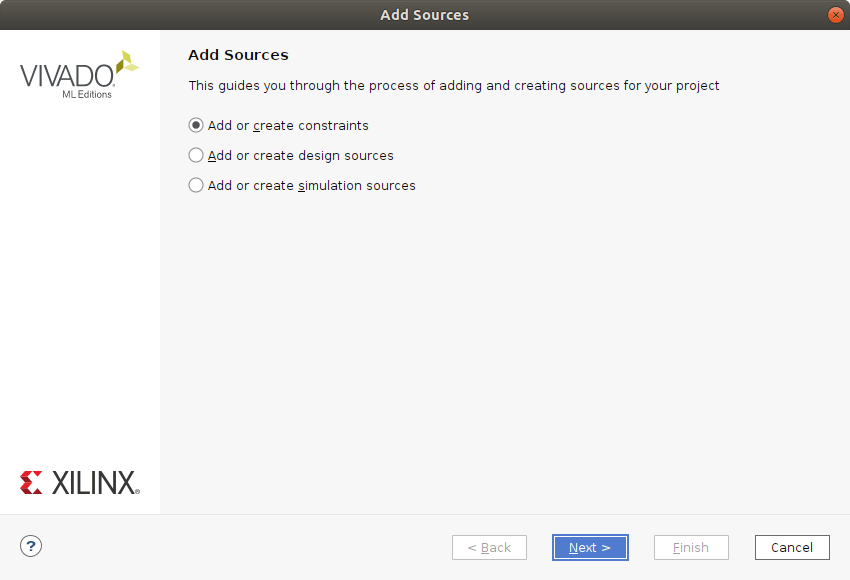

塊設(shè)計(jì)完成且頂層 HDL 包裝器就位后,需要添加設(shè)計(jì)約束以指定信號(hào)映射到 FPGA 上的封裝引腳等內(nèi)容。

在Flow Navigator窗口中,單擊Add Sources 。選擇添加以創(chuàng)建約束,然后選擇添加文件并使用附加到本文的約束文件。確保在單擊Finish之前選擇了Copy constraints files into project選項(xiàng)。

由于存在多個(gè)約束文件,因此需要將一個(gè)約束文件指定為目標(biāo)約束文件,以便 Vivado 知道在需要時(shí)將新約束寫入何處(但所有約束都會(huì)讀入設(shè)計(jì)中)。右鍵單擊Sources選項(xiàng)卡中的vivado_target.xdc約束文件,然后選擇Set as Target Constraint File 。

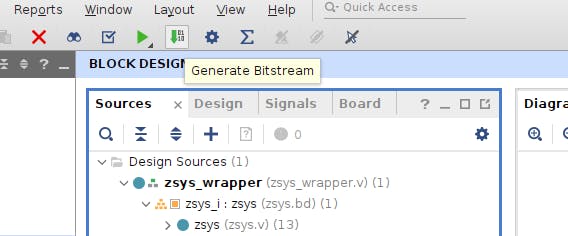

生成比特流

現(xiàn)在 ZynqberryZero 的完整硬件設(shè)計(jì)已經(jīng)到位,是時(shí)候?qū)ζ溥M(jìn)行綜合、布局和布線并生成比特流了。您可以點(diǎn)擊Generate Bitstream ,Vivado 也會(huì)自動(dòng)運(yùn)行綜合和實(shí)現(xiàn)。

成功生成比特流后,導(dǎo)出用于 Vitis 的硬件,為 Zynq SoC 的 ARM 內(nèi)核處理器開發(fā)軟件(是的,會(huì)有一些時(shí)序違規(guī),但我還沒有看到任何問題,并且我仍在努力弄清楚如何修復(fù)它們)。

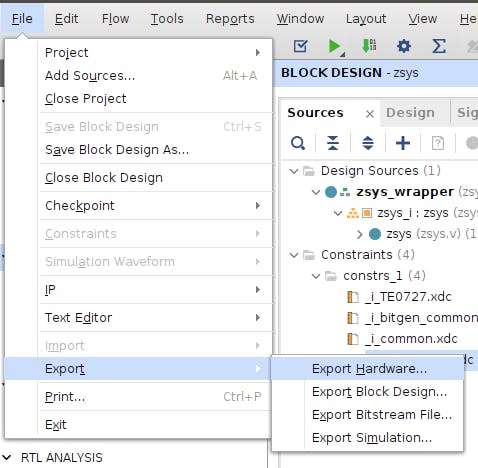

單擊文件>導(dǎo)出>導(dǎo)出硬件...

請(qǐng)務(wù)必選擇Include bitstream選項(xiàng)。我總是將硬件平臺(tái)導(dǎo)出到 Vivado 項(xiàng)目目錄的頂層(默認(rèn)),但您可以選擇您喜歡的任何目錄。

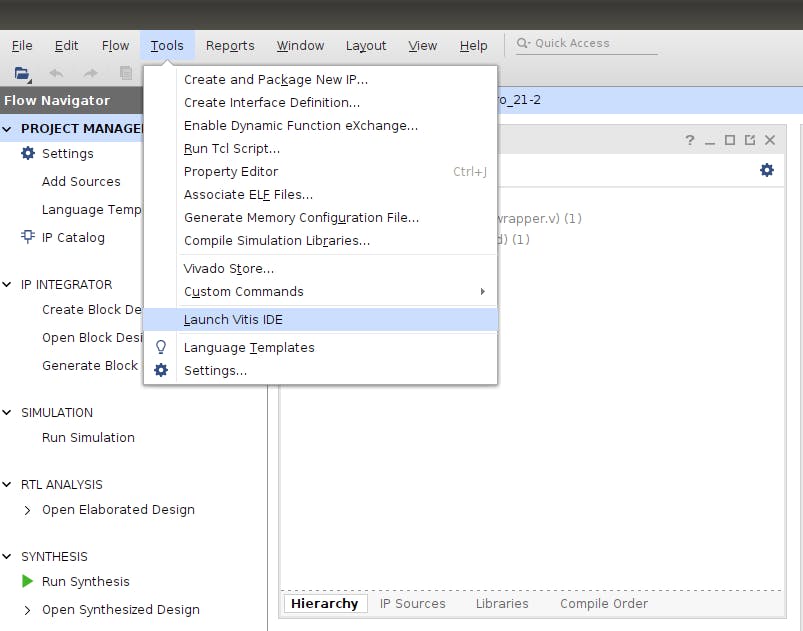

從 Vivado 導(dǎo)出硬件平臺(tái)后,通過在 Vivado 中選擇工具>啟動(dòng) Vitis IDE來啟動(dòng) Vitis 。

同樣,您可以選擇任何所需的目錄來啟動(dòng) Vitis 工作區(qū),但我個(gè)人喜歡在 Vivado 項(xiàng)目目錄的頂層為其創(chuàng)建一個(gè)名為vitis_??workspace的文件夾。

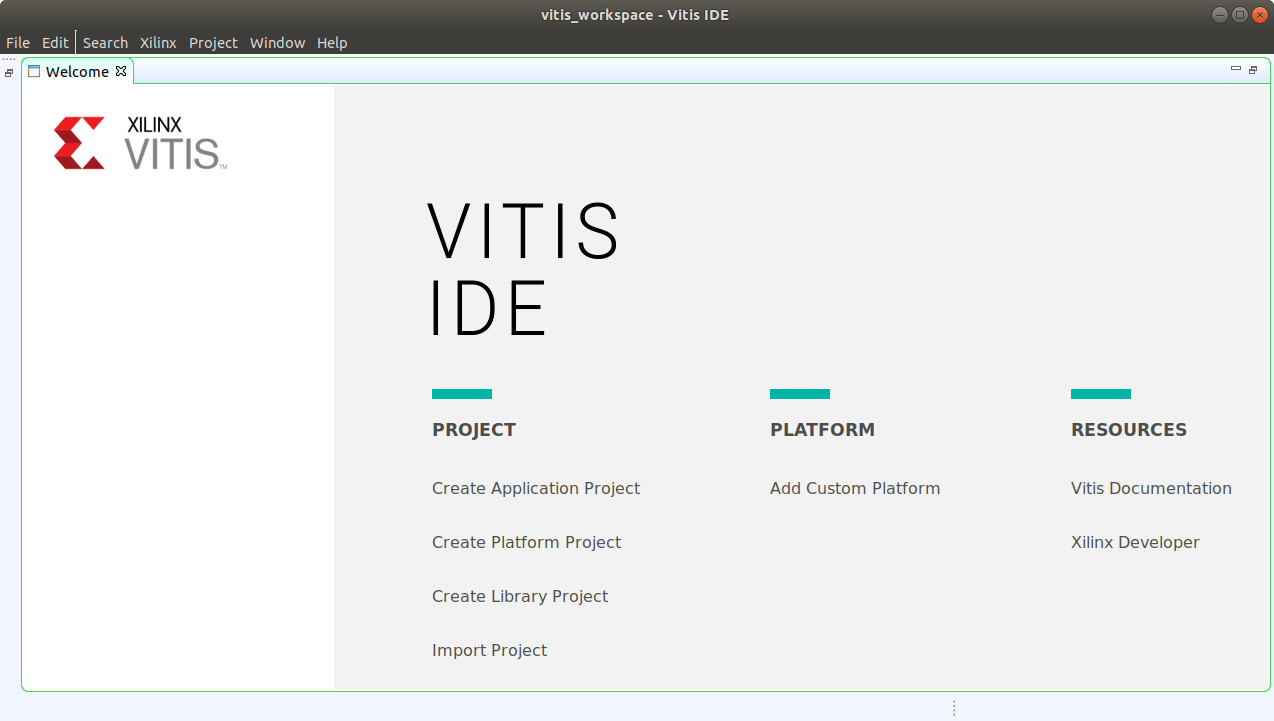

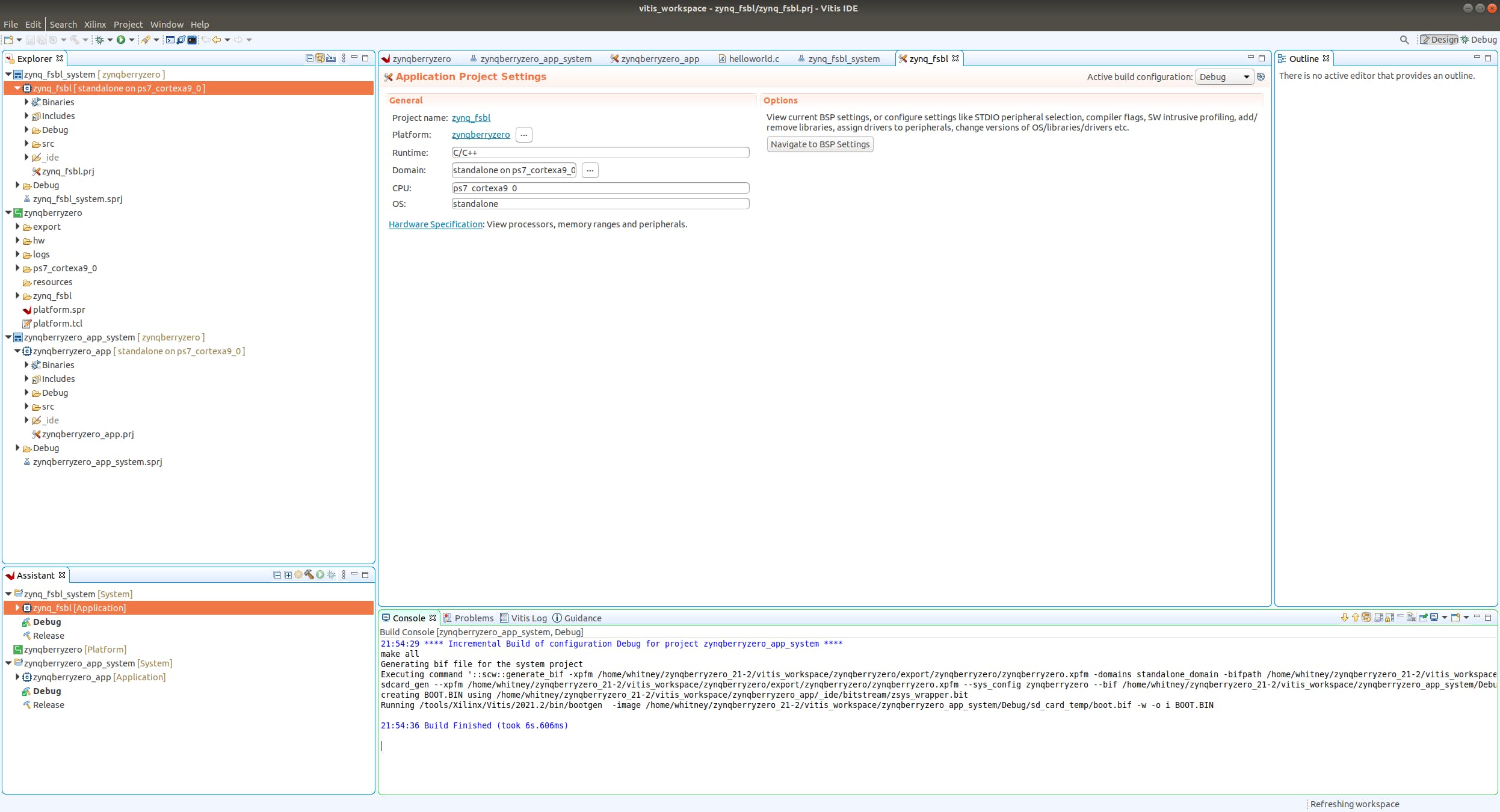

Vitis 平臺(tái)項(xiàng)目

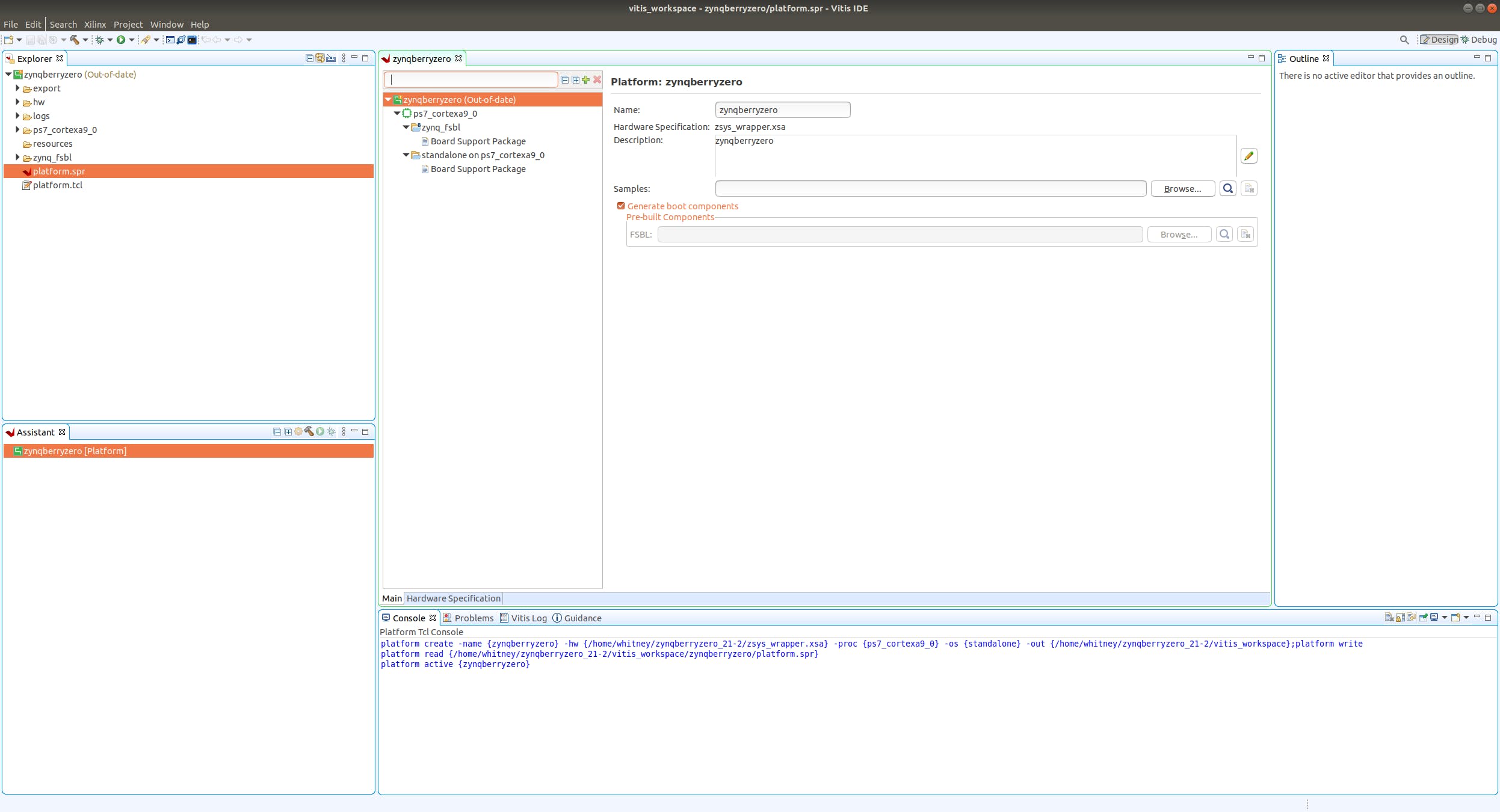

Vitis 啟動(dòng)到新工作區(qū)后,通過選擇 Create Platform Project 創(chuàng)建新的平臺(tái)項(xiàng)目。為其指定所需的名稱,并指定從 Vivado 導(dǎo)出的硬件(XSA 文件)以用于要從中創(chuàng)建的平臺(tái)項(xiàng)目。

在平臺(tái)生成后構(gòu)建平臺(tái)(因?yàn)樗婚_始會(huì)顯示過時(shí))。

Vitis 應(yīng)用項(xiàng)目

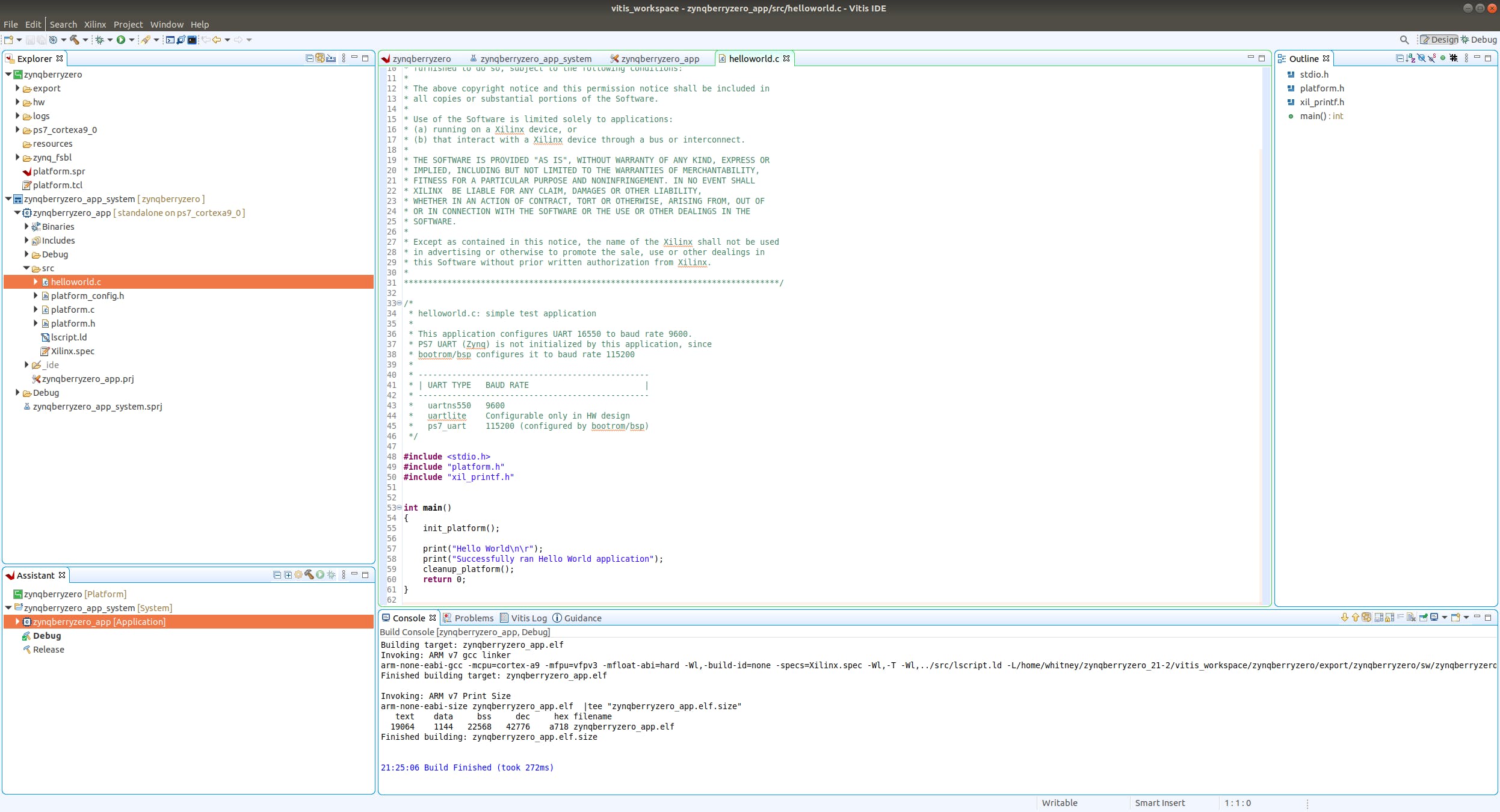

通過平臺(tái)項(xiàng)目準(zhǔn)備好硬件平臺(tái)和 BSP(板級(jí)支持包)后,創(chuàng)建要在其上運(yùn)行的應(yīng)用項(xiàng)目。

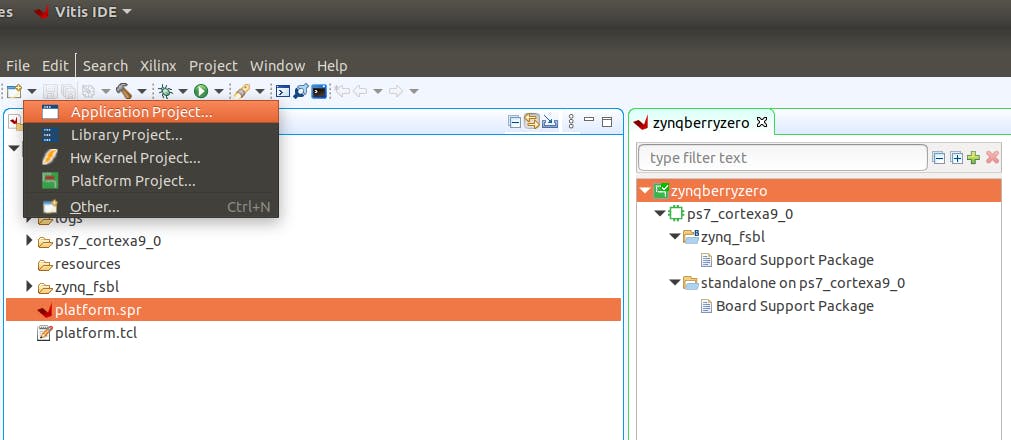

選擇新建>應(yīng)用程序項(xiàng)目...

選擇上一步中由平臺(tái)項(xiàng)目創(chuàng)建的平臺(tái),并為應(yīng)用程序指定所需的名稱。使用Hello World應(yīng)用程序模板。

生成后構(gòu)建應(yīng)用程序。

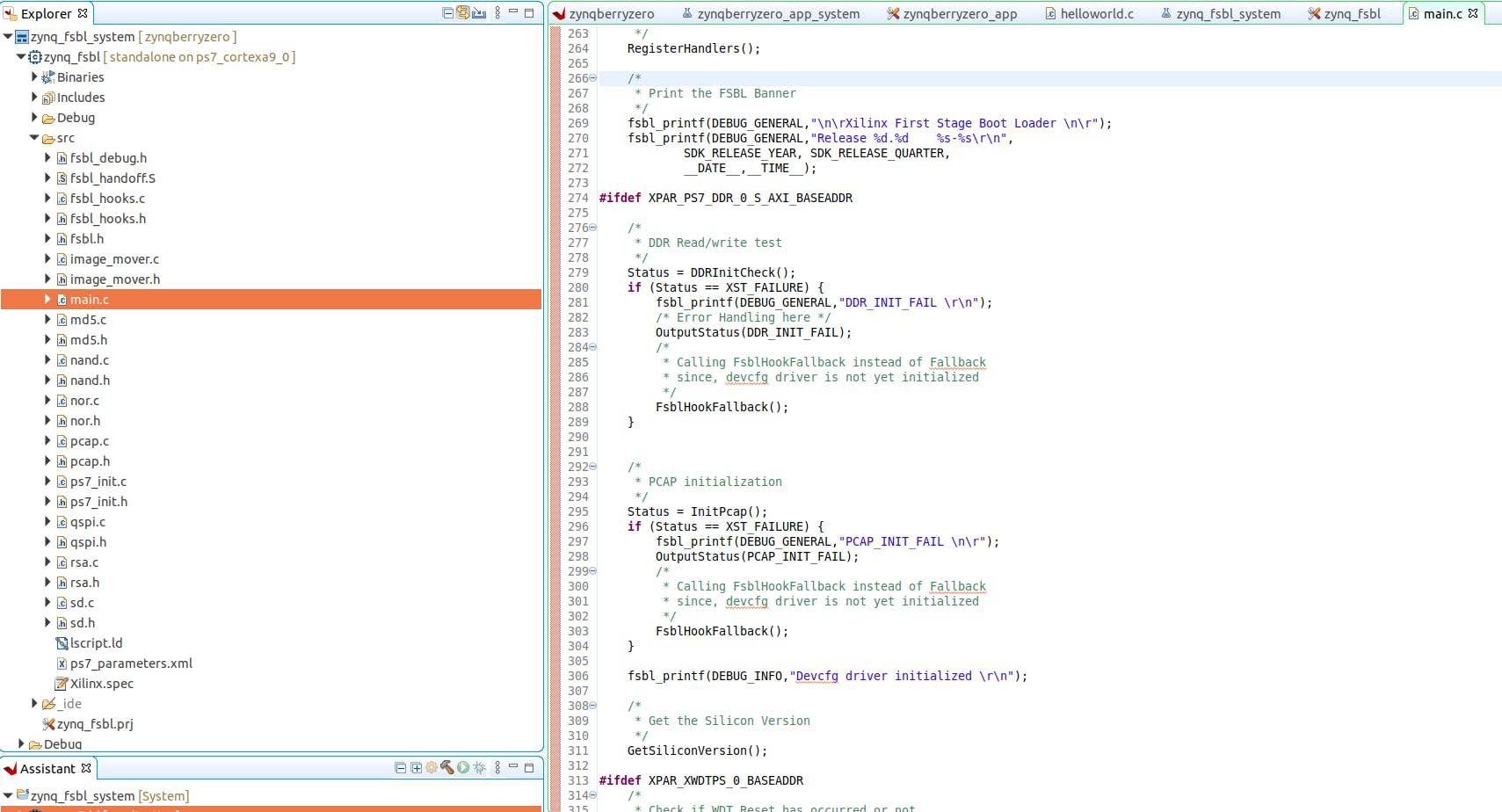

Zynq FSBL 應(yīng)用項(xiàng)目

為了將 Hello World 應(yīng)用程序刷入 ZynqberryZero 的 QSPI 閃存,需要?jiǎng)?chuàng)建和修改 Zynq 第一階段引導(dǎo)加載程序應(yīng)用程序項(xiàng)目以從 JTAG 引導(dǎo)。Zynq 芯片需要從 JTAG 引導(dǎo),以便主機(jī) PC 可以將引導(dǎo)映像編程到 QSPI 閃存上。

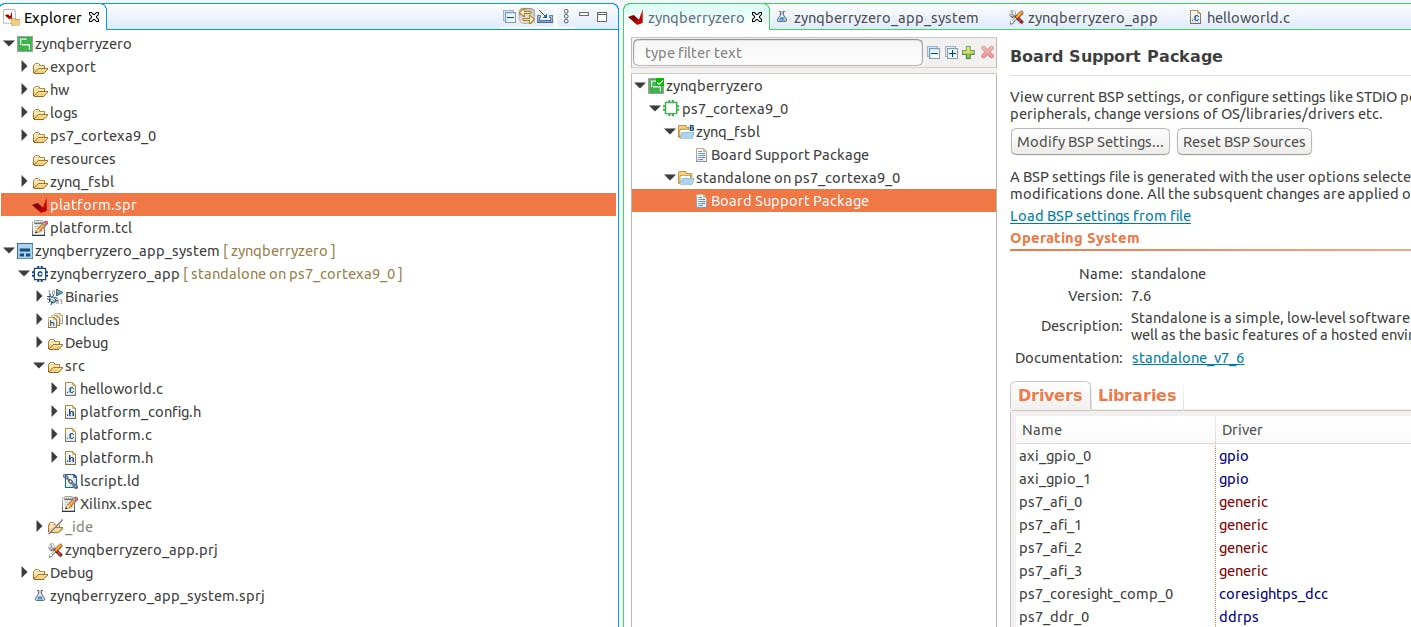

在創(chuàng)建 Zynq FSBL 應(yīng)用程序之前,在平臺(tái)項(xiàng)目的獨(dú)立 BSP 中啟用通用 FAT 文件系統(tǒng)庫 (xilffs)。

從Explorer窗口中選擇 .xpr 文件,然后在 standalone on ps7_cortexa9_0下選擇Board Support Package 。單擊Modify BSP Settings...并選中xilffs旁邊的框。

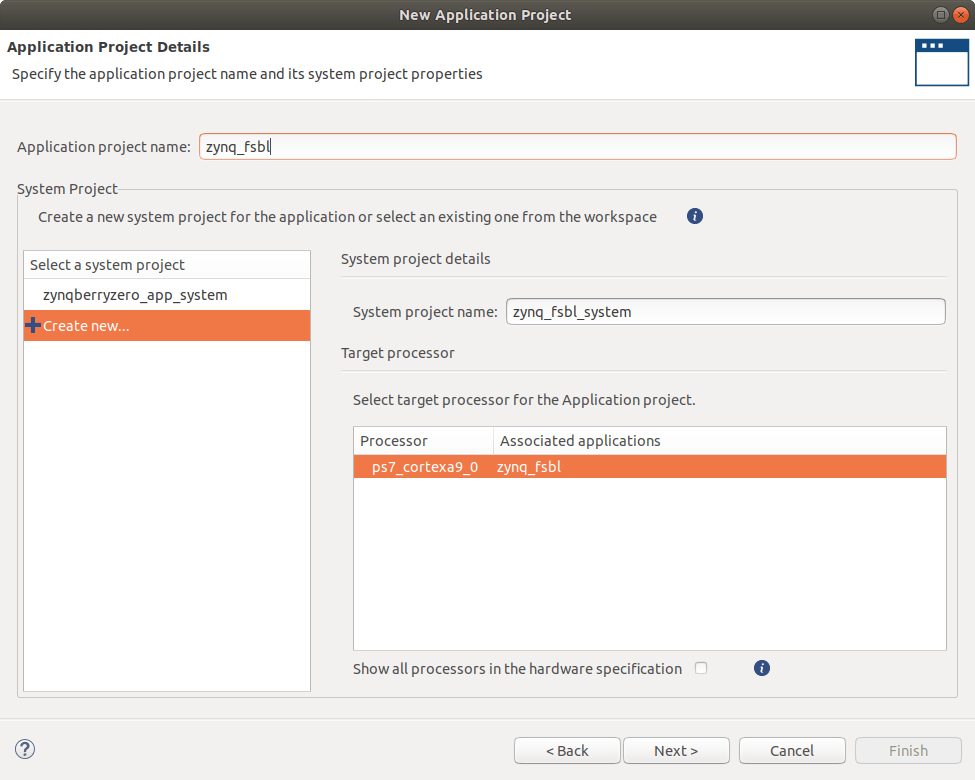

基于Zynq FSBL模板,按照之前的方法再創(chuàng)建一個(gè)應(yīng)用工程:

等待 Zynq FSBL 的應(yīng)用項(xiàng)目生成。

打開 main.c 并將啟動(dòng)模式更新為 JTAG 啟動(dòng)模式并跳過內(nèi)存外設(shè)測(cè)試。

您還可以在下面找到修改后的 main.c。

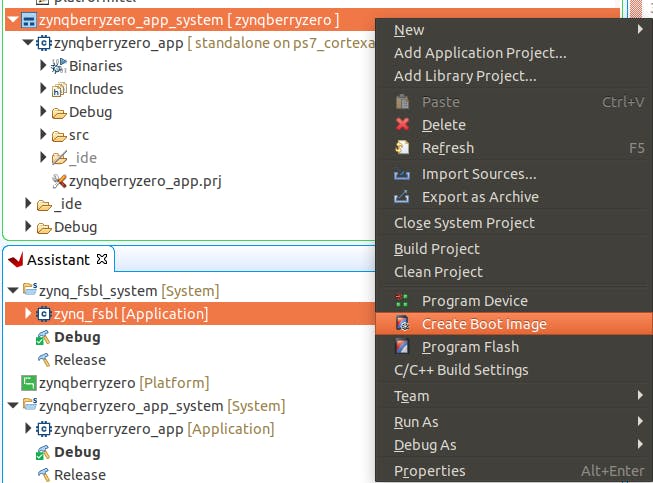

閃存 Zynqberry 零內(nèi)存

通過在資源管理器窗口中右鍵單擊 Hello World 應(yīng)用程序并選擇Create Boot Image來為 ZynqberryZero 創(chuàng)建啟動(dòng)映像。由于從 Hello World 應(yīng)用程序的右鍵單擊菜單中選擇了創(chuàng)建啟動(dòng)映像選項(xiàng),因此將自動(dòng)生成啟動(dòng)分區(qū)和文件路徑。

您可以看到 FPGA 比特流、Hello World ELF 和 QSPI Zynq FSBL 是構(gòu)成 ZynqberryZero 的啟動(dòng)二進(jìn)制文件 (BOOT.BIN) 的啟動(dòng)分區(qū)。

單擊創(chuàng)建圖像。

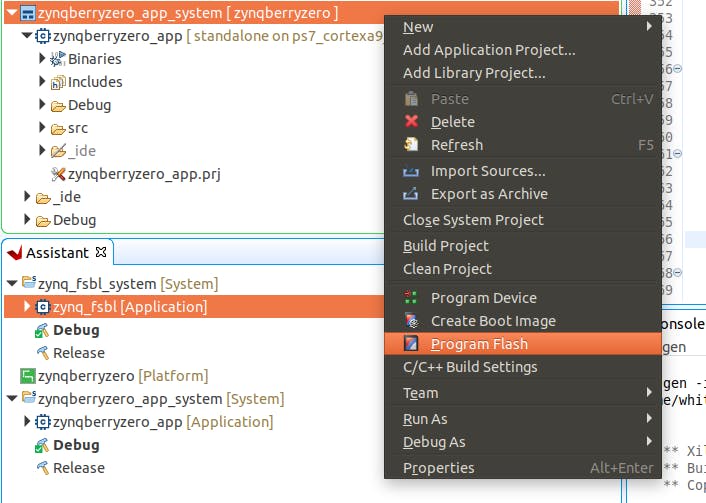

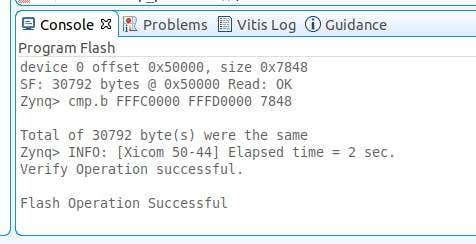

通過再次右鍵單擊資源管理器窗口中的 Hello World 應(yīng)用程序并選擇Program Flash來對(duì) ZynqberryZero 的 QSPI 閃存進(jìn)行編程。

使用剛剛創(chuàng)建的引導(dǎo)二進(jìn)制文件 (BOOT.BIN) 作為映像文件。設(shè)置Offset為0x0,Flash Type為qspi-x4-single,使用JTAG Zynq FSBL的ELF文件作為Init File 。還要選中Verify after flash選項(xiàng)。

?

- Vivado 2021.1中的Kria KV260入門

- 《Python編程入門》.pdf 0次下載

- MATLAB使用教程-初步入門大全.PPT 0次下載

- GitHub入門與實(shí)踐 0次下載

- Verilog HDL入門教程.pdf 115次下載

- Kicad5.1.5中文入門教程電子版下載 0次下載

- 松下PLC入門基礎(chǔ)培訓(xùn)課件下載 125次下載

- MATLAB入門教程電子版下載 0次下載

- Xilinx_Vivado_zynq7000入門筆記 71次下載

- 什么是Vivado?資料下載

- Vivado設(shè)計(jì)流程指導(dǎo)說明 28次下載

- Vivado設(shè)計(jì)流程指導(dǎo)手冊(cè) 50次下載

- Vivado中xilinx_BRAM IP核使用

- PSIM仿真入門學(xué)習(xí)-課件下載 186次下載

- ZYBO入門指導(dǎo)手冊(cè)(一)v1.0——Vivado 21次下載

- Vivado Schematic中的實(shí)線和虛線有什么區(qū)別? 956次閱讀

- 在Vivado中實(shí)現(xiàn)ECO功能 2250次閱讀

- Tcl在Vivado中的應(yīng)用 1288次閱讀

- Vivado里如何手動(dòng)調(diào)整編譯順序 3470次閱讀

- Vivado中的Elaborate是做什么的? 1277次閱讀

- Vivado在FPGA設(shè)計(jì)中的優(yōu)勢(shì) 1508次閱讀

- 如何升級(jí)Vivado工程腳本 1709次閱讀

- xilinx Vivado工具使用技巧 3934次閱讀

- Vivado軟件仿真DDS核的過程中應(yīng)該注意的問題 9656次閱讀

- 基于linux系統(tǒng)實(shí)現(xiàn)的vivado調(diào)用VCS仿真教程 1.1w次閱讀

- Vivado 2017.1和Vivado 2016.4性能對(duì)比分析 9977次閱讀

- Vivado獲取License的步驟教程 5.9w次閱讀

- Vivado使用誤區(qū)與進(jìn)階——在Vivado中實(shí)現(xiàn)ECO功能 5242次閱讀

- Tcl在Vivado中的基礎(chǔ)應(yīng)用 4831次閱讀

- ISE約束導(dǎo)入vivado總共分幾步 8733次閱讀

下載排行

本周

- 1山景DSP芯片AP8248A2數(shù)據(jù)手冊(cè)

- 1.06 MB | 532次下載 | 免費(fèi)

- 2RK3399完整板原理圖(支持平板,盒子VR)

- 3.28 MB | 339次下載 | 免費(fèi)

- 3TC358743XBG評(píng)估板參考手冊(cè)

- 1.36 MB | 330次下載 | 免費(fèi)

- 4DFM軟件使用教程

- 0.84 MB | 295次下載 | 免費(fèi)

- 5元宇宙深度解析—未來的未來-風(fēng)口還是泡沫

- 6.40 MB | 227次下載 | 免費(fèi)

- 6迪文DGUS開發(fā)指南

- 31.67 MB | 194次下載 | 免費(fèi)

- 7元宇宙底層硬件系列報(bào)告

- 13.42 MB | 182次下載 | 免費(fèi)

- 8FP5207XR-G1中文應(yīng)用手冊(cè)

- 1.09 MB | 178次下載 | 免費(fèi)

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費(fèi)

- 2555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33566次下載 | 免費(fèi)

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費(fèi)

- 4開關(guān)電源設(shè)計(jì)實(shí)例指南

- 未知 | 21549次下載 | 免費(fèi)

- 5電氣工程師手冊(cè)免費(fèi)下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費(fèi)

- 6數(shù)字電路基礎(chǔ)pdf(下載)

- 未知 | 13750次下載 | 免費(fèi)

- 7電子制作實(shí)例集錦 下載

- 未知 | 8113次下載 | 免費(fèi)

- 8《LED驅(qū)動(dòng)電路設(shè)計(jì)》 溫德爾著

- 0.00 MB | 6656次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費(fèi)

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537798次下載 | 免費(fèi)

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420027次下載 | 免費(fèi)

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費(fèi)

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費(fèi)

- 6電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191187次下載 | 免費(fèi)

- 7十天學(xué)會(huì)AVR單片機(jī)與C語言視頻教程 下載

- 158M | 183279次下載 | 免費(fèi)

- 8proe5.0野火版下載(中文版免費(fèi)下載)

- 未知 | 138040次下載 | 免費(fèi)

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評(píng)論