完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > 先進(jìn)封裝

先進(jìn)封裝可以提高加工效率,提高設(shè)計(jì)效率,減少設(shè)計(jì)成本,降低芯片尺寸等優(yōu)勢(shì)。半導(dǎo)體器件有許多封裝形式,半導(dǎo)體封裝經(jīng)歷了多次重大革新,芯片級(jí)封裝、系統(tǒng)級(jí)封裝技術(shù)指標(biāo)一代比一代先進(jìn)。現(xiàn)在涌現(xiàn)了倒裝類(FlipChip,Bumping),晶圓級(jí)封裝(WLCSP,F(xiàn)OWLP,PLP),2.5D封裝等。

文章:413個(gè) 瀏覽:266次 帖子:0個(gè)

先進(jìn)封裝之TSV、TGV技術(shù)制作工藝和原理

摩爾定律指引集成電路不斷發(fā)展。摩爾定律指出:“集成電路芯片上所集成的電路的數(shù)目,每隔18-24個(gè)月就翻一倍;微處理器的性能提高一倍,或價(jià)格下降一半。

CoWoS先進(jìn)封裝技術(shù)介紹 CoWoS-R技術(shù)主要特點(diǎn)分析

CoWoS-R 技術(shù)的主要特點(diǎn)包括: 1)RDL interposer 由多達(dá) 6L 銅層組成,用于最小間距為 4um 間距(2um 線寬/間距)的布線...

CSP封裝(Chip Scale Package)是指芯片級(jí)封裝,其封裝尺寸和芯片核心尺寸基本相同,一般芯片面積與封裝面積的比例約在1:1.1。CSP封...

先進(jìn)封裝三種技術(shù):IPD/Chiplet/RDL技術(shù)

工藝選擇的靈活性。芯片設(shè)計(jì)中,并不是最新工藝就最合適。目前單硅SoC,成本又高,風(fēng)險(xiǎn)還大。像專用加速功能和模擬設(shè)計(jì),采用Chiplet,設(shè)計(jì)時(shí)就有更多選擇。

2023-03-08 標(biāo)簽:芯片設(shè)計(jì)封裝技術(shù)晶圓工藝 1.3萬(wàn) 0

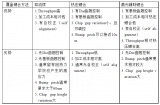

傳統(tǒng)封裝 Vs.先進(jìn)封裝的區(qū)別及優(yōu)勢(shì)

集成電路封裝是指將制備合格芯片、元件等裝配到載體上,采用適當(dāng)連接技術(shù)形成電氣連接,安裝外殼,構(gòu)成有效組件的整個(gè)過(guò)程,封裝主要起著安放、固定、密封、保護(hù)芯...

另外一個(gè)將TGV填實(shí)的方案是將金屬導(dǎo)電膠進(jìn)行TGV填實(shí)。利用金屬導(dǎo)電膠的優(yōu)點(diǎn)是固化后導(dǎo)電通孔的熱膨脹系數(shù)可以調(diào)節(jié),使其接近基材,避免了因CTE不匹配造成的失效。

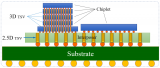

2.5D 封裝是在2D封裝結(jié)構(gòu)的基礎(chǔ)上,在芯片和封裝載體之間加入了一個(gè)硅中介轉(zhuǎn)接層,該中介轉(zhuǎn)接層上利用硅通孔 (Through Silicon Via,...

Chiplet技術(shù)是一種利用先進(jìn)封裝方法將不同工藝/功能的芯片進(jìn)行異質(zhì)集成的技術(shù)。這種技術(shù)設(shè)計(jì)的核心思想是先分后合,即先將單芯片中的功能塊拆分出來(lái),再通...

隨著晶圓代工制程不斷縮小,摩爾定律逼近極限,先進(jìn)封裝是后摩爾時(shí)代的必然選擇。其中,利用高端封裝融合最新和成熟節(jié)點(diǎn),采用系統(tǒng)封裝(SiP)和基于小芯片的方...

何謂先進(jìn)封裝/Chiplet?先進(jìn)封裝/Chiplet的意義

先進(jìn)封裝/Chiplet可以釋放一部分先進(jìn)制程產(chǎn)能,使之用于更有急迫需求的場(chǎng)景。從上文分析可見(jiàn),通過(guò)降制程和芯片堆疊,在一些沒(méi)有功耗限制和體積空間限制、...

2023-01-31 標(biāo)簽:中國(guó)半導(dǎo)體chiplet先進(jìn)封裝 4229 0

隨著chatGPT橫空出世,生成式AI紅遍全球,帶動(dòng)AI芯片的需求強(qiáng)勁,英偉達(dá)(NVIDIA)的H100、A100全部由臺(tái)積電代工,并使用臺(tái)積電的CoW...

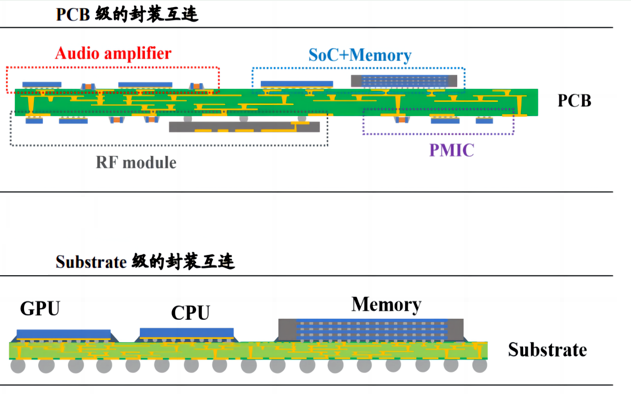

基于XY平面延伸和Z軸延伸的先進(jìn)封裝技術(shù)

無(wú)論是采用Fan-in還是Fan-out,WLP晶圓級(jí)封裝和PCB的連接都是采用倒裝芯片形式,芯片有源面朝下對(duì)著印刷電路板,可以實(shí)現(xiàn)最短的電路徑,這也保...

先進(jìn)封裝(Advanced Packaging)是一種新型的電子封裝技術(shù),它旨在通過(guò)創(chuàng)新的技術(shù)手段,將多個(gè)芯片或其他電子元器件以更高的集成度、更小的尺寸...

先進(jìn)封裝技術(shù)以SiP、WLP、2.5D/3D為三大發(fā)展重點(diǎn)。先進(jìn)封裝核心技術(shù)包括Bumping凸點(diǎn)、RDL重布線、硅中介層和TSV通孔等,依托這些技術(shù)的...

2023-09-28 標(biāo)簽:晶圓芯片設(shè)計(jì)SiP技術(shù) 3483 0

什么是先進(jìn)封裝?先進(jìn)封裝和傳統(tǒng)封裝區(qū)別 先進(jìn)封裝工藝流程

半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類可分為引腳插入型、表面貼裝型和高級(jí)封裝三類。從DIP、SOP、QFP、PGA、BGA到CSP再到S...

2023-08-11 標(biāo)簽:三極管PCB板芯片設(shè)計(jì) 3437 0

熱壓鍵合工藝的基本原理與傳統(tǒng)擴(kuò)散焊工藝相同,即上下芯片的Cu 凸點(diǎn)對(duì)中后直接接觸,其實(shí)現(xiàn)原子擴(kuò)散鍵合的主要影響參數(shù)是溫度、壓力、時(shí)間. 由于電鍍后的Cu...

最近,在先進(jìn)封裝領(lǐng)域又出現(xiàn)了一個(gè)新的名詞“3.5D封裝”,以前聽(tīng)?wèi)T了2.5D和3D封裝,3.5D封裝又有什么新的特點(diǎn)呢?還是僅僅是一個(gè)吸引關(guān)注度的噱頭?

BumpMetrologysystem—BOKI_1000在半導(dǎo)體行業(yè)中,Bump、RDL、TSV、Wafer合稱先進(jìn)封裝的四要素,其中Bump起著界面...

2023-09-06 標(biāo)簽:封裝測(cè)量?jī)x器先進(jìn)封裝 3186 0

先進(jìn)封裝增速高于整體封裝,將成為全球封裝市場(chǎng)主要增量。根據(jù)Yole的數(shù)據(jù),全球封裝市場(chǎng)規(guī)模穩(wěn)步增長(zhǎng),2021 年全球封裝 市場(chǎng)規(guī)模 約達(dá) 777 億美元...

先進(jìn)封裝中凸點(diǎn)技術(shù)的研究進(jìn)展

隨著異構(gòu)集成模塊功能和特征尺寸的不斷增加,三維集成技術(shù)應(yīng)運(yùn)而生。凸點(diǎn)之間的互連 是實(shí)現(xiàn)芯片三維疊層的關(guān)鍵,制備出高可靠性的微凸點(diǎn)對(duì)微電子封裝技術(shù)的進(jìn)一步...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |