完善資料讓更多小伙伴認識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > 賽靈思

提供賽靈思公司最新的技術(shù)和產(chǎn)品信息,工程師最喜歡的賽靈思技術(shù)社區(qū)

文章:1697個 瀏覽:131410次 帖子:56個

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載12:Spartan

Spartan-6 器件最多包含6 個CMT,12 個PLL。PLL 的主要用途是作為頻率合成器,產(chǎn)生更寬范圍的頻率輸出,在與CMT 中的DCM 連接時...

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載11:Spartan

Spartan-6 CMT是一個靈活、高性能的時鐘管理模塊。它位于芯片中央、垂直的全局時鐘網(wǎng)絡(luò)旁。如圖2-17所示,它包含一個PLL和兩個DCM。

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載10:Spartan

Spartan-6的時鐘布線網(wǎng)絡(luò)包括由BUFGMUX驅(qū)動的全局時鐘網(wǎng)絡(luò)和由I/O時鐘緩沖器(BUFIO2)、PLL時鐘緩沖器(BUFPLL)驅(qū)動的I/O...

在系統(tǒng)設(shè)計的初期我們不僅要考慮要實現(xiàn)的功能,性能,可操作性等方面,還有一方面便是實地的使用環(huán)境,如高溫,高濕等惡劣的條件給系統(tǒng)設(shè)計提出了新的要求

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載40:Spartan

最大化【Package Pins】,如圖10-45 所示, 和按鈕配合,完成對器件引腳的排序,如圖中我們將所有VREF 引腳排在一起,選中所有VREF ...

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載39:Spartan

下面通過一個簡單的實例介紹如何創(chuàng)建PlanAhead項目,進行I/O規(guī)劃。

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載38:Spartan

PlanAhead允許導(dǎo)入多種不同類型的源文件,包括HDL和NGC核。在RTL編輯器中可以打開、編輯、開發(fā)RTL源文件。下面我們介紹【Sources】源...

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載37:Spartan

這里介紹如何用PlanAhead進行RTL代碼開發(fā)與分析。需要說明一點,本章所用的所有實例都可以在PlanAhead的安裝目錄E:\Xilinx\11....

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載36:Spartan

PlanAhead工具是Xilinx提供的一個集成的、可視化的FPGA設(shè)計工具,它可以被應(yīng)用于FPGA設(shè)計過程中的不同階段,常見的應(yīng)用包括用PlanAh...

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載34:Spartan

ChipScope Pro內(nèi)核插入器的文件后綴名為cdc。在ISE工程中可以創(chuàng)建一個新的cdc程序,也可以在實現(xiàn)流程中激活內(nèi)核插入器。

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載35:Spartan

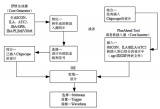

ChipScope Pro 分析工具(Analyzer tool)直接與ICON、ILA、IBA、VIO及IBERT核相連,用戶可以實時地創(chuàng)建或修改觸發(fā)條件。

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載33:Spartan

下面通過一個簡單8位計數(shù)器的例子,了解如何在工程中添加ChipScope Pro內(nèi)核生成器的各個IP核,對FPGA內(nèi)部節(jié)點和邏輯進行觀測。在該實例中,我...

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載32:Spartan

雙擊【Xilinx Core Generator】,打開現(xiàn)有的IP核工程項目或者創(chuàng)建一個新的IP核工程。

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載31:Spartan

雙擊【Xilinx Core Generator】,打開現(xiàn)有的IP核工程項目或者創(chuàng)建一個新的IP核工程。【View by function】→【Debu...

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載30:Spartan

Xilinx針對不同類型的調(diào)試IP核,提供了不同的核生成器。本節(jié)重點介紹Xilinx Core Generator Tool(Xilinx IP核生成器...

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載29:Spartan

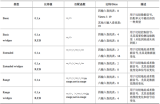

ChipScope Pro 提供了多種不同功能的調(diào)試內(nèi)核,通常分成三類:邏輯調(diào)試內(nèi)核、誤比特率測試核和集成總線分析核。用戶根據(jù)系統(tǒng)的調(diào)試要求,應(yīng)用不同的...

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載28:Spartan

FPGA和PCB設(shè)計人員保留一定數(shù)量FPGA引腳作為測試引腳,F(xiàn)PGA設(shè)計者在編寫FPGA代碼時,將需要觀察的FPGA內(nèi)部信號定義為模塊的輸出,在綜合實...

Xilinx可編程邏輯器件設(shè)計與開發(fā)(基礎(chǔ)篇)連載41:Spartan

設(shè)計者可以在【Clock Regions】窗口、【I/O Ports】窗口或者【Package Pins】窗口選擇一個或多個對象,或者單擊按鈕取消所有選...

最近自己做了一塊FPGA板子,不慎將PROM的兩根引腳連錯,導(dǎo)致在配置時無法正確識別PROM的型號,顛三倒四地排除了一個星期問題最終幸運解決。之后感嘆自...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |