完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > 邏輯

文章:116個(gè) 瀏覽:29464次 帖子:49個(gè)

本文主要介紹了cd4069發(fā)光邏輯顯示電路圖及原理,另外還介紹了CD4069制作的收音機(jī)電路、CD4069組成的電容感應(yīng)式控制電路及組成的逆變器電路。

邏輯或功能功能表明如果任何一個(gè)“OR”事件為T(mén)RUE,則輸出操作將變?yōu)門(mén)RUE,但它們發(fā)生的順序并不重要,因?yàn)樗粫?huì)影響最終結(jié)果。

邏輯與門(mén)是一種數(shù)字邏輯電路,只有當(dāng)所有輸入都為高電平時(shí),其輸出才會(huì)變?yōu)楦唠娖街吝壿嬰娖綌?shù)字邏輯與門(mén)的輸出狀態(tài)只有當(dāng)ANY的輸入處于邏輯電平“0”時(shí),才會(huì)...

VLOOKUP函數(shù)是Excel中最常用的函數(shù)之一,它用于在一列或一行中查找某個(gè)值,并返回相應(yīng)的結(jié)果。本文將以詳盡、詳實(shí)、細(xì)致的方式介紹VLOOKUP函數(shù)...

邏輯與功能輸出僅在其所有輸入均為真時(shí)才為真,否則輸出為假,在1854年,喬治布爾對(duì)基于簡(jiǎn)化版“群”或“集合”理論的“思想規(guī)律”,以及布爾代數(shù)的開(kāi)發(fā)。

移位寄存器用于數(shù)據(jù)存儲(chǔ)或數(shù)據(jù)移動(dòng),因此通常用于計(jì)算器內(nèi)部或計(jì)算機(jī)在將數(shù)據(jù)添加到一起之前存儲(chǔ)數(shù)據(jù),例如兩個(gè)二進(jìn)制數(shù),或者將數(shù)據(jù)從串行轉(zhuǎn)換為并行或并行轉(zhuǎn)換為...

2019-06-26 標(biāo)簽:寄存器數(shù)據(jù)二進(jìn)制 9910 0

內(nèi)網(wǎng)安全管理有哪些隱患,應(yīng)如何解決

內(nèi)網(wǎng)安全架構(gòu)中,存在三個(gè)邏輯組件,分別是:終端代理程序、準(zhǔn)入控制點(diǎn)(也稱為策略強(qiáng)制點(diǎn))、策略決策點(diǎn)。其中,準(zhǔn)入控制點(diǎn)是整個(gè)體系的關(guān)鍵,承擔(dān)著與后臺(tái)策略決...

順序脈沖發(fā)生器-三態(tài)邏輯和微機(jī)總線接口立即下載

類(lèi)別:信號(hào)處理電路 2008-05-27 標(biāo)簽:微機(jī)邏輯三態(tài) 1264 0

CMOS邏輯門(mén)電路 CMOS邏輯門(mén)電路是在TTL電路問(wèn)世之后 ,所開(kāi)發(fā)出的第二種廣泛應(yīng)用的數(shù)字集成器件,從發(fā)展趨勢(shì)來(lái)看,由于制造工藝的改進(jìn),CMO...

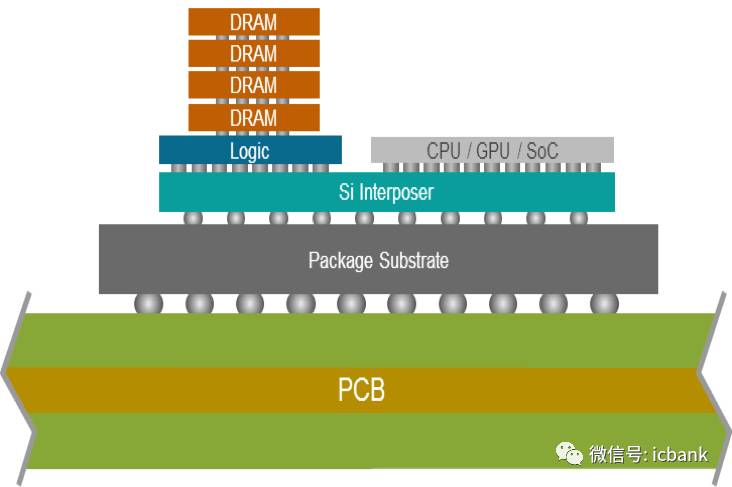

簡(jiǎn)要解析先進(jìn)封裝的優(yōu)點(diǎn)和缺陷

為了避免這些問(wèn)題,一些設(shè)計(jì)團(tuán)隊(duì)已經(jīng)開(kāi)始關(guān)注在系統(tǒng)層面上創(chuàng)造前期設(shè)計(jì)原型——基本上就是創(chuàng)造整個(gè)設(shè)計(jì)的數(shù)字模型。這讓他們可以從頂部 die 一直到 pack...

2019-09-05 標(biāo)簽:半導(dǎo)體數(shù)據(jù)邏輯 1.2萬(wàn) 0

如果你和我一樣,可能今天至少有一次希望時(shí)間停下來(lái),讓你可以來(lái)思考再去做事。對(duì)我來(lái)說(shuō),這發(fā)生在第三杯咖啡之前。昨天,則是凌晨2點(diǎn)在Netflix按下“游戲...

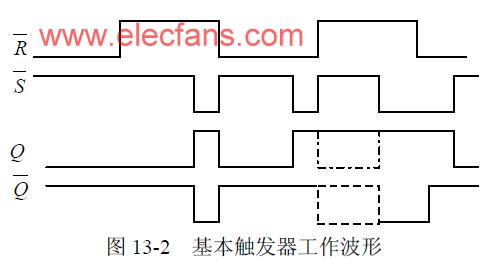

基本觸發(fā)器的邏輯結(jié)構(gòu)如圖13-1所示。它可由兩個(gè)與非門(mén)交叉耦合構(gòu)成,圖13-1(a)是其邏輯電路圖和邏輯符號(hào),也可以由兩個(gè)或非門(mén)交叉耦合構(gòu)成,如圖13-...

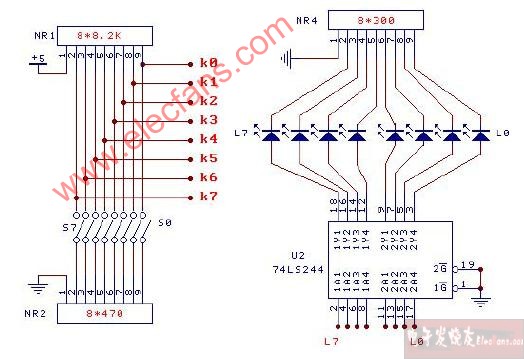

邏輯電平開(kāi)關(guān)電路如圖所示實(shí)驗(yàn)臺(tái)右下方設(shè)有8個(gè)開(kāi)關(guān)K7~K0,開(kāi)關(guān)撥到“1”位置時(shí)開(kāi)關(guān)斷開(kāi),輸出高電平。向下打到“0”位置時(shí)開(kāi)關(guān)接通,輸出低電平。電路中

2009-03-25 標(biāo)簽:邏輯 6453 0

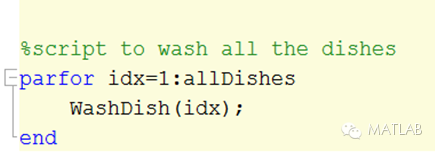

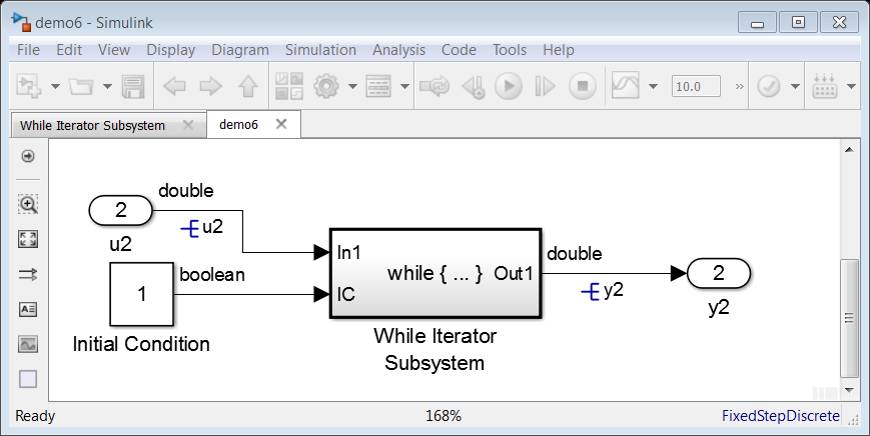

關(guān)于實(shí)現(xiàn)邏輯循環(huán)的方法分析和介紹

生成代碼,如下圖。圖中的func函數(shù)就是框圖func子系統(tǒng)所生成的函數(shù)。內(nèi)部做了一些更新flag的計(jì)算。另外可以看到累加框圖生成的代碼:y2 += u2。

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹(shù)莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |