完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > Verilog HDL

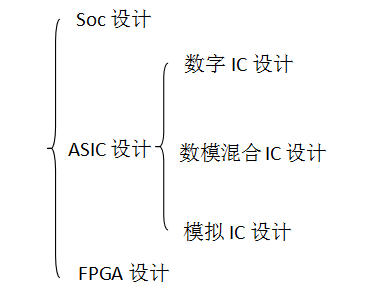

Verilog HDL是一種硬件描述語言(HDL:Hardware Description Language),以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。

Verilog HDL是一種硬件描述語言(HDL:Hardware Description Language),以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。 Verilog HDL和VHDL是世界上最流行的兩種硬件描述語言,都是在20世紀80年代中期開發出來的。前者由Gateway Design Automation公司(該公司于1989年被Cadence公司收購)開發。兩種HDL均為IEEE標準。

Verilog HDL是一種硬件描述語言(HDL:Hardware Description Language),以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。 Verilog HDL和VHDL是世界上最流行的兩種硬件描述語言,都是在20世紀80年代中期開發出來的。前者由Gateway Design Automation公司(該公司于1989年被Cadence公司收購)開發。兩種HDL均為IEEE標準。

以模塊為基礎的設計

描述復雜的硬件電路,設計人員總是將復雜的功能劃分為簡單的功能,模塊是提供每個簡單功能的基本結構。設計人員可以采取“自頂向下”的思路,將復雜的功能模塊劃分為低層次的模塊。這一步通常是由系統級的總設計師完成,而低層次的模塊則由下一級的設計人員完成。自頂向下的設計方式有利于系統級別層次劃分和管理,并提高了效率、降低了成本。“自底向上”方式是“自頂向下”方式的逆過程。

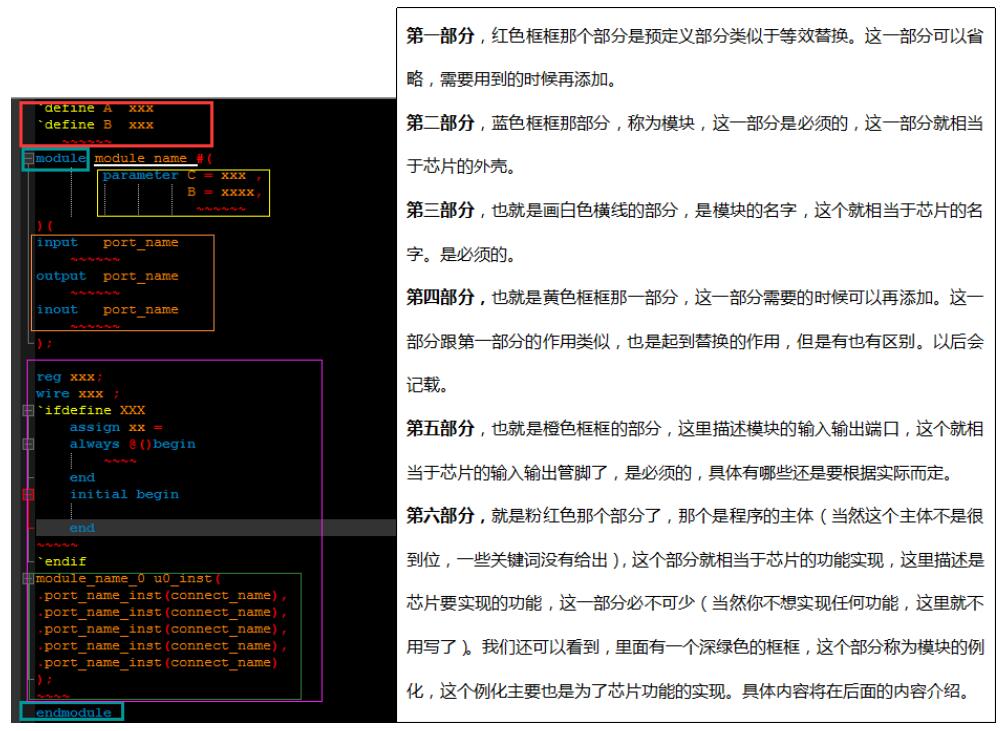

使用Verilog描述硬件的基本設計單元是模塊(module)。構建復雜的電子電路,主要是通過模塊的相互連接調用來實現的。模塊被包含在關鍵字module、endmodule之內。實際的電路元件。Verilog中的模塊類似C語言中的函數,它能夠提供輸入、輸出端口,可以實例調用其他模塊,也可以被其他模塊實例調用。模塊中可以包括組合邏輯部分、過程時序部分。例如,四選一的多路選擇器,就可以用模塊進行描述。它具有兩個位選輸入信號、四個數據輸入,一個輸出端,在Verilog中可以表示為:

module mux (out, select, in0, in1, in2, in3);output out;input [1:0] select;input in0, in1, in2, in3;//具體的寄存器傳輸級代碼endmodule

設計人員可以使用一個頂層模塊,通過實例調用上面這個模塊的方式來進行測試。這個頂層模塊常被稱為“測試平臺(Testbench)”。為了最大程度地對電路的邏輯進行功能驗證,測試代碼需要盡可能多地覆蓋系統所涉及的語句、分支、條件、路徑、觸發、狀態機狀態,驗證人員需要在測試平臺里創建足夠多的輸入激勵,并連接到被測模塊的輸入端,然后檢測其輸出端的表現是否符合預期(諸如SystemVerilog的硬件驗證語言能夠提供針對驗證專門優化的數據結構,以隨機測試的方式進行驗證,這對于高度復雜的集成電路設計驗證可以起到關鍵作用)。實例調用模塊時,需要將端口的連接情況按照這個模塊聲明時的順序排列。這個頂層模塊由于不需要再被外界調用,因此沒有輸入輸出端口:

module tester;reg [1:0] SELECT;reg IN0, IN1, IN2, IN3;wire OUT;mux my_mux (OUT, SELECT, IN0, IN1, IN2, IN3); //實例調用mux模塊,這個實例被命名為my_muxinitial //需要仿真的激勵代碼 begin endendmodule

在這個測試平臺模塊里,設計人員可以設定仿真時的輸入信號以及信號監視程序,然后觀察仿真時的輸出情況是否符合要求,這樣就可以了解設計是否達到了預期。

示例中的對模塊進行實例引用時,按照原模塊聲明時的順序羅列了輸入變量。除此之外,還可以使用或者采用命名端口連接的方式。使用這種方式,端口的排列順序可以與原模塊聲明時不同,甚至可以不連接某些端口:

mux my_mux (.out(OUT), .select(SELECT), .in0(IN0), .in1(IN1), .in2(IN2), .in3(IN3));//使用命名端口連接,括號外面是模塊聲明時的端口,括號內是實際的端口連接//括號外相當于C語言的形式參數,括號內相當于實際參數endmodule

上面所述的情況是,測試平臺頂層模塊的測試變量直接連接了所設計的功能模塊。測試平臺還可以是另一種形式,即測試平臺并不直接連接所設計的功能模塊,而是在這個測試平臺之下,將激勵模塊和功能模塊以相同的抽象級別,通過線網相互連接。這兩種形式的測試平臺都可以完成對功能模塊的測試。大型的電路系統,正是由各個層次不同模塊之間的連接、調用,來實現復雜的功能的。

Verilog HDL 快速入門

Verilog HDL是一種硬件描述語言(HDL:Hardware Description Language),它是以文本形式來描述數字系統硬件的結構和行為的語言。 世界上最流行的兩種硬件描述語言是Verilog HDL和VHDL。

注意,VerilogHDL是一種描述語言,它和常見的編程語言C有根本的不同。C語言,讓計算機的CPU從上往下按順序執行每一條指令,執行完程序就結束了。

而,VerilogHDL主要是描述了一個數字模塊的結構,或者行為。有點像商業合同,合同里面也會描述產品的結構,產品的功能等等。合同的每一個條款,并不需要嚴格的先后順序,只要把項目的方方面面都考慮完整,寫下來就OK了。VerilogHDL也是這樣。

我們用VerilogHDL描述數字模塊的功能,剩下的交給編譯器(如,Quartus),編譯器會根據我們的要求設計重構FPGA內部硬件。對于大批懶人來說,這技術簡直碉堡了。這就是EDA(Electronic Design Automation,電子設計自動化)。

好,下面就來認識一下VerilogHDL

我們先設計一個“數據選擇器”:

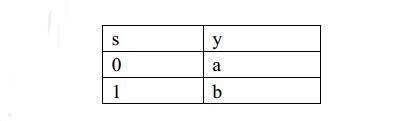

s是數據選擇控制端,

a,b是輸入信號,y是輸出信號

代碼如下:

module mux2_1(a, b, s, y); //模塊名、模塊接口名

input a, b, s; // 定義輸入端口

output y; // 定義輸出端口

/* s為0時,選擇a輸出;

s為1時,選擇b輸出。*/

assign y = (s == 0) ? a : b; //輸出信號

endmodule12345678

每個Verilog文件中都有一個module 開始,endmodule 結束的代碼塊。

這個代碼塊的定義了一個名字叫 mux2_1 的模塊,模塊名后面緊跟的括號內寫明了該模塊的接口信號,相當于數字器件的引腳。

但是括號內沒有說明接口的信號方向,所以緊跟著另起一行用input 和output 再說明一下。注釋和C語法一樣,可以用// 或 /* */ 。

assign 是Verilog的關鍵詞,書上稱為連續賦值。我一般把他視為“連線”操作,assign后面的緊跟的 y 在硬件上是一根導線(或輸出引腳)。

assign y = (s == 0) ? a : b;

這句話的意思是:s如果為0,那么等號左邊就是a,否則就是b。將這個表達式的輸出結果接在輸出引腳 y 上。

這就是一個簡單的Verilog程序,不需要我們去設計與非門,直接表達你的你想要的功能就好了。然后,編譯下載到FPGA,功能就實現了。

要注意的是,assign 后面永遠跟著一個 =,它們是一起使用的。

即,assign xx = zz;

上面的2選1數據選擇器,內部實現結構如下:

所以,上面的assign語句還可以這樣寫,直接使用邏輯表達式:

assign y = (a & (~ s)) | (b & s);

這個是在門級對邏輯關系進行描述,所以不屬于行為描述,算是結構描述吧。下面這種描述方式,叫做門原語,算結構描述。這里的關鍵詞wire 表示電路中的導線(信號線)。

module mux2_1(a, b, s, y);

input a, b, s;

output y;

wire ns, as, bs;

not(ns, s);//這里使用了一個非門,輸出是ns,輸入是s

and(as, a, ns);//使用一個與門,輸出as,輸入a和ns

and(bs, b, s);//使用與門,輸出bs,輸入b和s

or(y, as, bs);//使用或門,輸出y,輸入as和bs

endmodule12345678910

看,這是告訴我們電路中有什么元器件,又是怎么連接的,所以這個屬于結構描述。

很明顯,有時候結構描述比行為描述要費力得多,而且不太容易理解程序功能。

另外,上面的這個程序中,這4個邏輯門的順序,可以隨便寫,不用管先后順序。

這個數據選擇器,還可以使用如下行為描述方法:

module mux2_1(a, b, s, y);

input a, b, s;

output y;

reg y; //reg 表示寄存器

always @(a, b, s)

begin

if(!s) y = a;

else y = b;

end

endmodule1234567891011

這里reg表示寄存器(存儲器),需要提醒一下的是,assign后面只能接wire型,不能接reg型。(當然output從物理上也是wire)

為什么不能?因為寄存器的賦值除了需要輸入信號,還需要觸發信號(例如D觸發器寄存器),assign?sorry,he can’t。

always @(a, b, s)中,括號里面的輸入信號a,b,s表示敏感信號。

always @( ) 是連在一起使用的。

這句話的意思是,敏感信號列表中的任何一個信號發生變化,將會引發

begin …… end 之間的行為。

Verilog用begin和end包圍代碼段,相當于c語言中的大括號{ }的功能。

if(!s) y = a;

這里的“=”單獨使用,叫做“阻塞賦值”。我把他理解為“串行賦值”。

比如,有這么一段代碼:

b=a;

c=b;

那么最后,c的值就等于a,這個行為在描述的時候,語句的先后順序,決定了賦值的先后。

在Verilog中,和它對應的還有一個“非阻塞賦值”,表示方法是 《=,我把這種賦值稱為“并行賦值”。具體區別,請參考另一篇短文阻塞賦值和非阻塞賦值。

? 交流問題 ? Q :FPGA打磚塊小游戲,如何基于FPGA用verilog語言在Vivado平臺上寫打磚塊小游戲,最好能用到PS2與VGA。 A :...

2024-12-09 標簽:FPGAVerilog HDLVivado 690 0

Verilog HDL是一種硬件描述語言,以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完...

2023-12-07 標簽:fpgaVerilogVerilog HDL 3454 0

prj為工程文件存放目錄;rtl為verilog可綜合代碼存放目錄;tb為測試文件存放目錄;image為設計相關圖片存放目錄;doc為設計相關文檔存放目...

2023-01-10 標簽:fpgaFPGA芯片Verilog HDL 632 0

Verilog HDL是一種用于數字系統設計的語言。用Verilog HDL描述的電路設計就是該電路的Verilog HDL模型也稱為模塊。Verilo...

2022-12-08 標簽:fpgaVerilogVerilog HDL 3150 0

今天給大俠帶來的是一周掌握FPGA Verilog HDL 語法,今天開啟第二天。上一篇提到了整數型以及參數型,此篇我們繼續來看變量以及后續其他內容,結...

2022-07-18 標簽:fpga變量Verilog HDL 2019 0

一、HDL的概念和特征 HDL,Hard Discrimination Language的縮寫,翻譯過來就是硬件描述語言。那么什么是硬件描述語言呢?為什...

2020-10-21 標簽:fpgaIC設計Verilog HDL 4649 0

基于FPGA的SOC在嵌入式系統應用越來越廣了,往往一個復雜系統使用一個單芯片基于FPGA的SOC就搞定了。比較流行的方案主要有Altera/xilin...

2020-09-01 標簽:C語言Verilog HDL 4587 0

Verilog HDL的程序結構_veriloghdl的關鍵字

首先我們不開始講Verilog HDL的語法,我們從Verilog HDL的程序結構出發。相信大家都看過芯片吧,它有個名字,有個外殼,外殼向外伸出有引腳...

2020-08-27 標簽:VerilogVerilog HDL 2630 0

類別:電子資料 2023-11-08 標簽:fpgaofdmVerilog HDL

類別:電子資料 2023-11-08 標簽:fpga函數Verilog HDL

類別:電子資料 2023-08-29 標簽:Verilog HDL硬件描述語言

在Verilog HDL中使用分頻器的8位計數器的設計立即下載

類別:電子資料 2023-06-15 標簽:fpga計數器Verilog HDL

類別:電子資料 2023-02-10 標簽:vhdlVerilog HDL

Verilator高性能Verilog HDL模擬器與lint系統立即下載

類別:電子資料 2022-04-14 標簽:C++模擬器Verilog HDL

Verilog HDL入門教程-Verilog HDL的基本語法立即下載

類別:FPGA/ASIC 2022-01-07 標簽:Verilog HDL

類別:C語言|源代碼 2021-08-13 標簽:編程Verilog HDL

類別:VHDL/Verilog/EDA源碼 2021-05-06 標簽:仿真Verilog HDL

Verilog HDL的禮物-Verilog HDL掃盲文下載立即下載

類別:FPGA/ASIC 2021-04-30 標簽:FPGAVerilog HDL

標識符可以是一組字母、數字、下劃線和$符號的組合,且標識符的第一個字符必須是字母或者下劃線。

2022-07-04 標簽:寄存器運算符Verilog HDL 1583 0

原文標題:非常詳細的Verilog講義教程 文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。 ? ? ? 審核編輯:彭靜

2022-07-04 標簽:軟件Verilog HDL 904 0

Verilog HDL 優點:類似C語言,上手容易,靈活。大小寫敏感。在寫激勵和建模方面有優勢。 缺點:很多錯誤在編譯的時候不能被發現。 VHDL 優點...

Verilog HDL verilog hdl和vhdl的區別

Verilog HDL是一種以文本形式描述數字系統硬件的結構和行為的硬件描述語言,也可描述邏輯電路圖、邏輯表達式等。Verilog HDL和VHDL是目...

2021-07-23 標簽:VHDLVerilog HDL 1.1萬 0

Verilog HDL中定義的26個有關門級的關鍵字中常用的有哪些?

1、結構描述形式 從電路結構的角度來描述電路模塊,稱為結構描述形式。 Verilog HDL中定義了26個有關門級的關鍵字,比較常用的有8個: and ...

2021-07-02 標簽:Verilog HDL 3282 0

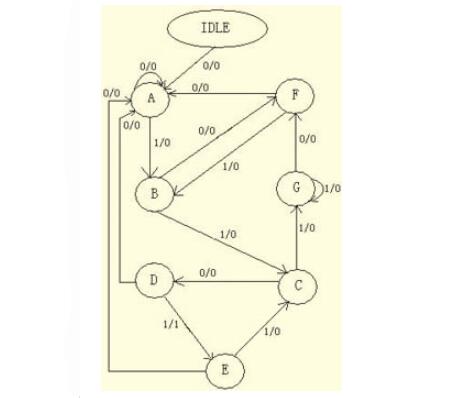

基于Verilog HDL描述語言實現交通燈系統控制器的設計

EDA技術是依靠功能強大的電子計算機,在EDA工具軟件平臺上,對以硬件描述語言HDL(Hardware Description Language)為系...

2020-07-21 標簽:交通燈系統控制器Verilog HDL 8431 0

通常設計數字電路大都采用自頂向下將系統按功能逐層分割的層次化設計方法,這比傳統自下向上的EDA設計方法有更明顯的優勢(當時的主要設計文件是電路圖)。因為...

2020-07-20 標簽:fpgaedaVerilog HDL 2272 0

在數字信號的傳輸過程中,有時需要從多路輸入數據中選出某一路數據,完成此功能的邏輯器件稱為數據選擇器,即所謂多路開關,簡稱MUX(Multiplexer)...

2020-07-20 標簽:Verilog HDL多路選擇器 4937 0

電子發燒友網核心提示: 本例程是Verilog HDL源代碼:關于基本組合邏輯功能中7段譯碼器的功能實現源代碼。注意:程序運行在不同軟件平臺可能要作一些...

2012-10-15 標簽:譯碼器Verilog HDLHDL源代碼 2.4萬 0

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題 教程专题

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |