完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > clk

文章:114個(gè) 瀏覽:17182次 帖子:106個(gè)

FPGA設(shè)計(jì)之Verilog中clk為什么要用posedge而不用negedge?

Verilog是一種硬件描述語言,用于描述數(shù)字電路的行為和特性。在Verilog中,時(shí)鐘信號(hào)(clk)和線路是非常重要的,它用于同步電路中的各個(gè)模塊,確...

2023-10-10 標(biāo)簽:同步電路FPGA芯片時(shí)鐘信號(hào) 3938 0

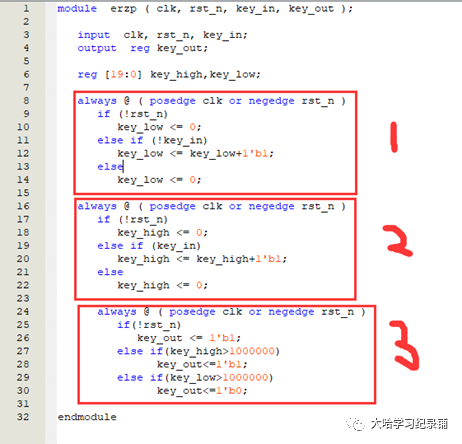

如何設(shè)計(jì)一個(gè)對(duì)按鍵信號(hào)進(jìn)行計(jì)數(shù)的計(jì)數(shù)器?

detect_module模塊用于檢測按鍵信號(hào)的下降沿,當(dāng)檢測到下降沿后,輸出一個(gè)時(shí)鐘周期的高電平。

2023-10-10 標(biāo)簽:寄存器計(jì)數(shù)器CLK 1770 0

單口RAM、同步FIFO、異步FIFO的設(shè)計(jì)

if((!empty && re)&&(!full && we))// 同時(shí)讀寫,計(jì)數(shù)不變;

有限狀態(tài)機(jī)分割設(shè)計(jì),其實(shí)質(zhì)就是一個(gè)狀態(tài)機(jī)分割成多個(gè)狀態(tài)機(jī)

2023-10-09 標(biāo)簽:有限狀態(tài)機(jī)狀態(tài)機(jī)fsm 651 0

FPGA設(shè)計(jì)中的模塊化設(shè)計(jì)

模塊化設(shè)計(jì)是FPGA設(shè)計(jì)中一個(gè)很重要的技巧,它能夠使一個(gè)大型設(shè)計(jì)的分工協(xié)作、仿真測試更加容易,代碼維護(hù)或升級(jí)也更加便利。

2023-10-07 標(biāo)簽:FPGA設(shè)計(jì)CLK 1543 0

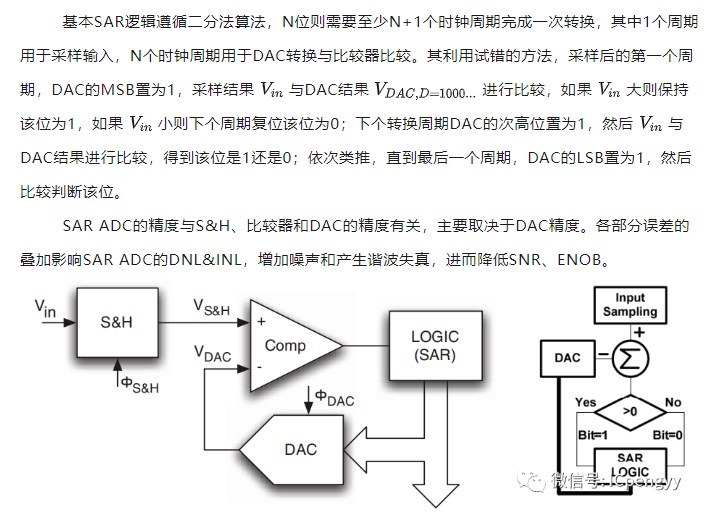

AD數(shù)據(jù)轉(zhuǎn)換-SAR ADC介紹

基本SAR(Successive Approxmation Register)ADC結(jié)構(gòu)中包括采樣保持S&H電路、比較器、DAC、SAR邏輯四個(gè)單元。

使用普通的多路復(fù)用器進(jìn)行切換時(shí)鐘會(huì)發(fā)生什么?

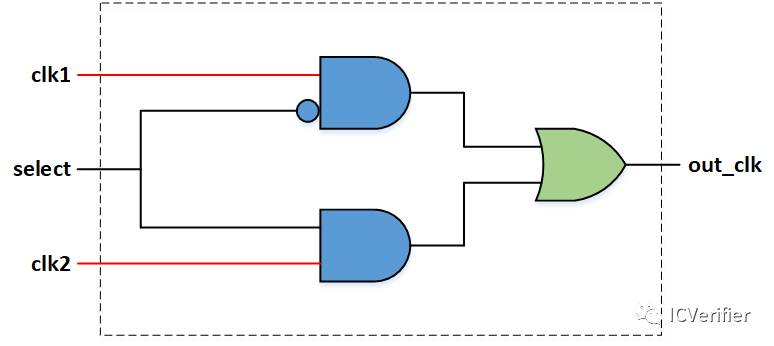

在現(xiàn)代芯片中,芯片運(yùn)行時(shí)有必要在兩個(gè)不同的時(shí)鐘之間切換。如果我們使用普通的多路復(fù)用器進(jìn)行切換時(shí)鐘會(huì)發(fā)生什么?

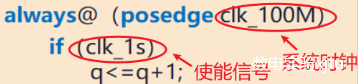

如何使用Verilog硬件描述語言描述時(shí)序邏輯電路?

時(shí)序邏輯電路的特點(diǎn)是輸出信號(hào)不僅與電路的輸入有關(guān),還與電路原來的狀態(tài)有關(guān)。

2023-09-17 標(biāo)簽:FPGA設(shè)計(jì)反相器D觸發(fā)器 3203 0

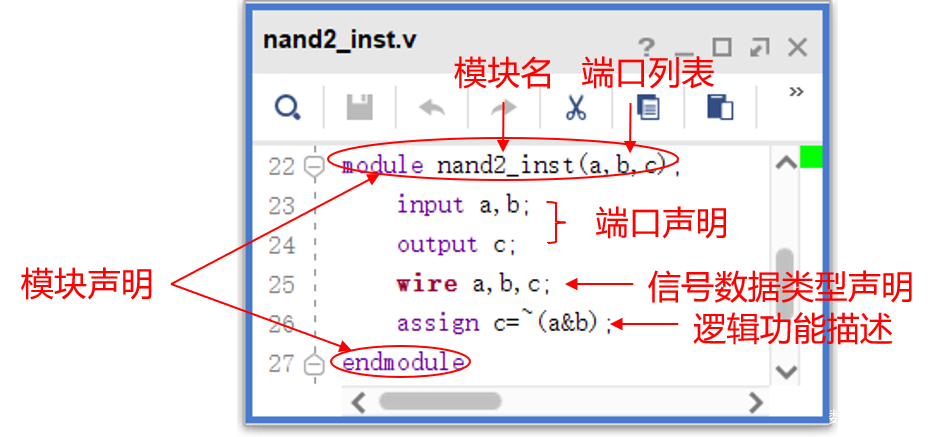

看看兩個(gè)使用Verilog HDL設(shè)計(jì)的簡單電路

與非門的Verilog 描述如下圖所示,源程序文件的后綴為.v。

2023-09-17 標(biāo)簽:D觸發(fā)器時(shí)序邏輯電路Module 1617 0

異步復(fù)位寄存器的0時(shí)刻是如何進(jìn)行賦值的呢?

Verilog規(guī)范告訴我們:negedge 事件指的是如表43所示的跳變,發(fā)生negedge事件時(shí)才會(huì)執(zhí)行操作。那么0時(shí)刻,是如何執(zhí)行操作的呢?

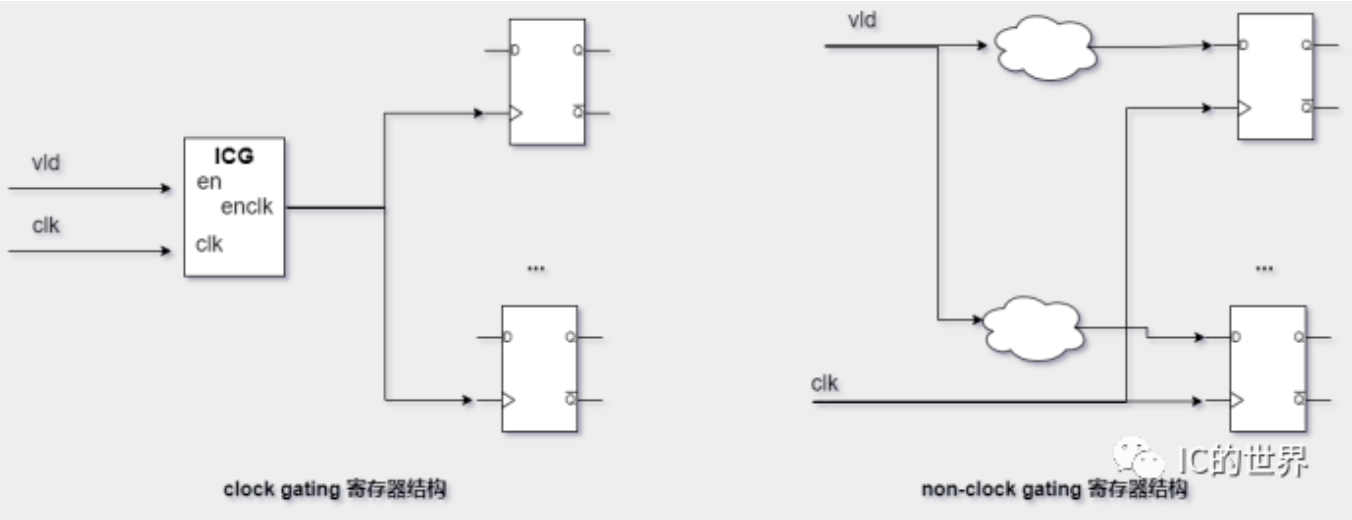

在ASIC設(shè)計(jì)中,項(xiàng)目會(huì)期望設(shè)計(jì)將代碼寫成clk-gating風(fēng)格,以便于DC綜合時(shí)將寄存器綜合成clk-gating結(jié)構(gòu),其目的是為了降低翻轉(zhuǎn)功耗。

2023-09-04 標(biāo)簽:寄存器IC設(shè)計(jì)ASIC設(shè)計(jì) 1920 0

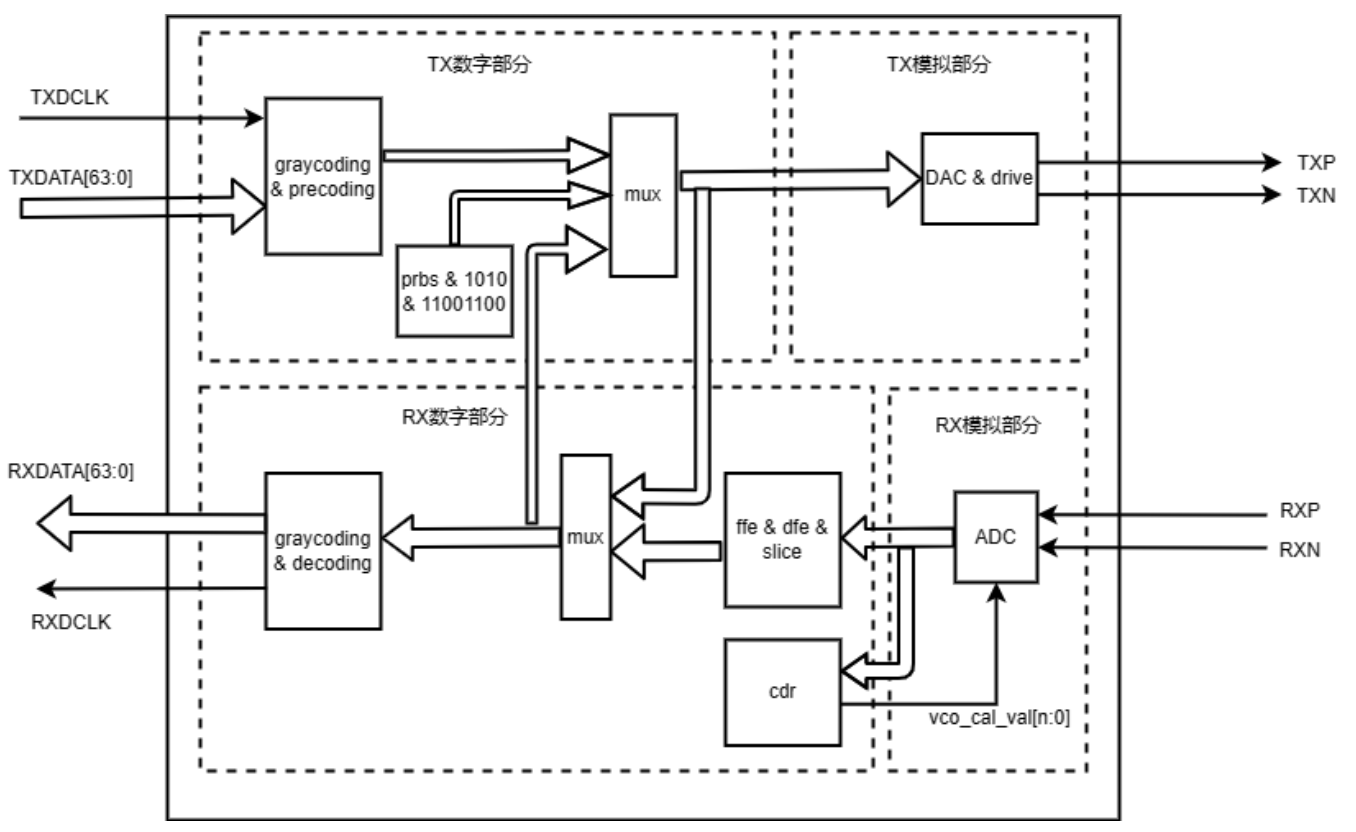

在芯片內(nèi)部,信號(hào)一般都是通過并行傳輸?shù)模驗(yàn)榇袀鬏攲?shí)在是太慢了。

2023-09-01 標(biāo)簽:CLKI2C協(xié)議ADC采樣 1150 0

數(shù)字前中后端都不得不熟練的clock switch設(shè)計(jì)

插入下降沿觸發(fā)的D觸發(fā)器,當(dāng)前已打開的時(shí)鐘路徑上的時(shí)鐘會(huì)在其下降沿之后先關(guān)閉,然后待打開時(shí)鐘路徑上的時(shí)鐘在其下降沿之后即打開。如下所示:從下圖第二個(gè)箭頭...

寫assertion很痛苦?了解一下SVA Checker Library

請(qǐng)根據(jù)這段代碼寫一個(gè)assertion檢查 count 每次加5。

2023-08-12 標(biāo)簽:VCSSVAFIFO存儲(chǔ) 1210 0

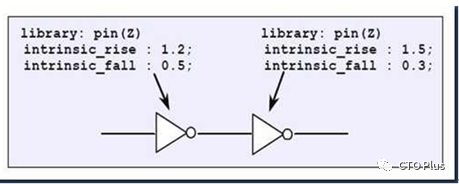

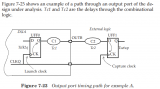

set_output_delay的本質(zhì)是什么?淺談set_ouput_delay時(shí)序

set_output_delay是對(duì)模塊output信號(hào)在模塊外部延遲的約束,本質(zhì)上EDA工具會(huì)根據(jù)約束調(diào)整內(nèi)部器件(UFF0)的類型,擺放位置以及組合...

昨天群里小伙伴說在VScode中用AI寫verilog效果很好。小編以前編輯代碼都是用gvim。抱著學(xué)習(xí)的心態(tài),我在linux下嘗試了下用VScode寫代碼。

2023-08-03 標(biāo)簽:Linux系統(tǒng)I2C總線CLK 3453 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |