完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > IP核

IP就是知識產權核或知識產權模塊的意思,在EDA技術開發中具有十分重要的地位。美國著名的Dataquest咨詢公司將半導體產業的IP定義為“用于ASIC或FPGA中的預先設計好的電路功能模塊”。

IP就是知識產權核或知識產權模塊的意思,在EDA技術開發中具有十分重要的地位。美國著名的Dataquest咨詢公司將半導體產業的IP定義為“用于ASIC或FPGA中的預先設計好的電路功能模塊”。IP主要分為軟IP、固IP和硬IP。軟IP是用Verilog/VHDL等硬件描述語言描述的功能塊,但是并不涉及用什么具體電路元件實現這些功能。固IP是完成了綜合的功能塊。硬IP提供設計的最終階段產品——掩膜。

IP就是知識產權核或知識產權模塊的意思,在EDA技術開發中具有十分重要的地位。美國著名的Dataquest咨詢公司將半導體產業的IP定義為“用于ASIC或FPGA中的預先設計好的電路功能模塊”。IP主要分為軟IP、固IP和硬IP。軟IP是用Verilog/VHDL等硬件描述語言描述的功能塊,但是并不涉及用什么具體電路元件實現這些功能。固IP是完成了綜合的功能塊。硬IP提供設計的最終階段產品——掩膜。

基本分類

IP內核的三種類型

IP核有三種不同的存在形式:HDL語言形式,網表形式、版圖形式。分別對應我們常說的三類IP內核:軟核、固核和硬核。這種分類主要依據產品交付的方式,而這三種IP內核實現方法也各具特色。

軟核

軟核是用VHDL等硬件描述語言描述的功能塊,但是并不涉及用什么具體電路元件實現這些功能。軟IP通常是以硬件描述語言HDL源文件的形式出現,應用開發過程與普通的HDL設計也十分相似,只是所需的開發硬軟件環境比較昂貴。軟IP的設計周期短,設計投入少。由于不涉及物理實現,為后續設計留有很大的發揮空間,增大了IP的靈活性和適應性。其主要缺點是在一定程度上使后續工序無法適應整體設計,從而需要一定程度的軟IP修正,在性能上也不可能獲得全面的優化。由于軟核是以源代碼的形式提供,盡管源代碼可以采用加密方法,但其知識產權保護問題不容忽視。

硬核

硬核提供設計階段最終階段產品:掩膜。以經過完全的布局布線的網表形式提供,這種硬核既具有可預見性,同時還可以針對特定工藝或購買商進行功耗和尺寸上的優化。盡管硬核由于缺乏靈活性而可移植性差,但由于無須提供寄存器轉移級(RTL)文件,因而更易于實現IP保護。

固核

固核則是軟核和硬核的折衷。大多數應用于FPGA的IP內核均為軟核,軟核有助于用戶調節參數并增強可復用性。軟核通常以加密形式提供,這樣實際的 RTL對用戶是不可見的,但布局和布線靈活。在這些加密的軟核中,如果對內核進行了參數化,那么用戶就可通過頭文件或圖形用戶接口(GUI)方便地對參數進行操作。對于那些對時序要求嚴格的內核(如PCI接口內核),可預布線特定信號或分配特定的布線資源,以滿足時序要求。這些內核可歸類為固核,由于內核是預先設計的代碼模塊,因此這有可能影響包含該內核的整體設計。由于內核的建立(setup)、保持時間和握手信號都可能是固定的,因此其它電路的設計時都必須考慮與該內核進行正確地接口。如果內核具有固定布局或部分固定的布局,那么這還將影響其它電路的布局。

技術應用

數字到模擬轉換器(DACs)將一個二進制數轉換為與之對應的電壓值,常用的D/A轉換器都是由電阻或電容加權網絡、受碼元控制的開關和基準電壓或電流源組成。當D/A轉換器需要轉換的信號每次取樣字長很長時,對這些電路的精度要求很高,并且還必須在整個溫度范圍和整個使用壽命期間內保持電路參數的穩定。例如,一個16位的D/A轉換器,其MSB的精度必須在1/2 16以內,這是很困難的。所以,需尋求一種中保持高分辨率又可降低對電路精度和穩定度要求的方法。

可綜合的Delta-Sigma DAC(術語Delta-Sigma分別指算術差與和,即Δ-∑DAC),是Xilinx公司提供的免費IP核,可從網上下載得到。

選擇和配置

選擇MAX7000S系列可編程邏輯器件,編譯后由MAX+PLUS II軟件自動配置進EMP7032SLC44芯片,將生成的目標文件通過編程電纜對器件進行編程。

將該IP核實現的D/A轉換器用于新型智能電阻爐溫度控制儀中,因為調節爐溫的信號不要求變化很快,因此DAC的輸入二進制信號為緩變信號。對于這種低頻應用,可以將RC時間常數取得較大,以減小噪聲。這樣,可綜合的VHDL語言Delta-Sigma DAC模塊配置進EMP7032芯片后,達到了預期的效果。

IP核的分類及特點

IP核的知識產權核心分為三大種類:硬核,中核和軟核。硬件中心是知識產權構思的物質表現。這些利于即插即用應用軟件并且比其它兩種類型核的輕便性和靈活性要差。像硬核一樣,中核(有時候也稱為半硬核)可以攜帶許多配置數據,而且可以配置許多不同的應用軟件。三者之中最有靈活性的就是軟核了,它存在于任何一個網絡列表(一列邏輯門位和互相連接而成的集成電路)或者硬件描述語言(HDL)代碼中。

IP核的設計原理

軟IP內核通常是用某種HDL文本提交用戶,它已經過行為級設計優化和功能驗證,但其中不含有任何具體的物理信息。據此,用戶可以綜合出正確的門電路級網表,并可以進行后續結構設計,具有最大的靈活性,可以很容易地借助于EDA綜合工具與其他外部邏輯電路結合成一體,根據各種不同的半導體工藝,設計成具有不同性能的器件。可以商品化的軟IP內核一般電路結構總門數都在5000門以上。但是,如果后續設計不當,有可能導致整個結果失敗。軟IP內核又稱作虛擬器件。

硬IP內核是基于某種半導體工藝的物理設計,已有固定的拓撲布局和具體工藝,并已經過工藝驗證,具有可保證的性能。其提供給用戶的形式是電路物理結構掩模版圖和全套工藝文件,是可以拿來就用的全套技術。

固IP內核的設計深度則是介于軟IP內核和硬IP內核之間,除了完成硬IP內核所有的設計外,還完成了門電路級綜合和時序仿真等設計環節。一般以門電路級網表形式提交用戶使用。

IP核的總線介紹

為了使IP 核集成更快速、更方便,縮短進入市場的時間,迫切需要一種標準的互聯方案,在這一背景下產生的片上總線OCB(on-chip bus)技術。目前,基于IP 核互連的總線結構較有影響力的有三種:IBM公司的Core Connect,ARM 公司的AMBA(Advanced MicrocontrollerBusArchitecture)和SilicoreCorp公司的Wishbone。

1.CoreConnect 總線IBM 公司的CoreConnect 總線提供了三種基本結構:處理器內部總線PLB(Processor Local Bus)、片上外圍總線OPB(On-ChipPeripheral Bus)和設備控制總線DCR(Device Control Register)。

(1) PLB 標準是為總線傳輸的主要發出者和接受者之間提供高帶寬、低延遲的連接。其主要特征為: 高性能處理器內部總線;

交疊的讀和寫功能(最快每周期兩次傳輸); 支持分段傳輸; 讀和寫分開; 32~64 位數據總線; 32 位地址空間; 支持16~64 字節突發傳輸模式; 4 級仲裁優先權; 特殊DMA(Direct Memory Access)模式。

(2) OPB 標準為連接具有不同的總線寬度及時序要求的外設和內存提供了一條途徑,并盡量減小對PLB 性能的影響。其主要特性如下: 片上外圍總線、支持多個主設備; 32 位地址空間; 讀和寫數據總線分開; 8~32 位數據總線; 動態總線寬度; 支持重試模式(如果主設備要求的從設備忙,主設備隔一段時間再次請求); 支持突發(burst)傳輸模式; 支持DMA。

(2) DCR 是用來規范CPU 通用寄存器設備,控制寄存器之間傳輸數據。DCR 總線在內存地址映射中取消了配置寄存器,減少取操作,增加處理器內部總線的帶寬。其主要特征如下: 10 位地址總線; 32 位數據總線; 同步和異步的傳輸; 分布式結構。

CoreConnect 擁有完備的一整套技術文檔,在技術上可行性較強,可以應用在類似于工作站這樣的高性能系統的連接,對于簡單的嵌入式應用來說可能有點太復雜,提供的許多特性無法用到。

2.AMBA 總線AMBA 總線體系結構定義了2 種總線:AHB(Advanced High-performanceSOC 設計初級培訓(Bus)和APB(Advance Peripheral Bus),如圖1-2 所示。圖1-2 AMBA 總線體系結構(1) AHB 主要用于連接高性能、高吞吐率的設備,完成ARM 芯核與CPU外圍部分例如存儲通道控制器,DMA 控制器,SPI 接口等的整合。它的主要特性包括: 多控制器; 分段傳輸; 單周期總線控制權移交; 32~128 位總線寬; 包含一種訪問保護機制,用來區別特權訪問和無特權訪問模式,或指令和數據提取等; 突發傳輸模式最大為16 節; 訪問空間限制在32 位;

支持仲裁、REQ、GNT 和LOCK; 支持字節、半字和字傳輸。

(2) APB 是專為降低功耗以及接口復雜性而設計的外圍互聯總線,它常被用于連接一些低帶寬、低速傳輸的外設,主要特征如下: 低性能、低功率外圍總線; 單控制器; 32 位地址空間; 32 位數據總線; 分開讀和寫數據總線。

3.Wishbone 總線Wishbone 總線是Silicore 公司推出的片上總線協議。它的結構極其簡單、靈活,又完全公開、完全免費,獲得眾多支持。主要特征如下: 所有應用使用一個總線體系結構; 支持多控制器; 64 位地址空間; 8~64 位數據總線(可擴展); 單周期讀和寫; 支持重試; 支持內存映射,FIFO(FISRT IN FIRSTO U T )和十字互連接口; 由終端用戶定義仲裁方式。同前2 種總線結構相比,Wishbone 只定義了一種高速總線,在既需要高速總線又需要低速總線的系統中,使用兩個Wishbone 接口,比起設計兩個不同的接口要簡單些。

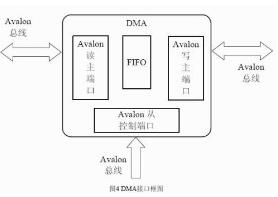

4.Avalon 總線這里,再介紹下將要用到的Avalon 總線。Avalon 總線發布于2000 年的秋天,是Altera 公司針對FPGAs 而設計的一種SOPC 接口標準。它提供了各設備之間連接的接口,可以用于片上處理器和外設之間的連接。Avalon 總線具有支持SOPC,結構簡單和可參數化配置等特點。主要特征如下: 32 位地址空間,共計4Gbytes; 所有Avalon 總線信號都是和Avalon 總線時鐘同步的,這種設計簡化了Avalon 總線的時序行為,便于和高速外設的連接; 地址、數據和控制信號使用獨立的端口,以簡化外設的設計; Avalon 總線自動為所有外設產生片選信號,簡化了Avalon 總線外設的設計; 支持多主設備結構。多個主設備可以共存于Avalon 總線之中,Avalon 總線會自動產生仲裁邏輯; 基于向導的配置。用戶可以使用圖形化的向導來配置Avalon 總線的相關參數; 動態的總線寬度。Avalon 總線會自動處理不同位寬設備間的信SOC 設計初級培訓號,使不同位寬的設備可以順利通訊;

常用的IP核介紹

眾多的IP 提供商包括純IP 提供商、設計服務公司等都可以向設計者提供各種各樣的IP 核。目前,比較著名的IP 提供商包括ARM、Rambus、Synopsys、TTPCom、ParthusCeva、

Virage Logic、Artisan、MIPS、Mentor 和Mosys 等公司。ARM 作為業內領先的32 位嵌入式RISC(Reduced Instruction Set Computer CPU)微處理器解決方案供應商,自1990 年正式成立以來,發展迅速。下面就以ARM 公司為例,進行介紹。ARM 的IP 核技術包括芯片內核、結構延伸、軟件開發工具和片上系統解決方案,具有功耗低、性能高、成本低等特點。適用于多種領域,ARM 的用戶遍及多個行業,包括:汽車、消費、娛樂、成像、工業、控制、網絡、存儲、安保和無線應用。ARM 公司的“chipless”模式非常獨特,它從不直接介入芯片的生產和銷售領域,而是一直以IP 提供者的身份向各大半導體制造商出售知識產權。這種獨特的模式,使設計公司、OEM、軟件及工具開發公司及制造公司都與ARM結成了合作伙伴關系,使其半導體行業產業鏈上游的上游,成為許多全球性RISC 標準的締造者。目前,采用ARM 公司IP 核的半導體公司已多達103 家,包括Intel、TI、Motorola、ST、IBM、ADI、美國國家半導體、Infineon、NEC、LSI 等半導體巨擘,RTOS 軟件廠商超過50 家如微軟、WindRiver 等公司,EDA工具廠商超過30 家如Cadence、Synopsys 等。ARM 處理器核當前有6 個系列產品ARM7,ARM9,ARM9E,ARM10E,SecurCore 以及ARM11 系列。進一步還包括與其合作伙伴一同研發的產品,如Intel XScale 微體系結構和StrongARM 產品。其中每一類又根據其包含的不同功能模塊而分成多種型號。在ARM 內核中常用的四個模塊分別用T、D、M 和I 來表示,它們可供生產廠商根據不同用戶的需求來選擇配置。

(1) T 表示Thumb,該內核可從16 位指令集擴充到32 位ARM 指令集。

(2) D 表示Debug,該內核中包含可用于調試的結構,通常為一個邊界掃描鏈JTAG,以便進入CPU 調試模式,從而進行斷點設置、單步調試等工作。

(3) M 表示Multiplier,是8 位乘法器。

(4) I 表示Embedded ICE Logic,包含用于實現斷點觀測及變量觀測的邏輯電路,其中的TAP 控制器可接入到邊界掃描鏈。

1.ARM7

ARM7采用ARMV4T結構,分為三級流水,空間統一的指令與數據Cache,平均功耗為0.6mW/MHz,時鐘速度為20MHz~133MHz,每條指令平均需要1.9 個時鐘周期,處理速度為0.9MIPS/MHz。其中的ARM710,ARM720 和ARM740 為內帶Cache 的ARM 核。ARM 7 的運算速度一般為150DMIPS。ARM7 是小型、快速、低能耗、集成式RISC 內核,廣泛應用于手持式計算、數據通信和消費類多媒體。

2.ARM9

ARM9 采用ARMV4T 結構,采用五級流水處理以及分離的Cache 結構,平均功耗為0.7mW/MHz。時鐘速度為100MHz~233MHz,每條指令平均需要1.5 個時鐘周期,處理速度為1.1MIPS/MHz。其中,ARM920、ARM940 和ARM9E 為含Cache 的CPU 核。性能為132MIPS(120MHz 時鐘,3.3V 供)或220MIPS(200MHz 時鐘)。ARM 9 的運算速度一般為300DMIPS。ARM9 是低價、低能耗、高性能系統微處理器,配有Cache、內存管理和寫緩沖。多應用于高級引擎管理、保安系統、頂置盒、便攜計算機和高檔打印機。

ARM9E 應該屬于ARM10 系列,它也采用了ARMV5TE 結構,其性能得到了大大提高。其中,ARM968E-S(tm)是ARM9E 系列的最新產品,它同時也是ARM9E 系列內核中最小的、最低功耗的產品,可以為網絡、汽車、電子消費娛樂品、無線方案等提供理想的技術方案。ARM968E-S 內核含有低延遲的AMBA(tm) AHB-lite 總線接口,內核與DMA 時鐘分離, 在閑置狀態下的功耗更低。ARM968E-S 內核比ARM966E-S(tm)內核的面積小20%,功耗至少降低10%。延長了電池使用壽命。

3.ARM10

ARM10 采用ARMV5TE 結構,采用六級流水處理,指令與數據分離的Cache 結構。時鐘速度為300MHz,每條指令平均需要1.2 個周期。其中ARM1020 為帶Cache 的版本。ARM 10 的運算速度一般為500DMIPS。ARM10 速度快,能夠支持多種商用操作系統,適用于高性能手持式因特網設備及數字式消費類產品。

3.ARM11

ARM11 采用ARMV6 結構,采用8 級流水處理,動態分支預測與返回堆棧。ARM11 的時鐘速度達到550MHz,采用了0.13 微米的工藝技術,支持IEM技術,可以大大減少功耗。ARM 11 的運算速度一般為1000DMIPS。ARM還發布了四個新的ARM11 系列微處理器內核(ARM1156T2-S 內核、ARM1156T2F-S 內核、ARM1176JZ-S 內核和ARM11JZF-S 內核)、應用ARM1176JZ-S 和ARM11JZF-S 內核系列的PrimeXsys 平臺、相關的CoreSight技術。

ARM1156T2-S 和ARM1156T2F-S 是首批含有ARM Thumb-2 內核技術的產品,主要用于多種深嵌入式存儲器、汽車網絡和成像應用產品,提供了更高的CPU 性能和吞吐量,并增加了許多特殊功能,可解決新一代裝置的設計難題。它們采用AMBA 3.0 AXI 總線標準,可滿足高性能系統的大量數據存取需求。Thumb-2 內核技術結合了16 位、32 位指令集體系結構,提供更低的功耗、更高的性能、更短的編碼,該技術提供的軟件技術方案較現用的ARM 技術方案減少使用26%的存儲空間、較現用的Thumb 技術方案增速25%。ARM1176JZ-S 和ARM1176JZF-S 內核是首批以ARM TrustZone 技術實現手持裝置和費電子裝置中公開操作系統的超強安全性的產品,同時也是首次對可節約高達75%處理器功耗的ARM 智能能量管理(ARM Intelligent Energy Manager)進行一體化支持。主要為服務供應商和運營商所提供的新一代消費電子裝置的電子商務和安全的網絡下載提供支持。

4.StrongARM

StrongARM 處理器采用ARMV4T 的五級流水結構,性能較高。它最初是與DEC 聯合研制的,后來授權給Intel,Intel 公司用SA110 命名該通用嵌入式標準處理器。該系列還包括SA1100 PDA 系統芯片和SA1500 多媒體處理器芯片。ARM 芯片的選擇要根據實際需求而定。例如,如果希望使用WinCE 或Linux 等操作系統以減少軟件開發時間,就需要選擇ARM720T 以上帶有MMU(memory management unit)功能的ARM 芯片,ARM720T、StrongARM、ARM920T、ARM922T、ARM946T 都帶有MMU 功能。而ARM7TDMI 沒有MMU,不支持Windows CE 和大部分的Linux,但目前有uCLinux 等少數幾種Linux 不需要MMU 的支持。

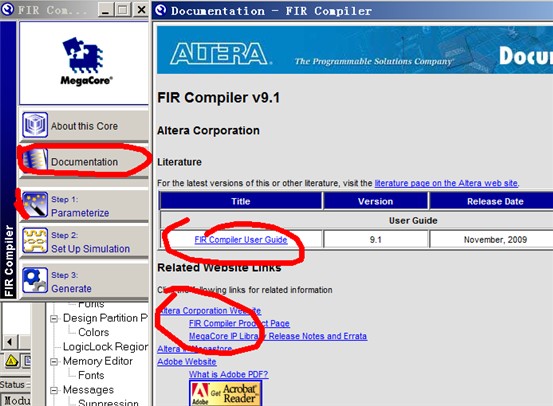

很多人都說QUARYUSII中的IP核是收費的,不可以直接用的,其實不然,下面我以FIR濾波器的核的使用來給大家介紹IP核的使用,希望對大家有點幫助。 ...

2013-01-16 標簽:IP核QUARTUS II 7.8萬 10

大家好,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。 首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivad...

為了簡化編碼解碼器和PL之間的集成復雜度,這里介紹兩個AVNET所開發的IP核,可通過Avnet GitHub下載( github.com/Avnet/...

玩轉賽靈思Zedboard開發板(5):基于AXI Lite總線的從設備IP設計

本小節通過使用XPS中的定制IP向導(ipwiz),為已經存在的ARM PS 系統添加用戶自定IP(Custom IP ),了解AXI Lite IP基...

Xilinx IP核配置,一步一步驗證Xilinx Serdes GTX最高8.0Gbps

之前用serdes一直都是跑的比較低速的應用,3.125Gbps,按照官方文檔一步一步來都沒出過什么問題,這次想驗證一下K7系列GTX最高線速8Gbps...

第二項是器件添加,只有選擇了相應的器件,你的IP核才能在那個器件里被使用。單擊器件,右鍵——Add——Add Family Explicitiy,于是便...

高云半導體推出GW2A系列FPGA芯片的DDR類儲存器接口解決方案

山東濟南,2017年10月10日訊,山東高云半導體科技有限公司(以下簡稱山東高云半導體)今天宣布推出基于中密度晨熙?家族的GW2A系列FPGA芯片的DD...

玩轉賽靈思Zedboard開發板(4):如何使用自帶外設IP讓ARM PS訪問FPGA?

本文的目的是使用XPS為ARM PS 處理系統添加額外的IP。從IP Catalog 標簽添加GPIO,并與ZedBoard板子上的8個LED燈相連。當...

基于Quartus II免費IP核的雙端口RAM設計實例立即下載

類別:FPGA/ASIC 2012-11-13 標簽:RAMIP核Quartus II

中天微基于C-SKY CPU IP核的SoC芯片累計出貨量已經突破8億顆

在此時間節點上,中天微正式推出基于RISC-V的第三代C-SKY指令架構,同時發布第一個32位低功耗CK902處理器,并表示將針對不同的產品應用場景,持...

智能手機、平板機和移動互聯網的興起,讓原本默默無聞的英國小公司ARM成了世界矚目的焦點,甚至搞得半導體霸主Intel狼狽不堪,屢屢受挫。 2008年開...

Imagination在近日更新了MIPS旗艦級的Aptiv 內核現有的產品組合,并且宣布在今年稍晚點時候推出包括32位和64位內核的全系列新款MIPS...

2013-07-08 標簽:MIPSIP核Imagination 9830 0

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |