完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > Pcb layout

PCB印刷電路板,又稱印制電路板,作為電子元件的載體,實現(xiàn)了電子元器件之間的線路連接和功能實現(xiàn)。

PCB(Printed circuit board)印刷電路板,又稱印制電路板,作為電子元件的載體,實現(xiàn)了電子元器件之間的線路連接和功能實現(xiàn)。傳統(tǒng)的電路板工藝,采用了印刷蝕刻阻劑的工法,做出電路的線路及圖面,因此被稱為印制電路板或印刷線路板。

特性

21世紀(jì)人類進(jìn)入了信息化社會,電子產(chǎn)業(yè)得到了飛速發(fā)展,人們的工作生活和各種電子產(chǎn)品密不可分。而作為電子產(chǎn)品不可缺少的重要載體-PCB,也扮演了日益重要的角色。電子設(shè)備呈現(xiàn)高性能、高速、輕薄的趨勢,PCB作為多學(xué)科行業(yè)已成為電子設(shè)備最關(guān)鍵技術(shù)之一。PCB行業(yè)在電子互連技術(shù)中占有舉足輕重的地位。

PCB(Printed circuit board)印刷電路板,又稱印制電路板,作為電子元件的載體,實現(xiàn)了電子元器件之間的線路連接和功能實現(xiàn)。傳統(tǒng)的電路板工藝,采用了印刷蝕刻阻劑的工法,做出電路的線路及圖面,因此被稱為印制電路板或印刷線路板。

特性

21世紀(jì)人類進(jìn)入了信息化社會,電子產(chǎn)業(yè)得到了飛速發(fā)展,人們的工作生活和各種電子產(chǎn)品密不可分。而作為電子產(chǎn)品不可缺少的重要載體-PCB,也扮演了日益重要的角色。電子設(shè)備呈現(xiàn)高性能、高速、輕薄的趨勢,PCB作為多學(xué)科行業(yè)已成為電子設(shè)備最關(guān)鍵技術(shù)之一。PCB行業(yè)在電子互連技術(shù)中占有舉足輕重的地位。

PCB設(shè)計流程

常規(guī)PCB設(shè)計包括建庫、調(diào)網(wǎng)表、布局、布線、文件輸出等幾個步驟,但常規(guī)PCB設(shè)計流程已經(jīng)遠(yuǎn)遠(yuǎn)不能滿足日益復(fù)雜的高速PCB設(shè)計要求。由于SI仿真、PI仿真、EMC設(shè)計、單板工藝等都需要緊密結(jié)合到設(shè)計流程中,同時為了實現(xiàn)品質(zhì)控制,要在各節(jié)點增加評審環(huán)節(jié),實際的PCB設(shè)計流程要復(fù)雜得多。圖中為PCB設(shè)計公司一博科技的較典型的PCB設(shè)計流程,能更好地解決高速設(shè)計帶來的問題。

如何學(xué)習(xí)PCB layout

任務(wù)學(xué)習(xí)PCB Layout至少需要掌握的幾點:

(1)電路的基本原理,可以參考《電路分析基礎(chǔ)》。

(2)選擇Design 工具,推薦cadence,我也用過AD,個人感覺還是Cadence更強(qiáng)大順手。而且你本人想拿尖端科技的電路板,我不知道如何定義尖端,其實一個PCB 最挑戰(zhàn)的地方還是設(shè)計和成本Fab能力之間的矛盾,幾十層板(目前做過最多的48層,最少的24層),小的pin pitch,狹小的走線空間,苛刻信號質(zhì)量要求,繁瑣的走線約束,完成過后還有一些列的檢查,而這些工作我相信用Cadence來完成會更方便輕松。

(3)會利用cadence畫原理圖,這點很重要,如果不知道電路原理,其實你很難做一個好的Placement(我不知道這個詞語是否通用,所以還是解釋一下:原理圖的器件在PCB的實際布局),本人覺得一個好的Placement其實就完成了一個PCB設(shè)計的一大半了。

(4)會根據(jù)原理圖利用好PCB的空間,做合理的Placement,保證最好的信號路徑,最大的信號走線空間。做完P(guān)lacement后調(diào)整好silk,這可是最后板子做出來的臉面。

(5)會設(shè)計PCB的stackup,一個合理最優(yōu)的(不犧牲信號質(zhì)量的前提下,兼顧成本和走線復(fù)雜度,因為肯定層越多線越好走,但是成本越高)。設(shè)計走線約束規(guī)則,然后就是完成Layout。

(個人覺得其實Layout在這個完整的過程中是最簡單的,因為在約束條件下,只要稍微有些經(jīng)驗就可以完成最后的layout工作)

(6)知道Fab廠家的實際Fab能力,當(dāng)然你得清楚你的PCB做出來,廠家能否生成(如果你設(shè)計出100層的板子(就算有估計也是天價),我不知道哪個廠家可以生成出來,我目前知道身邊最多Fab的也就60多層(40x60cm 10多W美金),還沒聽過70層的)

(7)會做報價,知道每項Fab的收費,疊層,盲孔,埋孔,塞孔,背鉆,加工精度,鉆孔比要求,線寬等等,可以在原理圖初期就估算出報價,甚至在設(shè)計時把成本考慮進(jìn)去,使最后的產(chǎn)品具有價格競爭力。

(8)完成PCB后會檢查,包括阻抗匹配等長線寬檢查,電源線負(fù)載能力檢查,重復(fù)走線檢查,短路斷路檢查,信號回流路徑檢查等等關(guān)于信號的檢查,還有實際的Fab能力檢查,線寬檢查,線間距,線孔距等等。

(9)生成Fab文件,交由Fab廠家生產(chǎn)。

(10)上面還遺漏了一點,就BOM選項,根據(jù)原理圖,考慮器件的成本供貨周期,對Placement影響情況(如果都是相同參數(shù)的電阻,大多數(shù)情況下我愿意選擇小尺寸的,因為可以節(jié)約PCB空間)選擇最合適的器件。

總結(jié):雖然樓主只是問了Layout問題,但是這些看似和Layout無關(guān)的部分其實,是Layout不可或缺的部分,如果你要開自己的公司這些你不可能不知道,就算只是代工Layout,也許不需要Placement甚至設(shè)置約束條件,但是這些一定是必不可少的。

PCB Layout初學(xué)者必會知識總結(jié)

PCB是印刷電路板(即Printed Circuit Board)的簡稱。印刷電路板是組裝電子零件用的基板,是在通用基材上按預(yù)定設(shè)計形成點間連接及印制元件的印制板。該產(chǎn)品的主要功能是使各種電子零組件形成預(yù)定電路的連接,起中繼傳輸?shù)淖饔茫请娮赢a(chǎn)品的關(guān)鍵電子互連件,有“電子產(chǎn)品之母”之稱。

本內(nèi)容為pcb layout初學(xué)者整理了相關(guān)的技術(shù)點及設(shè)計經(jīng)驗、技巧等知識,方便初學(xué)者快速上手。

一、pcb layout是什么

PCB是印刷電路板(即Printed Circuit Board)的簡稱。印刷電路板是組裝電子零件用的基板,是在通用基材上按預(yù)定設(shè)計形成點間連接及印制元件的印制板。該產(chǎn)品的主要功能是使各種電子零組件形成預(yù)定電路的連接,起中繼傳輸?shù)淖饔茫请娮赢a(chǎn)品的關(guān)鍵電子互連件,有“電子產(chǎn)品之母”之稱。印刷電路板作為電子零件裝載的基板和關(guān)鍵互連件,任何電子設(shè)備或產(chǎn)品均需配備。其下游產(chǎn)業(yè)涵蓋范圍相當(dāng)廣泛,涉及一般消費性電子產(chǎn)品、信息、通訊、醫(yī)療,甚至航天科技(資訊 行情 論壇)產(chǎn)品等領(lǐng)域。隨著科學(xué)技術(shù)的發(fā)展,各類產(chǎn)品的電子信息化處理需求逐步增強(qiáng),新興電子產(chǎn)品不斷涌現(xiàn),使PCB產(chǎn)品的用途和市場不斷擴(kuò)展。新興的3G手機(jī)、汽車電子、LCD、IPTV、數(shù)字電視、計算機(jī)的更新?lián)Q代還將帶來比現(xiàn)在傳統(tǒng)市場更大的PCB市場。

LAYOUT是布局規(guī)劃的意思。

結(jié)合起來:PCB LAYOUT就是印刷電路板布局布線的中文意思。

二、Pcb layout基礎(chǔ)之常用電子元器件英文

特別是在用PADS9.3或者allegro16.3畫原理圖時,了解常用電子元器件英文是不可少的一個環(huán)節(jié)。經(jīng)常我們用一個零件的前三個英文字母來代替一個零件,pcb設(shè)計培訓(xùn)中例如:電阻用RES,電容用CAP,電感用IND,……等等。下面列舉了一些相信能幫助你。

電壓 voltage

電流 current

歐姆 Ohm

伏特 Volt

安培 Ampere

瓦特 Watt

電路 circuit

電路元件 circuit element,

電阻 resistance

電阻器 resistor

電感 inductance

電感器 inductor

電容 capacitance

電容器 capacitor

歐姆定律 Ohm’s law

基爾霍夫定律 Kirchhoff’s law

基爾霍夫電壓定律 Kirchhoff’s voltage law(KVL)

基爾霍夫電流定律 Kirchhoff’s current law(KCL)

回路 loop

網(wǎng)絡(luò) network

無源二端網(wǎng)絡(luò) passive two-terminal network

有源二端網(wǎng)絡(luò) active two-terminal network

三、pcb layout中必須要考慮的問題

pcb設(shè)計畫電路邊框,邊框線與元件引腳焊盤最短距離不能小于2MM,(一般取5MM較合理)否則下料困難。同一電路板中,電源線。地線比信號線粗。

元件布局原則

一般原則:在PCB設(shè)計中,如果電路系統(tǒng)同時存在數(shù)字電路和模擬電路.pcblayout培訓(xùn)以及大電流電路,則必須分開布局,使各系統(tǒng)之間藕合達(dá)到最小在同一類型電路中,按信號流向及功能,分塊,分區(qū)放置元件。

輸入信號處理單元,輸出信號驅(qū)動元件應(yīng)靠近pcb設(shè)計培訓(xùn)電路板邊,使輸入輸出信號線盡可能短,以減小輸入輸出的干擾。

元件放置方向: 元件只能沿水平和垂直兩個方向排列。否則不得于插件。 當(dāng)元件間電位差較大時,元件間距應(yīng)足夠大,防止出現(xiàn)放電現(xiàn)象。

元件間距。對于中等密度板,小元件,如小功率電阻,電容,二極管,等分立元件彼此的間距與插件,焊接工藝有關(guān),波峰焊接時,元件間距可以取50-100MIL(1.27–2.54MM)手工可以大些,如取100MIL,集成電路芯片,元件間距一般為100–150MIL在而已進(jìn)IC去藕電容要靠近芯片的電源秋地線引腳。不然濾波效果會變差。在數(shù)字電路中,為保證數(shù)字電路系統(tǒng)可靠工作,

在每一數(shù)字集成電路芯片的電源和地之間均放置IC去藕電容。去藕電容一般采用瓷片電容,容量為0.01~0.1UF去藕電容容量的選擇一般按系統(tǒng)工作頻率F的倒數(shù)選擇。此外,在電路電源的入口處的電源線和地線之間也需加接一個10UF的電容,以及一個0.01UF的瓷片電容。

時鐘電路元件盡量靠近單片機(jī)芯片的時鐘信號引腳,以減小時鐘電路的連線長度。且下面最好不要走線。剛印刷導(dǎo)線電阻大,線上的電壓降也就大,影響電路的性能, 線寬太寬,則布線密度不高,板面積增加,除了增加成本外,也不利于小型化。

如果電流負(fù)荷以20A/平方毫米計算,當(dāng)覆銅箔厚度為0.5MM時,(一般為這么多,)則1MM(約40MIL)線寬的電流負(fù)荷為1A,因此,線寬取1–2.54MM(40–100MIL)能滿足一般的應(yīng)用要求,大功率設(shè)備板上的地線和電源,根據(jù)功率大小,可適當(dāng)增加線寬,而在小功率的數(shù)字電路上,為了提高布線密度,最小線寬取0.254–1.27MM(10–15MIL)就能滿足。

四、pcb layout工程師應(yīng)該熟悉的幾種模塊

下面是在pcb設(shè)計中經(jīng)常會碰到的幾個模塊,作為一個pcb layout工程師應(yīng)該對這些熟悉。

I-mode 和 CHTML

i-mode是日本電信(NTT)的子公司DoCoMo在日本市場推出的無線通訊服務(wù)。是目前世界上使用人數(shù)最多(都在日本)的無線互聯(lián)網(wǎng)服務(wù)。I-mode 和 WAP

的主要區(qū)別在于:I-mode 的內(nèi)容是用CHTML寫成的,因此現(xiàn)行的大部分網(wǎng)絡(luò)內(nèi)容只要稍做修改可以使用;而WAP使用的是WML,pcb

layout培訓(xùn)現(xiàn)有的網(wǎng)絡(luò)內(nèi)容必須轉(zhuǎn)化為WML才能被WAP所使用。

CHTML(Compact HTML)HTML的一種變體。與HTML大部分兼容。

-----------

藍(lán)牙(BlueTooth)

藍(lán)牙是一種支持設(shè)備短距離通信(一般是10m之內(nèi))的無線電技術(shù)。pcb

layout設(shè)計培訓(xùn)能在包括移動電話、PDA、無線耳機(jī)、筆記本電腦、相關(guān)外設(shè)等眾多設(shè)備之間進(jìn)行無線信息交換。它的標(biāo)準(zhǔn)是IEEE802.15。工作在 2.4HGz

頻帶。帶寬為1Mb/s

(注:藍(lán)牙這名字很有意思,來自公元10世紀(jì)統(tǒng)一丹麥和瑞典的斯堪的納維亞國王的名字。)

-----------

Wireless LAN

無線局域網(wǎng),是由局域網(wǎng)發(fā)展而來,標(biāo)準(zhǔn)是IEEE802.11、IEEE802.11b 和IEEE802.11a。其中802.11b

工作在2.4GHz頻帶,帶寬可達(dá)11Mbps。而802.11a定義在5GHz頻帶,帶寬有望達(dá)到54Mb/s 。但相應(yīng)地,Wireless

HomeRF

HomeRF主要為家庭網(wǎng)絡(luò)設(shè)計的無線射頻技術(shù),是IEEE802.11與DECT的結(jié)合,旨在降低成本。HomeRF也采用了擴(kuò)頻技術(shù),工作在2.4GHz頻帶,目前HomeRF的帶寬為1~2Mb/s,未來會增到10Mb/s。

-----------

SyncML

SyncML是一種行業(yè)通用的移動數(shù)據(jù)同步化協(xié)議。利用SyncML可使移動設(shè)備上的數(shù)據(jù)與遠(yuǎn)程數(shù)據(jù)保持同步狀態(tài)。由Ericsson、 IBM、 Lotus、

Matsushita、Motorola、 Nokia、 Palm、 Psion和Starfish Software等公司組成的協(xié)會所開發(fā)。

五、pcb layout基礎(chǔ)之電源、地線的處理

對每個從事電子產(chǎn)品設(shè)計的工程人員來說都明白地線與電源線之間噪音所產(chǎn)生的原因,pcblayout既使在整個PCB板中的布線完成得都很好,但由于電源、 地線的考慮不周到而引起的干擾,會使產(chǎn)品的性能下降,有時甚至影響到產(chǎn)品的成功率。所以對電、地線的布線要認(rèn)真對待,把電、地線所產(chǎn)生的噪音干擾降到最低限度,以保證產(chǎn)品的質(zhì)量。 現(xiàn)只對降低式抑制噪音作以表述:

A、用大面積銅層作地線用,在印制板上把沒被用上的地方都與地相連接作為地線用。pcb設(shè)計培訓(xùn)或是做成多層板,電源,地線各占用一層。

B、眾所周知的是在電源、地線之間加上去耦電容。

C、盡量加寬電源、地線寬度,最好是地線比電源線寬,它們的關(guān)系是:地線》電源線》信號線,pcb設(shè)計通常信號線寬為:0.2~0.3mm,最經(jīng)細(xì)寬度可達(dá)0.05~0.07mm,電源線為1.2~2.5mm

對數(shù)字電路的PCB可用寬的地導(dǎo)線組成一個回路, 即構(gòu)成一個地網(wǎng)來使用(模擬電路的地不能這樣使用)。

六、pcb layout必須要了解EMI的三要素

只有先了解才有可能去避免它,減少它在電路中的危害。EMC電磁兼容是pcb layout必須的一課。不知道如何減少EMI,那么這樣做pcb layout是沒有很大價值的

電磁干擾三要素:

騷擾源

耦合途徑

敏感設(shè)備

為了實現(xiàn)電磁兼容,必須從上面三個基本要素出發(fā),運用技術(shù)和組織兩方面措施。

所謂技術(shù)措施,就是從分析電磁騷擾源、耦合途徑和敏感設(shè)備著手,采取有效的 技術(shù)手段,抑制騷擾源、消除或減弱騷擾的耦合、降低敏感設(shè)備對騷擾的響應(yīng)或增加電磁敏感性電平;

為了對人為騷擾進(jìn)行限制,并驗證所采用的技術(shù)措施的有效性,還必須采取組織措施,制定和遵循一套完整的標(biāo)準(zhǔn)和規(guī)范,進(jìn)行合理的頻譜分配,控制與管理頻譜的使用,依據(jù)頻率、工作時間、天線方向性等規(guī)定工作方式,分析電磁環(huán)境并選擇布置地域,進(jìn)行電磁兼容性管理等。

電磁騷擾源:任何形式的自然或電能裝置所發(fā)射的電磁能量,能使共享同一環(huán)境的人或其它生物受到傷害,或使其它設(shè)備、分系統(tǒng)或系統(tǒng)發(fā)生電磁危害,導(dǎo)致性能降低或失效,即稱為電磁騷擾源。

耦合途徑:即傳輸電磁騷擾的通路或媒介。

敏感設(shè)備(Victim): 是指當(dāng)受到電磁騷擾源所發(fā)射的電磁量的作用時,會受到傷害的人或其它生物,以及會發(fā)生電磁危害,導(dǎo)致性能降低或失效的器件、設(shè)備、分系統(tǒng)或系統(tǒng)。許多器件、設(shè)備、分系統(tǒng)或系統(tǒng)可以既是電磁騷擾源又是敏感設(shè)備。

七、pcb layout初學(xué)者如何理解差分信號

什么是差分信號? 通俗地說,就是驅(qū)動端發(fā)送兩個等值、反相的信號,接收端通過比較這兩個電壓的差值來判斷邏輯狀態(tài)“0”還是“1”。而承載差分信號的那一對線就稱為差分線。差分線阻抗怎么算?各種差分信號的阻抗都不一樣的,比如USB的D+ D-,差分線阻抗是90ohm,1394的差分線是110ohm,最好先看看規(guī)格書或者相關(guān)資料。現(xiàn)在已經(jīng)有很多計算阻抗工具,比如polar的si9000,影響差分阻抗的因素有線寬、差分線間距、介質(zhì)介電常數(shù)、介質(zhì)的厚度(差分線到參考面之間的介質(zhì)厚度),一般是調(diào)整差分線間距和線寬來控制差分阻抗的。做板的時候也要跟廠家說明哪些線要控制阻抗。一個差分信號是用一個數(shù)值來表示兩個物理量之間的差異。從嚴(yán)格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統(tǒng)里,系統(tǒng)‘地’被用作電壓基準(zhǔn)點。當(dāng)‘地’當(dāng)作電壓測量基準(zhǔn)時,這種信號規(guī)劃被稱之為單端的。我們使用該術(shù)語是因為信號是用單個導(dǎo)體上的電壓來表示的。

對于 PCB LAYOUT工程師來說,最關(guān)注的還是如何確保在實際走線中能完全發(fā)揮差分走線的這些優(yōu)勢。也許只要是接觸過 Layout 的人都會了解差分走線的一般要求,pcb設(shè)計那就是“等長、等距”。等長是為了保證兩個差分信號時刻保持相反極性,減少共模分量;等距則主要是為了保證兩者差分阻抗一致,減少反射。“盡量靠近原則”有時候也是差分走線的要求之一。 差分走線也可以走在不同的信號層中,但一般不建議這種走法,因為不同的層產(chǎn)生的諸如阻抗、過孔的差別會破壞差模傳輸?shù)男Ч牍材T肼暋4送猓绻噜弮蓪玉詈喜粔蚓o密的話,會降低差分走線抵抗噪聲的能力,但如果能保持和周圍走線適當(dāng)?shù)拈g距,串?dāng)_就不是個問題。在一般頻率(GHz 以下),EMI 也不會是很嚴(yán)重的問題,實驗表明,相距 500Mils 的差分走線,在3 米之外的輻射能量衰減已經(jīng)達(dá)到 60dB,足以滿足 FCC 的電磁輻射標(biāo)準(zhǔn),所以設(shè)計者根本不用過分擔(dān)心差分線耦合不夠而造成電磁不兼容問題。但所有這些規(guī)則都不是用來生搬硬套的,不少工程師似乎還不了解高速差分信號傳輸?shù)谋举|(zhì)。下面重點討論一下 PCB 差分信號設(shè)計中幾個常見的誤區(qū)。

認(rèn)為差分走線一定要靠的很近。讓差分走線靠近無非是為了增強(qiáng)他們的耦合,既可以提高對噪聲的免疫力,還能充分利用磁場的相反極性來抵消對外界的電磁干擾。雖說這種做法在大多數(shù)情況下是非常有利的,但不是絕對的,如果能保證讓它們得到充分的屏蔽,不受外界干擾,那么我們也就不需要再讓通過彼此的強(qiáng)耦合達(dá)到抗干擾和抑制 EMI 的目的了。如何才能保證差分走線具有良好的隔離和屏蔽呢?增大與其它信號走線的間距是最基本的途徑之一,電磁場能量是隨著距離呈平方關(guān)系遞減的,一般線間距超過4 倍線寬時,它們之間的干擾就極其微弱了,基本可以忽略。此外,通過地平面的隔離也可以起到很好的屏蔽作用,這種結(jié)構(gòu)在高頻的(10G 以上)IC 封裝PCB 設(shè)計中經(jīng)常會用采用,被稱為 CPW 結(jié)構(gòu),可以保證嚴(yán)格的差分阻抗控制(2Z0)。

我實際工作的體會:

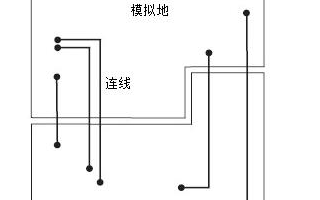

如圖,大電流的模塊要挨近電源,弱電走向強(qiáng)電;數(shù)字地、模擬地一點共地;高頻的器件電源線、地線要避免長線;每個數(shù)字 ic 電源腳與接地腳之間,以最短路徑焊接高頻濾波電容,如 CC1 高頻瓷介電容,重要部位加鉭電容濾波。干擾大的部位用示波器就可以看清楚。

Layout軟件Altium、Cadence、Mentor對比

國內(nèi)的EDA軟件市場幾乎被三家瓜分,分別是Altium、Cadence、Mentor,也是我們這次主要分析和比較的軟件。除此之外還有很多小眾的Layou...

開關(guān)電源PCB Layout的電路要求和EMI要求

PCB Layout是開關(guān)電源研發(fā)過程中的極為重要的步驟和環(huán)節(jié),關(guān)系到開關(guān)電源能否正常工作,生產(chǎn)是否順利進(jìn)行

2018-04-06 標(biāo)簽:EMIpcb layout開關(guān)電源PCB 1.1萬 0

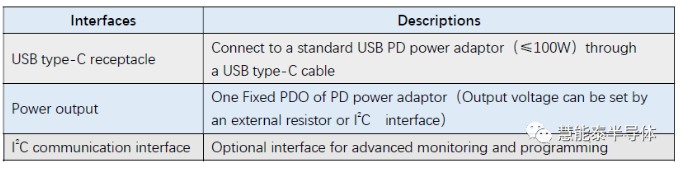

User Guide for the HUSB238 USB PD Sink Reference Design Board

The HUSB238 is a highly integrated USB Power Delivery (PD) controller as sin...

2021-02-23 標(biāo)簽:Pcb layoutUSB PD 8487 0

PCB layout需要豐富的經(jīng)驗和扎實的理論基礎(chǔ)支持,還要多踩幾個坑,多做幾個仿真加深對走線的理解,才能形成閉環(huán)的走線設(shè)計。

2022-07-19 標(biāo)簽:電路板地線Pcb layout 3840 0

pcb layout 前必須考慮的“5種”生產(chǎn)工藝

單層板還是雙層板?2、是全直插還是直插加貼片?3、工廠是否支持紅膠工藝

2019-09-20 標(biāo)簽:生產(chǎn)工藝Pcb layout 3737 0

旁路電容的選取對各Buck輸入/輸出 noise,輸出電壓性能有重要影響。現(xiàn)在的Buck DC regulator采用PFM (Pulse Freque...

2020-12-14 標(biāo)簽:WLAN藍(lán)牙芯片Pcb layout 3415 0

PCB layout設(shè)計需要遵行的七大規(guī)則介紹

線路層設(shè)計有網(wǎng)格的板子(鋪銅鋪成網(wǎng)格狀的),網(wǎng)格空處矩形大于等于10*10mil,就是在鋪銅設(shè)置時line spacing不要小于10mil,網(wǎng)格線寬大...

2019-09-27 標(biāo)簽:PCB設(shè)計Pcb layout 3371 0

如果沒有注意數(shù)字地和模擬的分割情況,直接分割成兩部分,會引起多種始料未及的情況,甚至?xí)a(chǎn)生分割后出現(xiàn)的噪聲更大,所以在使用地平面分割的時候,需要認(rèn)真的考...

貼片元器件之間的間距是工程師在layout時必須注意的一個問題,如果間距太小焊膏印刷和避免焊接連錫難度非常大。

2022-12-30 標(biāo)簽:元器件電解電容Pcb layout 3123 0

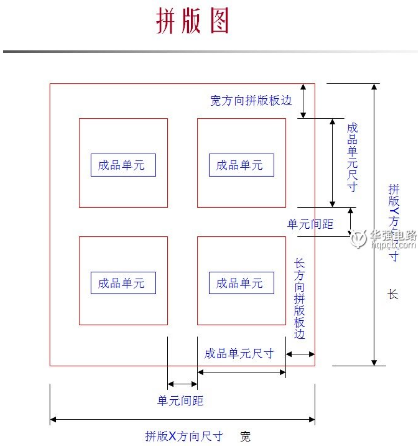

其次就是不同工程師設(shè)計的PCB板承載的信息是不一樣的,其板子的大小也就各不相同,5CMX5CM,10CMX10CM 等等各種尺寸的都有!而加工PCB的生...

2019-07-12 標(biāo)簽:PCB拼板Pcb layout 2706 0

原創(chuàng)看圖快速學(xué)PADS_LAYOUT_PCB拼板教程立即下載

類別:PCB設(shè)計規(guī)則 2012-11-16 標(biāo)簽:PADSPCB LAYOUT

類別:電子教材 2012-03-15 標(biāo)簽:pcb layout

類別:PCB設(shè)計規(guī)則 2013-09-13 標(biāo)簽:PCBPCB LAYOUT

類別:電源技術(shù) 2014-03-31 標(biāo)簽:Pcb layout

神速-三天學(xué)會PADS PCB Layout立即下載

類別:PCB設(shè)計規(guī)則 2012-11-16 標(biāo)簽:PADSPCB Layout

走線規(guī)則技巧及PCB制程培訓(xùn)講座立即下載

類別:PCB設(shè)計規(guī)則 2015-10-23 標(biāo)簽:PCB制程ECADPCB LAYOUT

類別:PCB設(shè)計規(guī)則 2013-07-07 標(biāo)簽:PCB_layout

類別:PCB設(shè)計規(guī)則 2012-07-12 標(biāo)簽:展訊PCB Layout

類別:電源技術(shù) 2021-11-07 標(biāo)簽:電源設(shè)計Pcb layout

全!268條PCB Layout設(shè)計規(guī)范!

2019-08-19 標(biāo)簽:PCBPCB打樣Pcb layout 1.2萬 0

本內(nèi)容介紹了pcb layout中IC常用封裝,了解這些常識對PCB LAYOUT是有幫助的。下面還將介紹幾種IC封裝。

2011-11-09 標(biāo)簽:pcbIC封裝pcb layout 8519 0

在pcb layout中我們可以從下面的幾點來分析一下PCI,PCI總線的布線有什么殊要求,如何做好PCI總線的布線,首先,PCI系統(tǒng)是一個同步時序的體...

作為一個PCB LAYOUT工程師必須了解ICT飛針在線測試,這樣對在PCB設(shè)計過程中加測試點的意義就很清楚了。很多公司要求ICT測試點要能加到95%以...

2011-11-09 標(biāo)簽:飛針測試PCB LAYOUTICT測試 5842 0

本內(nèi)容為pcb layout初學(xué)者整理了相關(guān)的技術(shù)點及設(shè)計經(jīng)驗、技巧等知識,方便初學(xué)者快速上手。

2012-07-04 標(biāo)簽:pcbpcb layout 5755 0

介紹了PCB Layout零件布局走線的一般原則,數(shù)字信號走線盡量放置在數(shù)字信號布線區(qū)域內(nèi)等知識

2012-06-25 標(biāo)簽:PCBPCB走線PCB Layout 5528 0

作為一個PCB設(shè)計人員,不能只了解自己所做的MID方案,應(yīng)該適當(dāng)擴(kuò)展自己的視野,了解跟多的相關(guān)知識

2011-11-09 標(biāo)簽:PcbMIDPcb layout 4679 0

全!268條PCB Layout設(shè)計規(guī)范!

2019-08-20 標(biāo)簽:pcbPcb layout 4534 0

【原創(chuàng)】PCB Layout必須遵循的“33條規(guī)矩”!

2019-08-20 標(biāo)簽:pcbPcb layout 4397 0

pcblayout既使在整個PCB板中的布線完成得都很好,但由于電源、 地線的考慮不周到而引起的干擾,會使產(chǎn)品的性能下降,有時甚至影響到產(chǎn)品的成功率。

2012-06-25 標(biāo)簽:pcbpcb layout 4360 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |