完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > pll

文章:379個 瀏覽:135135次 帖子:512個

同步降壓型DC/DC控制器LTC3855的性能特點(diǎn)及應(yīng)用范圍

凌力爾特公司 (Linear Technology Corporation) 推出的雙輸出高效率 (高達(dá) 95%) 同步降壓型 DC/DC 控制器 LT...

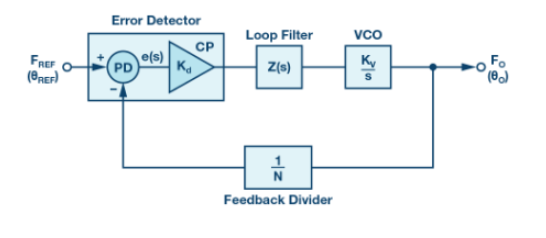

ADI ADF4xxx系列PLL經(jīng)典數(shù)字PLL架構(gòu)實(shí)現(xiàn)方案

基本配置:時鐘凈化電路 鎖相環(huán)的最基本配置是將參考信號(FREF)的相位與可調(diào)反饋信號(RFIN)F0的相位進(jìn)行比較,如圖1所示。 圖1. PLL基本配...

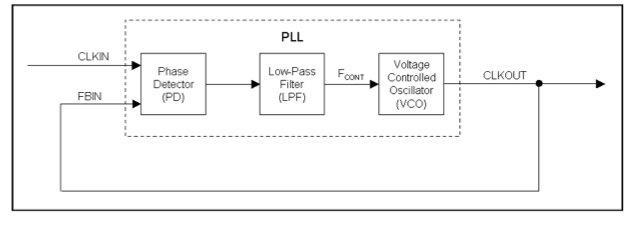

基于 PLL 的零延遲緩沖器的系統(tǒng)應(yīng)用

本應(yīng)用報(bào)告介紹了實(shí)現(xiàn) IDT 基于 PLL 的零延遲緩沖器的輸入?yún)⒖紩r鐘和輸出時鐘之間定義的相位關(guān)系的不同方法。該報(bào)告重點(diǎn)介紹了 PLL 反饋環(huán)路中不同...

LMK03000系列精密時鐘調(diào)理器的性能及作用分析

LMK03000系列精密時鐘調(diào)理器結(jié)合了抖動清除/修復(fù),乘法和分配參考時鐘的功能。這些器件集成了壓控振蕩器(VCO),高性能整數(shù)N鎖相環(huán)(PLL),部分...

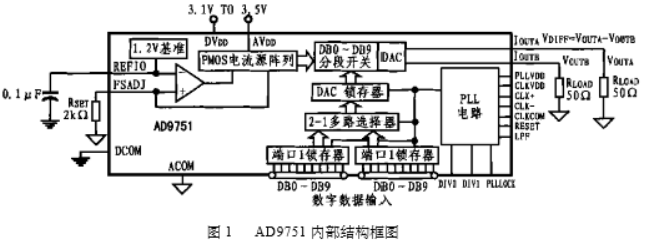

超高速10位CMOS D/A轉(zhuǎn)換器AD9751的原理、特點(diǎn)及應(yīng)用設(shè)計(jì)

AD9751是一個雙輸入端口的超高速10位CMOS DAC。它內(nèi)含一個高性能的10位D/A內(nèi)核、一個基準(zhǔn)電壓和一個數(shù)字接口電路。當(dāng)AD9751工作于30...

2020-10-20 標(biāo)簽:轉(zhuǎn)換器dacpll 4002 0

ADMV8416/ADMV8432與PLL/VCO IC配合實(shí)現(xiàn)PLL/VCO技術(shù)的提升

多年來,微波頻率生成使工程師面臨嚴(yán)峻的挑戰(zhàn),不僅需要對模擬、數(shù)字、射頻(RF)和微波電子有深入的了解,尤其是鎖相環(huán)(PLL)和壓控振蕩器(VCO)集成電...

隨著相關(guān)工藝、電路和封裝技術(shù)的各種創(chuàng)新,頻率生成技術(shù)不斷發(fā)展,能夠?yàn)橛脩籼峁┍纫郧暗姆至⑹浇鉀Q方案的體積更小、功能和性能更出色的解決方案。

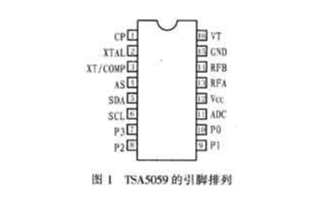

單片PLL頻率合成器TSA5059的特點(diǎn)性能及典型應(yīng)用電路

TSA5059是專門為數(shù)字衛(wèi)星接收機(jī)的調(diào)諧系統(tǒng)設(shè)計(jì)的單片PLL頻率合成器,它的工作頻率可達(dá)2.7GHz,供電電壓為5V±10%,電源電流為45mA。輸入...

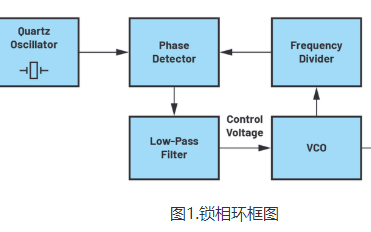

鎖相環(huán)PLL電路是如何實(shí)現(xiàn)的

鎖相環(huán)(PLL)電路是由壓控振蕩器(VCO)和鑒相器組成的反饋系統(tǒng),振蕩器信號跟蹤施加的頻率或相位調(diào)制信號是否具有正確的頻率和相位。需要從固定低頻率信號...

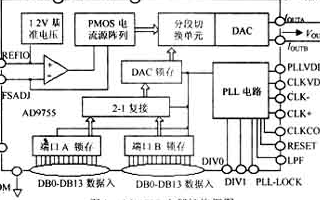

超高速14位數(shù)模轉(zhuǎn)換芯片AD9755的性能特點(diǎn)和應(yīng)用分析

AD9755主要由兩組14位數(shù)據(jù)輸入接口、2-1復(fù)接器、DAC鎖存器、基準(zhǔn)電壓、PMOS電流源陣列、分段切換器、PLL電路以及DAC單元等構(gòu)成,其內(nèi)部結(jié)...

利用PLL芯片ADF4360_4的本振信號源的參數(shù)和方案設(shè)計(jì)

鎖相(Phase Lock)技術(shù)是一種相位負(fù)反饋頻率控制技術(shù),該技術(shù)在鎖定時無剩余頻差,并具有良好的窄帶載波跟蹤性能和帶寬調(diào)制跟蹤性能,而且對相位噪聲和...

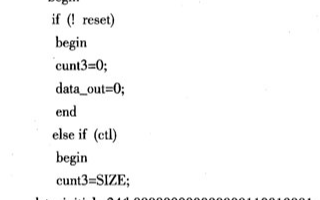

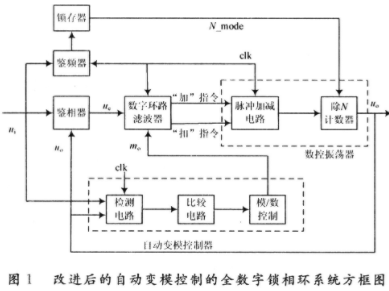

自動變模控制PLL的工作原理和功能實(shí)現(xiàn)設(shè)計(jì)

目前數(shù)字鎖相環(huán)在數(shù)字通信、雷達(dá)、無線電電子學(xué)、儀表儀器、高速計(jì)算機(jī)及導(dǎo)航系統(tǒng)中得到了廣泛的應(yīng)用。與傳統(tǒng)的模擬鎖相環(huán)相比,全數(shù)字鎖相環(huán)克服了模擬鎖相環(huán)易受...

2020-08-12 標(biāo)簽:計(jì)算機(jī)pll計(jì)數(shù)器 1982 0

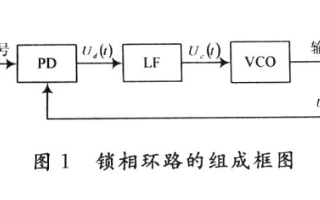

鎖相環(huán)路的組成、的基本特性和應(yīng)用分析

鎖相環(huán)路(Phase Lock Loop,PLL)是一種自動相位控制(APC)系統(tǒng),是現(xiàn)代電子系統(tǒng)中應(yīng)用廣泛的一個基本部件。它的基本作用是在環(huán)路中產(chǎn)生一...

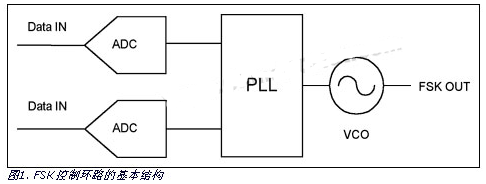

使用兩片MAX176 ADC實(shí)現(xiàn)FSK控制回路的設(shè)計(jì)

本文給出了快速響應(yīng)FSK控制環(huán)路模擬前端的詳細(xì)設(shè)計(jì)方案。用兩片MAX176 ADC分別量化兩個輸入通道并控制FSK調(diào)制器的PLL。這一獨(dú)特、簡單的結(jié)構(gòu)將...

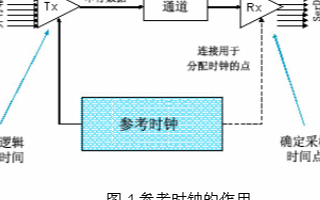

E5052B信號源分析儀的時鐘抖動分析的測量技術(shù)研究

發(fā)射機(jī)必須用適當(dāng)?shù)囊驍?shù)乘以參考時鐘獲得數(shù)據(jù)速率,才能確定邏輯變換定時。例如,對于100 MHz參考時鐘和5 Gb/s輸出信號,發(fā)射機(jī)將用PLL給參考時鐘...

用于實(shí)現(xiàn)高品質(zhì)全速測試程序的方法建議

LinkedIn全速測試在大量新功能的協(xié)助下有了很大的改進(jìn),包括在測試模式期間使用芯片上產(chǎn)生的功能時脈。目前許多設(shè)計(jì)都工作在非常高的頻率,并包含許多時脈...

具有兩種測量功能的高性能頻譜分析儀FSU的設(shè)計(jì)

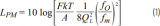

無線傳輸?shù)氖瞻l(fā)模塊的性能主要取決于所用本振的相位噪聲,因此模塊特性的準(zhǔn)確測量,特別是相位噪聲的測量,是進(jìn)行有效通信和廣播的基本保證。在常用的相位測量應(yīng)用...

基于高分辨率A/D轉(zhuǎn)換器和DL技術(shù)實(shí)現(xiàn)時鐘穩(wěn)定電路的設(shè)計(jì)

另外,在高分辨率A/D轉(zhuǎn)換器電路設(shè)計(jì)技術(shù)中,Σ-Δ電路結(jié)構(gòu)是目前很流行的一種電路設(shè)計(jì)技術(shù),這種電路結(jié)構(gòu)不僅在高分辨低速或中速A/D轉(zhuǎn)換器方面將逐步取代S...

2020-07-22 標(biāo)簽:轉(zhuǎn)換器flashpll 1166 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |