完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > System

system是一個(gè)C語(yǔ)言和C++下的函數(shù)。windows操作系統(tǒng)下system () 函數(shù)詳解主要是在C語(yǔ)言中的應(yīng)用,system函數(shù)需加頭文件《stdlib.h》后方可調(diào)用。

system是一個(gè)C語(yǔ)言和C++下的函數(shù)。windows操作系統(tǒng)下system () 函數(shù)詳解主要是在C語(yǔ)言中的應(yīng)用,system函數(shù)需加頭文件《stdlib.h》后方可調(diào)用。

system是一個(gè)C語(yǔ)言和C++下的函數(shù)。windows操作系統(tǒng)下system () 函數(shù)詳解主要是在C語(yǔ)言中的應(yīng)用,system函數(shù)需加頭文件《stdlib.h》后方可調(diào)用。

Windows函數(shù)

函數(shù)名: system功 能: 發(fā)出一個(gè)DOS命令用 法: int system(char *command);程序例:

8#include 《stdlib.h》

#include 《stdio.h》

int main(void)

{

printf(“About to spawn and run a DOS command\n”);

system(“dir”);

return 0;

}

又如:system(“pause”)可以實(shí)現(xiàn)凍結(jié)屏幕,便于觀察程序的執(zhí)行結(jié)果;system(“CLS”)可以實(shí)現(xiàn)清屏操作。而調(diào)用color函數(shù)可以改變控制臺(tái)的前景色和背景,具體參數(shù)在下面說(shuō)明。例如,用 system(“color 0A”); 其中color后面的0是背景色代號(hào),A是前景色代號(hào)。各顏色代碼如下:0=黑色 1=藍(lán)色 2=綠色 3=湖藍(lán)色 4=紅色 5=紫色 6=黃色 7=白色 8=灰色 9=淡藍(lán)色 A=淡綠色 B=淡淺綠色 C=淡紅色 D=淡紫色 E=淡黃色 F=亮白色(注意:Microsoft Visual C++6.0 支持system)顏色屬性由兩個(gè)十六進(jìn)制數(shù)字指定 -- 第一個(gè)對(duì)應(yīng)于背景,第二個(gè)對(duì)應(yīng)于前景。每個(gè)數(shù)字可以為以下任何值:0 = 黑色 8 = 灰色1 = 藍(lán)色 9 = 淡藍(lán)色

2 = 綠色 A = 淡綠色

3 = 淺綠色 B = 淡淺綠色

4 = 紅色 C = 淡紅色

5 = 紫色 D = 淡紫色

6 = 黃色 E = 淡黃色

7 = 白色 F = 亮白色舉例看了下面實(shí)例,相信你會(huì)對(duì)學(xué)到更多system在C程序設(shè)計(jì)中的應(yīng)用。例一:C語(yǔ)言調(diào)用DOS命令實(shí)現(xiàn)定時(shí)關(guān)機(jī):

39#include《stdio.h》

#include《string.h》

#include《stdlib.h》

int print()

{

printf(“ ╪╪╪╪╪╪╧╧╧╧╧╧╧╧╪╪╪╪╪╪\n”);

printf(“╔═══╧╧C語(yǔ)言關(guān)機(jī)程序 ╧╧═══╗\n”);

printf(“║※1.實(shí)現(xiàn)10分鐘內(nèi)的定時(shí)關(guān)閉計(jì)算機(jī) ║\n”);

printf(“║※2.立即關(guān)閉計(jì)算機(jī) ║\n”);

printf(“║※3.注銷計(jì)算機(jī) ║\n”);

printf(“║※0.退出系統(tǒng) ║\n”);

printf(“╚═══════════════════╝\n”);

return 0;

}

void main()

{

system(“title C語(yǔ)言關(guān)機(jī)程序”);//設(shè)置cmd窗口標(biāo)題

system(“mode con cols=48 lines=25”);//窗口寬度高度

system(“color 0B”);

system(“date /T”);

system(“TIME /T”);

char cmd[20]=“shutdown -s -t ”;

char t[5]=“0”;

print();

int c;

scanf(“%d”,&c);

getchar();

switch(c)

{

case 1:printf(“您想在多少秒后自動(dòng)關(guān)閉計(jì)算機(jī)?(0~600)\n”);scanf(“%s”,t);

system(strcat(cmd,t));break;

case 2:system(“shutdown -p”);break;

case 3:system(“shutdown -l”);break;

case 0:break;

default:printf(“Error!\n”);

}

system(“pause”);

exit(0);

}

例二:用C語(yǔ)言刪除文件,例如文件的位置是d:\123.txt用system()函數(shù)執(zhí)行windows命令。

7#include 《stdlib.h》

#include 《stdio.h》

int main(void)

{

system(“del d:\\123.txt”);

return 0;

}

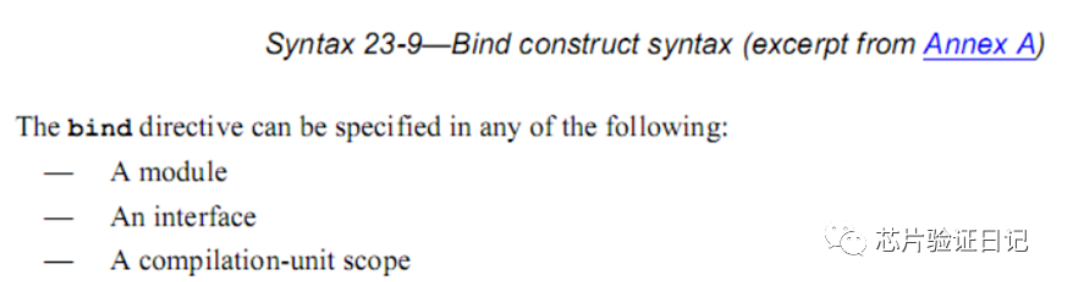

SystemVerilog中bind用法總結(jié)+送實(shí)驗(yàn)源碼和腳本

bind是systemverilog中一個(gè)重要的知識(shí)點(diǎn),很多時(shí)候能夠在驗(yàn)證中發(fā)揮重要的作用,今天就針對(duì)這個(gè)知識(shí)點(diǎn)做一個(gè)梳理,希望能幫助到大家。

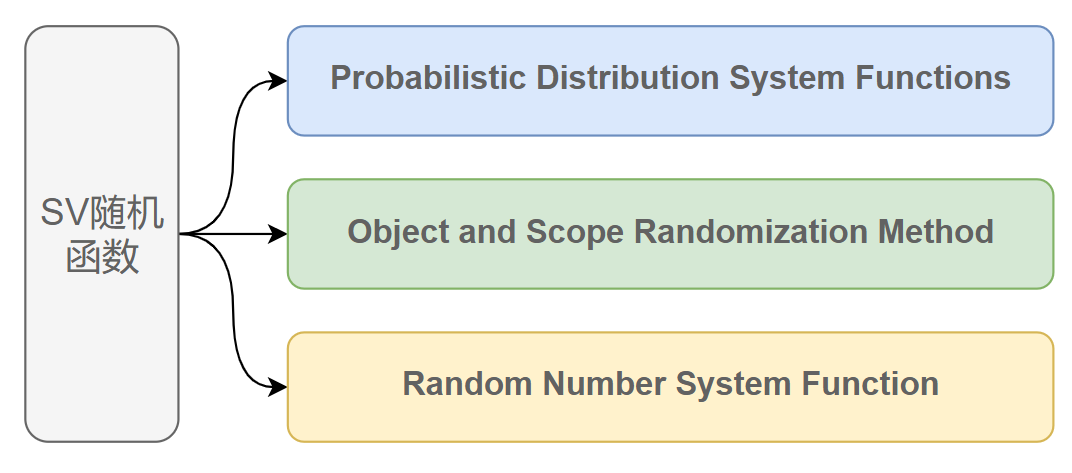

簡(jiǎn)述SystemVerilog的各種隨機(jī)化方法

我習(xí)慣將驗(yàn)證空間理解為:驗(yàn)證中原則上需要覆蓋的芯片所有有可能出現(xiàn)的工作狀態(tài)的集合。為了探索這片廣袤的驗(yàn)證空間,驗(yàn)證的時(shí)候搞出了帶有約束的隨機(jī)測(cè)試(con...

淺談SystemVerilog中的數(shù)據(jù)類型轉(zhuǎn)換

兩種形式實(shí)現(xiàn)的功能都是將源表達(dá)式src_exp轉(zhuǎn)換給目標(biāo)變量dest_var,那么既生瑜何生亮,實(shí)現(xiàn)的功能都一樣,在具體使用時(shí)仿真工具或者用戶如何知道使...

2022-09-28 標(biāo)簽:VerilogSystem數(shù)據(jù)類型 5151 0

SystemVerilog中“軟約束”與“硬約束”的應(yīng)用示例

示例中采用的是“硬約束”,因?yàn)槎x在類中的約束與隨機(jī)時(shí)指定的內(nèi)嵌約束“矛盾”,所以導(dǎo)致約束解析器解析隨機(jī)失敗,即“硬約束”要求所有相關(guān)的約束條件不能互相...

常用的時(shí)序反標(biāo)方法和EDA工具反標(biāo)方法

前段時(shí)間,一個(gè)朋友聊敘到這個(gè)后仿真任務(wù)命令都咋用,隨即整理了下,可以完成基本的后仿真不成問(wèn)題,但是如果還要完成一些其他的幺蛾子,那就需要各位仔細(xì)研讀各工...

隊(duì)列是大小可變的有序集合,隊(duì)列中元素必須是同一個(gè)類型的。隊(duì)列支持對(duì)其所有元素的訪問(wèn)以及在隊(duì)列的開(kāi)始或結(jié)束處插入和刪除。

SystemVerilog中的類構(gòu)造函數(shù)new

在systemverilog中,如果一個(gè)類沒(méi)有顯式地聲明構(gòu)造函數(shù)(new()),那么編譯仿真工具會(huì)自動(dòng)提供一個(gè)隱式的new()函數(shù)。這個(gè)new函數(shù)會(huì)默認(rèn)...

SystemVerilog中的關(guān)聯(lián)數(shù)組

關(guān)聯(lián)數(shù)組實(shí)際上是一種查找表,內(nèi)存空間直到被使用時(shí)才會(huì)分配,每個(gè)數(shù)據(jù)項(xiàng)都會(huì)有一個(gè)特定的“鍵(索引)”,索引的類型不局限于整型。

0

0

標(biāo)簽:Linux系統(tǒng)System 8565 0

System Management Bus(SMBus)Sp立即下載

類別:規(guī)則標(biāo)準(zhǔn) 2008-09-12 標(biāo)簽:System

如何使用System view數(shù)字調(diào)制進(jìn)行眼圖分析立即下載

類別:嵌入式開(kāi)發(fā) 2019-01-23 標(biāo)簽:二進(jìn)制通信系統(tǒng)System

LM81,datasheet,pdf(Serial Inte立即下載

類別:IC datasheet pdf 2009-10-22 標(biāo)簽:System

STM32的庫(kù)文件資料合集免費(fèi)下載立即下載

類別:C語(yǔ)言|源代碼 2019-05-21 標(biāo)簽:CORESTM32SYSTEM

基于SystemC構(gòu)建多核DSP軟件仿真平臺(tái)立即下載

類別:模擬數(shù)字論文 2017-01-03 標(biāo)簽:System多核DSP

基于SystemVerilog語(yǔ)言的驗(yàn)證方法學(xué)介紹立即下載

類別:C語(yǔ)言|源代碼 2011-05-09 標(biāo)簽:VerilogSystem驗(yàn)證方法

如何利用SystemVerilog仿真生成隨機(jī)數(shù)

采用SystemVerilog進(jìn)行仿真則更容易生成隨機(jī)數(shù),而且對(duì)隨機(jī)數(shù)具有更強(qiáng)的可控性。對(duì)于隨機(jī)變量,在SystemVerilog中可通過(guò)rand或ra...

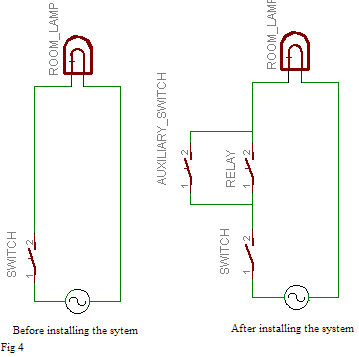

燈光控制系統(tǒng)電路,ht Control System

燈光控制系統(tǒng)電路,ht Control System It is easy to install a couple of infrared emitt...

利用模塊化建模方法實(shí)現(xiàn)基于System Generator的控制器導(dǎo)出并多軟硬件仿真驗(yàn)證

利用System Generator軟件平臺(tái),實(shí)現(xiàn)基于模塊化建模方法的變換器建模,并簡(jiǎn)化語(yǔ)言編寫控制系統(tǒng)的復(fù)雜過(guò)程。研究了從MATLAB-Xilinx環(huán)...

SystemVerilog是一種 硬件描述和驗(yàn)證語(yǔ)言 (HDVL),它 基于IEEE1364-2001 Verilog硬件描述語(yǔ)言(HDL),并對(duì)其進(jìn)行...

基于System Generator的Rife算法設(shè)計(jì)實(shí)現(xiàn)與仿真分析

在FPGA平臺(tái)上應(yīng)用System Generator工具實(shí)現(xiàn)了高精度頻率估計(jì)Rife算法。不同于傳統(tǒng)的基于HDL代碼和IP核的設(shè)計(jì)方法,采用System...

作者:limanjihe ?https://blog.csdn.net/limanjihe/article/details/83005713 Syste...

基于System Generator實(shí)現(xiàn)高速盲均衡器設(shè)計(jì)并闡述了MCMA算法的實(shí)現(xiàn)過(guò)程

基于System Generator軟件,在xc7z020-1clg484芯片上設(shè)計(jì)了一種高速盲均衡器。該盲均衡器由延遲模塊、濾波模塊、誤差計(jì)算模塊和...

Axiomtek宣布推出AIE100-903-FL-NX AI Edge System

NVIDIA Jetson為AIE100-903-FL-NX AI邊緣系統(tǒng)提供動(dòng)力,該系統(tǒng)使用帶有六核處理器的Xavier NX模塊和帶有Volta圖形...

2021-01-27 標(biāo)簽:處理器操作系統(tǒng)System 1988 0

了解決這個(gè)復(fù)雜的問(wèn)題,設(shè)計(jì)了這個(gè)庫(kù),它可以幫助您簡(jiǎn)化設(shè)計(jì)流程。使用一些簡(jiǎn)單的 API 可以輕松地在測(cè)試臺(tái)中讀取和寫入標(biāo)準(zhǔn)位圖文件 (.BMP)。并且,使...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |