完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > vhdl

VHDL全名Very-High-Speed Integrated Circuit Hardware Description Language,誕生于1982年。1987年底,VHDL被IEEE和美國(guó)國(guó)防部確認(rèn)為標(biāo)準(zhǔn)硬件描述語(yǔ)言 。

文章:304個(gè) 瀏覽:128235次 帖子:559個(gè)

基于VHDL的EDA技術(shù)在醫(yī)學(xué)中的應(yīng)用

在世界范圍內(nèi),關(guān)于VHDL在多個(gè)領(lǐng)域尤其在芯片,系統(tǒng)設(shè)計(jì)方面的應(yīng)用研究已經(jīng)取得眾多矚目成果。而將VHDL與醫(yī)學(xué)相結(jié)合,勢(shì)必成為電子自動(dòng)化設(shè)計(jì)(EDA)一...

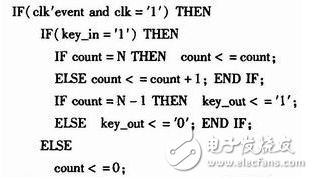

vhdl按鍵消抖程序(七種方式實(shí)現(xiàn)按鍵消抖)

按鍵消抖通常的按鍵所用開關(guān)為機(jī)械彈性開關(guān),當(dāng)機(jī)械觸點(diǎn)斷開、閉合時(shí),由于機(jī)械觸點(diǎn)的彈性作用,一個(gè)按鍵開關(guān)在閉合時(shí)不會(huì)馬上穩(wěn)定地接通,在斷開時(shí)也不會(huì)一下子斷...

基于單片機(jī)的表決式單片機(jī)多機(jī)冗余設(shè)計(jì)及VHDL語(yǔ)言編程示例

本文提出一種表決式單片機(jī)多機(jī)冗余設(shè)計(jì)方案。該方案不同于中央系統(tǒng)的多機(jī)冗余設(shè)計(jì)。大規(guī)模系統(tǒng)冗余大多采用完善而復(fù)雜的機(jī)間通訊協(xié)議實(shí)現(xiàn)系統(tǒng)重構(gòu),不太注重系統(tǒng)的...

testbench怎么寫_testbench經(jīng)典教程VHDL

testbench是一種驗(yàn)證的手段。首先,任何設(shè)計(jì)都是會(huì)有輸入輸出的。但是在軟環(huán)境中沒有激勵(lì)輸入,也不會(huì)對(duì)你設(shè)計(jì)的輸出正確性進(jìn)行評(píng)估。那么此時(shí)便有一種...

2017-12-01 標(biāo)簽:VHDL 5.6萬 0

利用VHDL硬件描述語(yǔ)言和FPGA技術(shù)完成驅(qū)動(dòng)時(shí)序電路的實(shí)現(xiàn)

CCD驅(qū)動(dòng) 電路的實(shí)現(xiàn)是CCD應(yīng)用技術(shù)的關(guān)鍵問題。以往大多是采用普通數(shù)字芯片實(shí)現(xiàn)驅(qū)動(dòng)電路,CCD外圍電路復(fù)雜,為了克服以上方法的缺點(diǎn),利用VHDL硬件描...

基于VHDL語(yǔ)言并選用FPGA設(shè)計(jì)了一個(gè)卷積碼編碼器

數(shù)字信號(hào)在有噪聲的信道中傳輸時(shí),由于受到干擾的影響,會(huì)發(fā)生誤碼。在設(shè)計(jì)數(shù)字通信系統(tǒng)時(shí),首先應(yīng)合理設(shè)計(jì)基帶信號(hào),選擇調(diào)制、解調(diào)方式,并采用均衡措施等,使誤...

2017-11-24 標(biāo)簽:fpgaFPGA設(shè)計(jì)vhdl 2247 0

使用VHDL語(yǔ)言設(shè)計(jì)的基于FPGA的實(shí)時(shí)NPR系統(tǒng)

在進(jìn)行非真實(shí)感渲染(NPR)處理時(shí)需要大量的計(jì)算,這對(duì)高幀率、高分辨率的視頻做實(shí)時(shí)的NPR渲染是一個(gè)難題。根據(jù)FPGA以并行運(yùn)算為主的特點(diǎn),對(duì)傳統(tǒng)的N...

簡(jiǎn)述BSDL邊界掃描語(yǔ)言,BSDL邊界掃描語(yǔ)言的應(yīng)用

BSDL邊界掃描語(yǔ)言的邊界掃描是一個(gè)完善的測(cè)試技術(shù)。 邊界掃描在自當(dāng)聯(lián)合測(cè)試行動(dòng)組(JTAG)90年代初發(fā)明了一種解決方案來測(cè)試使用了許多新的印刷電路,...

2017-04-19 標(biāo)簽:vhdl語(yǔ)言vhdlc++ 8740 0

基于EDA技術(shù)和VHDL語(yǔ)言的新型智能電子密碼鎖的設(shè)計(jì)與實(shí)現(xiàn)

本文介紹一種利用 EDA 技術(shù) 和 VHDL 語(yǔ)言 ,在 MAX+PLUSⅡ環(huán)境下,設(shè)計(jì)了一種新型的智能密碼鎖。它體積小、功耗低、價(jià)格便宜、安全可靠,維...

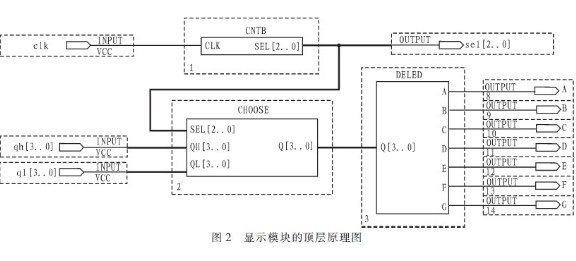

EDA技術(shù)基礎(chǔ)知識(shí)及數(shù)字系統(tǒng)設(shè)計(jì)實(shí)例

本文著重介紹EDA技術(shù)的發(fā)展、EDA技術(shù)的基本特征及使用EDA技術(shù)的數(shù)字系統(tǒng)設(shè)計(jì)實(shí)例分析

在通信系統(tǒng)中,通信芯片是整個(gè)硬件平臺(tái)的基礎(chǔ),它不僅完成OSI物理層中的數(shù)據(jù)發(fā)送和接收,還能根據(jù)傳輸方式和協(xié)議的不同實(shí)現(xiàn)不同的數(shù)據(jù)校驗(yàn)方式及數(shù)據(jù)組幀格式。

FPGA核心知識(shí)詳解(2):FPGA入門書籍推薦篇

電子發(fā)燒友網(wǎng)核心提示 :對(duì)于FPGA初學(xué)者而言,正確的入門參考書籍對(duì)其至關(guān)重要。應(yīng)廣大FPGA初學(xué)者和愛好者要求,電子發(fā)燒友網(wǎng)編輯根據(jù)多名在FPGA領(lǐng)域...

基于FPGA和VHDL的簡(jiǎn)易微機(jī)的結(jié)構(gòu)分析與應(yīng)用

隨著可編程邏輯器件的廣泛應(yīng)用,為數(shù)字系統(tǒng)的設(shè)計(jì)帶來了極大的靈活性,用戶可以利用FPGA(現(xiàn)場(chǎng)可編程門陣列)來開發(fā)出一個(gè)精簡(jiǎn)指令的CPU,同時(shí)對(duì)微型計(jì)算機(jī)...

在高速實(shí)時(shí)或者非實(shí)時(shí)信號(hào)處理系統(tǒng)當(dāng)中,使用大容量存儲(chǔ)器實(shí)現(xiàn)數(shù)據(jù)緩存是一個(gè)必不可少的環(huán)節(jié),也是系統(tǒng)實(shí)現(xiàn)中的重點(diǎn)和難點(diǎn)之一。詳細(xì)闡讀SDRAM數(shù)據(jù)文檔的前提...

專訪NI行銷經(jīng)理郭皇志:FPGA提升PXI儀器客制能力

電子發(fā)燒友網(wǎng)訊 :現(xiàn)場(chǎng)可編程門陣列(FPGA)元件將大幅提升PXI模組儀器客制化程度。為強(qiáng)化PXI模組儀器量測(cè)作業(yè)的效率與獲取資料的運(yùn)算速度,PXI儀器...

電子發(fā)燒友網(wǎng)核心提示 :目前,硬件描述語(yǔ)言(HDL)可謂是百花齊放,有VHDL、Superlog、Verilog、SystemC、Cynlib C++、...

電子發(fā)燒友網(wǎng)核心提示 :硬件描述語(yǔ)言HDL是一種用形式化方法描述數(shù)字電路和系統(tǒng)的語(yǔ)言。 利用這種語(yǔ)言,數(shù)字電路系統(tǒng)的設(shè)計(jì)可以從上層到下層(從抽象到具體)...

2012-10-15 標(biāo)簽:HDLVHDLVerilog HDL 4064 0

電子發(fā)燒友網(wǎng)核心提示 :本文將為軟件工程師揭開FPGA 的神秘面紗,主要介紹了如何為 FPGA嵌入式處理器開發(fā)軟件的一些實(shí)用技巧。 隨著產(chǎn)品設(shè)計(jì)復(fù)雜性的...

簡(jiǎn)析PLD和單片機(jī)構(gòu)成的雙向通信控制器

在傳統(tǒng)的控制系統(tǒng)中,人們常常采用單片機(jī)作為控制核心。但這種方法硬件連線復(fù)雜,可靠性差,且單片機(jī)的端口數(shù)目、內(nèi)部定時(shí)器和中斷源的個(gè)數(shù)都有限,在實(shí)際應(yīng)用中往...

Altium在Altium Designer軟件內(nèi)新增Aldec FPGA仿真技術(shù)

Altium和Aldec簽署的OEM協(xié)議中決定將Aldec的FPGA仿真功能添加到Altium Designer軟件中去。該協(xié)議的簽署使進(jìn)行FPGA(現(xiàn)...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |