完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > xilinx

Xilinx是全球領(lǐng)先的可編程邏輯完整解決方案的供應(yīng)商。Xilinx研發(fā)、制造并銷售范圍廣泛的高級集成電路、軟件設(shè)計工具以及作為預(yù)定義系統(tǒng)級功能的IP(Intellectual Property)核。

文章:1659個 瀏覽:121933次 帖子:5351個

全局時鐘資源相關(guān)xilinx器件原語的詳細(xì)解釋

目前,大型設(shè)計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發(fā)沿設(shè)計,對時鐘的周期、占空比、延時和抖動提出了更高的要求。為了滿足同步時序設(shè)計的要求,一...

從傳統(tǒng)的單片集中式基站架構(gòu)向依靠遠(yuǎn)端射頻頭的分布式基站架構(gòu)的過渡很快將變成一種趨勢。這種變遷為基于標(biāo)準(zhǔn)的連接功能協(xié)議取代基站內(nèi)部主要在基帶和射頻卡之間的...

2017-11-25 標(biāo)簽:Xilinx 387 0

賽靈思(Xilinx, Inc)宣布推出的是能夠支持3D電視(3D-TV)、超高清電視(Ultra HDTV)、(IP電視)IPTV、(數(shù)碼相機)Dig...

2017-11-25 標(biāo)簽:Xilinx 1538 0

Xilinx Spartan-3AN對游戲機加密的詳細(xì)分析與特點

動漫游戲是一個新興的行業(yè),發(fā)展?jié)摿Υ螅袌銮熬昂谩S螒蚱脚_的加密性、靈活性、通用性備受游戲平臺提供商的關(guān)注,同時要求低成本、容易采購。 科通數(shù)字技術(shù)公司...

基于賽靈思Virtex-5的音視頻監(jiān)視系統(tǒng)設(shè)計的詳細(xì)分析

本文探討在Virtex-5 FPGA中實現(xiàn)設(shè)計的一些難題,然后用一個項目作為示范來詳解充分利用其功能集的技法。設(shè)計過程包括幾個步驟,從針對應(yīng)用選擇適合的...

2017-11-24 標(biāo)簽:Xilinxvirtex5音視頻監(jiān)視系統(tǒng) 1374 0

基于xilinx公司的spartan-3e平臺中構(gòu)建一個嵌入式系統(tǒng)來實現(xiàn)安全網(wǎng)絡(luò)通信

信息安全的解決方案目前主要集中于采取單一的措施來保證信息的安全性,針對各種攻擊手段,防范措施主要集中于信息加密技術(shù)、安全交換機技術(shù)、防火墻技術(shù)、認(rèn)證技術(shù)...

基于XILINX的28nm從三重氧化物到HIGH-K詳細(xì)分析與前景

近10年來,當(dāng)集成電路進入亞微米階段,當(dāng)人們享受到摩爾定律帶來的好處時, 一朵烏云,一直籠罩在集成電路業(yè)界的上空,就是越來越嚴(yán)重的跑冒滴漏現(xiàn)象。 作為集...

Xilinx DA 攝像智能在駕駛員輔助平臺的應(yīng)用

Zynq-7000 All Programmable SoC 在單片器件中高度集成高級駕駛輔助系統(tǒng)所需的感測域、環(huán)境特性描述以及決策制定功能,與傳統(tǒng)多芯...

在 Xilinx 系列 FPGA 產(chǎn)品中,全局時鐘網(wǎng)絡(luò)是一種全局布線資源,它可以保證時鐘信號到達各個目標(biāo)邏輯單元的時延基本相同。其時鐘分配樹結(jié)構(gòu)如圖1所...

Xilinx UltraFast設(shè)計方法概述與指南

Vivado設(shè)計套件新增手把手的方法,確保可預(yù)測且可重復(fù)設(shè)計的結(jié)果。 過去40年來,IC工藝技術(shù)飛速發(fā)展,帶動電子企業(yè)推出豐富的產(chǎn)品,讓當(dāng)今的人們樂享其...

2017-11-18 標(biāo)簽:Xilinx 2338 0

教你如何為Xilinx設(shè)計創(chuàng)建創(chuàng)建自定義XBD文件

創(chuàng)建自定義賽靈思板級描述(XBD)文件不僅有助于節(jié)省時間,而且還能確保設(shè)計項目按計劃推進。為您設(shè)計的任意開發(fā)板創(chuàng)建一個XBD文件并非難事。 FPGA廠商...

2017-11-18 標(biāo)簽:Xilinx 2755 0

用于共享工具命令語言腳本的開源庫已發(fā)布在GitHub.com上。 在過去五年里,賽靈思把戰(zhàn)略重點放在設(shè)計方法和工具上,通過提供業(yè)界最先進、最全面的開發(fā)環(huán)...

Xilinx 7系列設(shè)備和NI cRIO-9068控制器創(chuàng)新詳解

Robert Bielby—Xilinx公司策略市場和業(yè)務(wù)規(guī)劃高級總監(jiān) 新的NI cRIO-9068可重配置機箱和NI PXIe-7975R NI Fl...

集成Xilinx內(nèi)核生成器IP至FPGA VI詳細(xì)步驟

LabVIEW使用IP集成節(jié)點方便的整合Xilinx內(nèi)核生成IP至FPGA VI。按照下列步驟添加Xilinx內(nèi)核生成器IP至FPGA VI。 1、在支...

本頁包含通過LabVIEW FPGA模塊可用的Xilinx CORE生成器IP的列表。LabVIEW通過Xilinx IP節(jié)點實現(xiàn)該IP。 下列IP名稱...

FPGA VI中不同的Xilinx內(nèi)核生成器IP設(shè)計實現(xiàn)與子模板說明

所屬選板:FPGA模塊VI和函數(shù) 必需:FPGA模塊。本主題的內(nèi)容可能與您所安裝的LabVIEW選板不匹配,LabVIEW選板上顯示的對象取決于操作系統(tǒng)...

xilinx Vivado HLS工作方式的優(yōu)勢與案例

不同層面的協(xié)議處理常見于各種新型通信系統(tǒng),因為任何信息交流都需要使用某種通信協(xié)議。通信協(xié)議一般包含數(shù)據(jù)包。數(shù)據(jù)包由發(fā)送方創(chuàng)建,由接收方重新組合,這些操...

基于Virtex-6 的Aurora 8B/10B,PCIe2.0,SRIO 2.0三種串行通信協(xié)議分析

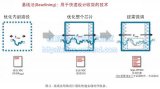

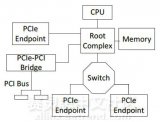

針對較為常用的Aurora 8B/10B和PCI Express 2.0,Serial RapidIO 2.0三種協(xié)議進行了測試及對比分析。首先搭建了基...

FPGA模塊里的Xilinx Vivado選項頁包括哪些項目

兩種方式可顯示該頁面: 右鍵單擊項目瀏覽器窗口中FPGA終端下的程序生成規(guī)范,從快捷菜單中選擇新建?編譯,打開編譯屬性對話框。在類別列表中選擇Xilin...

以Xilinx Zynq-7000為例說明設(shè)備樹的運用

由于內(nèi)核版本的演變,設(shè)備樹成了任何使用較高版本linux系統(tǒng)的設(shè)備平臺所必須文件,然國內(nèi)相關(guān)技術(shù)文檔嚴(yán)重不足,本文是國外技術(shù)專欄的翻譯,原文鏈接: 本教...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |