SystemVerilog通用驗(yàn)證方法(UVM)是一種生成測試和檢查結(jié)果以進(jìn)行功能驗(yàn)證的有效方法,最適合用于塊級IC或FPGA或其他“小型”系統(tǒng)。在UVM測試臺中,大多數(shù)活動(dòng)是通過編寫序列來生成的,這些序列是驗(yàn)證程序的主力要素,會(huì)導(dǎo)致諸如刺激物產(chǎn)生和結(jié)果檢查之類的事情發(fā)生。所以序列是您應(yīng)該集中精力的事情。UVM有許多運(yùn)動(dòng)部件。考慮序列時(shí),您可以專注于完成工作的程序。

產(chǎn)生序列項(xiàng)

導(dǎo)致其他順序發(fā)生

管理其他音序器上的音序

產(chǎn)生亂序交易

我們還將向您展示如何編寫自我檢查序列的代碼,并介紹在嘗試更高級的用法之前構(gòu)建和編寫基本序列的基礎(chǔ)。最后,這些技巧將幫助您更輕松地編碼和調(diào)試UVM序列。

創(chuàng)建和運(yùn)行UVM序列

如前所述,UVM序列是SystemVerilog代碼的集合,該代碼導(dǎo)致事件在測試平臺內(nèi)發(fā)生。它們通常用于創(chuàng)建事務(wù),將其隨機(jī)化,將其發(fā)送到定序器,然后再發(fā)送給驅(qū)動(dòng)程序。在驅(qū)動(dòng)程序中,生成的事務(wù)通常會(huì)引起接口引腳上的某些活動(dòng)。

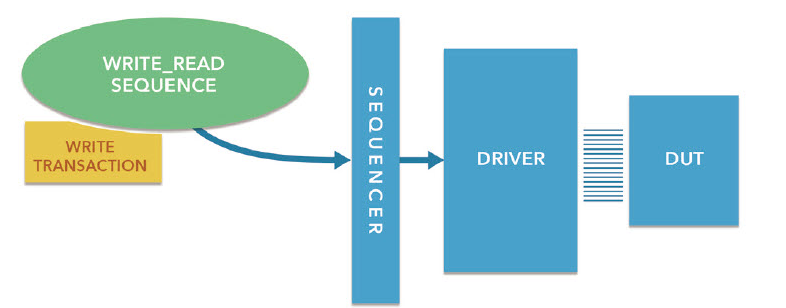

例如,如圖1所示,write_read_sequence可以生成隨機(jī)寫事務(wù)并將其發(fā)送到定序器和驅(qū)動(dòng)程序。驅(qū)動(dòng)程序?qū)⒔忉寣懭胧聞?wù)有效負(fù)載,并導(dǎo)致使用指定的地址和數(shù)據(jù)進(jìn)行寫入。

圖1這是一個(gè)執(zhí)行中的序列。

UVM序列是一個(gè)SystemVerilog對象,可以從許多不同的地方構(gòu)造它,但是通常,測試可以構(gòu)造序列然后運(yùn)行它們-它們體現(xiàn)了測試。

例如,測試可能被偽編碼為:

加載所有內(nèi)存位置

讀取所有內(nèi)存位置,然后

檢查預(yù)期的值是否匹配。

可能有一個(gè)順序?qū)⑺写鎯?chǔ)位置從A寫入到B。另一個(gè)順序是將所有存儲(chǔ)位置從A讀取到B。或更簡單的方法是:write_read_sequence首先寫入所有存儲(chǔ)位置,然后讀取所有存儲(chǔ)位置。

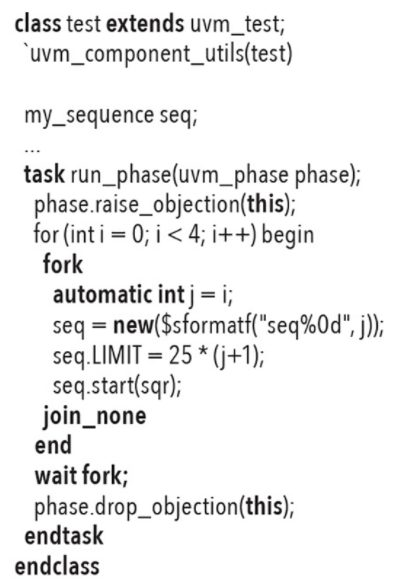

下面的測試在fork / join_none內(nèi)部創(chuàng)建一個(gè)序列。將有四個(gè)并行運(yùn)行的序列。每個(gè)序列都設(shè)置了一個(gè)LIMIT變量,并在fork / join_none的末尾開始運(yùn)行。一旦完成所有分支,測試就完成了。

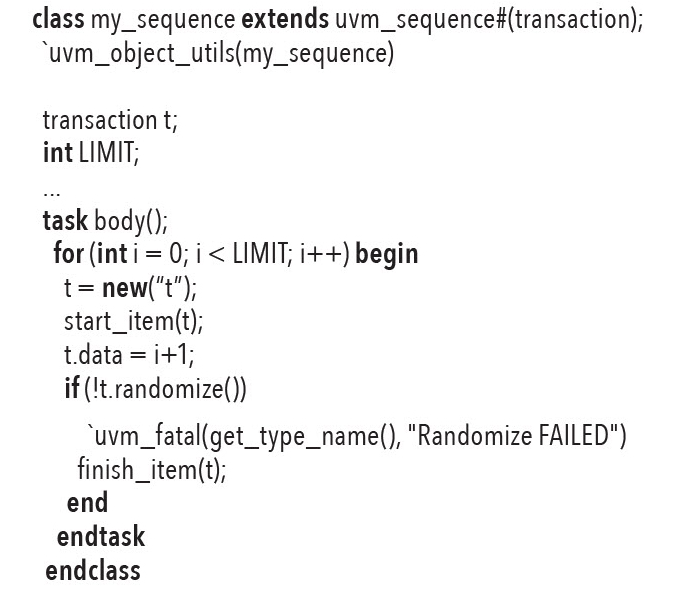

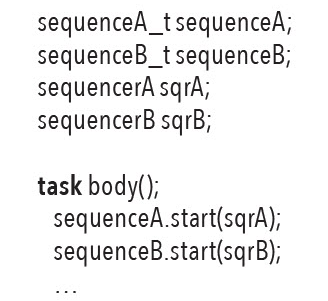

在下面的代碼my_sequence中,它是一個(gè)簡單的序列,可創(chuàng)建事務(wù)并將其發(fā)送到定序器和驅(qū)動(dòng)程序。body()任務(wù)已實(shí)現(xiàn)。這是一個(gè)簡單的for循環(huán),它會(huì)循環(huán)LIMIT次。LIMIT是可以從外部設(shè)置的序列中的變量。

在for循環(huán)中,通過調(diào)用new()或使用工廠來構(gòu)造事務(wù)對象。然后,調(diào)用start_item以開始與音序器的交互。此時(shí),定序器將停止執(zhí)行序列,直到驅(qū)動(dòng)程序準(zhǔn)備就緒為止。一旦驅(qū)動(dòng)程序準(zhǔn)備就緒,定序器將使start_item返回。一旦start_item返回,則該序列已被授予使用驅(qū)動(dòng)程序的權(quán)限。Start_item實(shí)際上應(yīng)該稱為request_to_send。現(xiàn)在,該序列具有使用驅(qū)動(dòng)程序的權(quán)限,它可以使事務(wù)隨機(jī)化,或根據(jù)需要設(shè)置數(shù)據(jù)值。這就是所謂的后期隨機(jī)化,這是理想的功能。事務(wù)應(yīng)盡可能接近執(zhí)行隨機(jī)化,這樣它們可以捕獲任何約束中的最新狀態(tài)信息。

在將事務(wù)隨機(jī)化并設(shè)置了數(shù)據(jù)值之后,將其發(fā)送到驅(qū)動(dòng)程序以使用finish_item進(jìn)行處理。Finish_item實(shí)際上應(yīng)該稱為execute_item。此時(shí),驅(qū)動(dòng)程序?qū)@取事務(wù)句柄并執(zhí)行它。一旦驅(qū)動(dòng)程序調(diào)用item_done(),然后finish_item將返回并且交易已執(zhí)行。

執(zhí)行驅(qū)動(dòng)程序

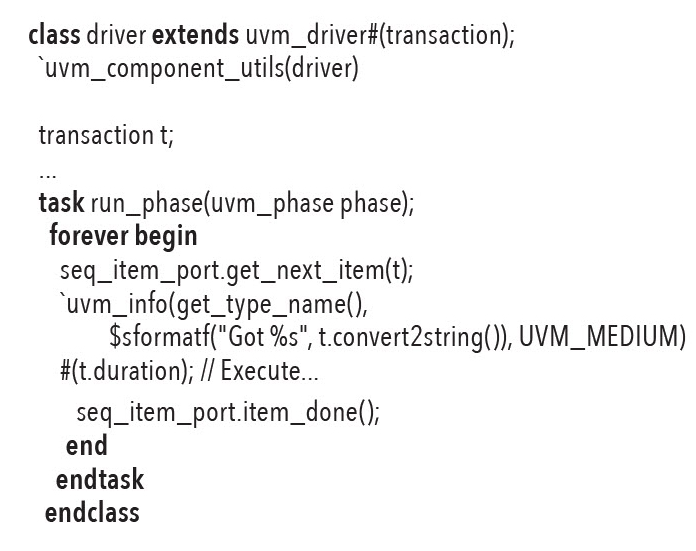

驅(qū)動(dòng)程序代碼相對簡單。它從uvm_driver派生并包含run_phase。run_phase是由UVM核心自動(dòng)啟動(dòng)的線程。run_phase被實(shí)現(xiàn)為永遠(yuǎn)的開始-結(jié)束循環(huán)。在開始到結(jié)束塊中,驅(qū)動(dòng)程序調(diào)用seq_item_port.get_next_item(t)。這是一個(gè)將導(dǎo)致在音序器中執(zhí)行的任務(wù)-本質(zhì)上是向音序器詢問應(yīng)執(zhí)行的下一個(gè)事務(wù)。可能是沒有可用的事務(wù),在這種情況下,此調(diào)用將被阻塞,即不會(huì)返回,因?yàn)樗凇暗却呈隆薄#ㄗ⒁猓嚎梢允褂闷渌亲枞{(diào)用,但它們不在本文討論范圍之內(nèi),而不是建議的用法)。當(dāng)定序器有要執(zhí)行的事務(wù)時(shí),那么get_next_item調(diào)用將取消阻塞并返回任務(wù)參數(shù)列表中的事務(wù)句柄(在下面的示例中為變量“ t”)。現(xiàn)在,驅(qū)動(dòng)程序可以執(zhí)行交易了。

對于此示例,執(zhí)行很簡單–它使用事務(wù)convert2string()調(diào)用打印一條消息,并等待由事務(wù)持續(xù)時(shí)間類成員變量控制的時(shí)間。

一旦執(zhí)行完成,將調(diào)用seq_item_port.item_done()來發(fā)信號通知定序器,并依次返回序列,表明事務(wù)已被執(zhí)行。

虛擬序列及相關(guān)序列

序列可以具有其他序列的句柄;畢竟,序列只是一個(gè)具有數(shù)據(jù)成員的類對象,以及一個(gè)將作為線程運(yùn)行的任務(wù)body()。

虛擬序列是一種序列,它可能不會(huì)生成序列項(xiàng),而是在其他音序器上啟動(dòng)序列。這是從一個(gè)控制點(diǎn)創(chuàng)建并行操作的便捷方法。虛擬序列僅具有其他序列和定序器的句柄。它啟動(dòng)它們或以其他方式管理它們。虛擬序列可能已經(jīng)通過從上方分配,使用配置數(shù)據(jù)庫查找或其他方式獲取了序列發(fā)生器句柄。它可能已經(jīng)構(gòu)造了序列對象,或者已經(jīng)通過類似的其他方式獲取了它們。

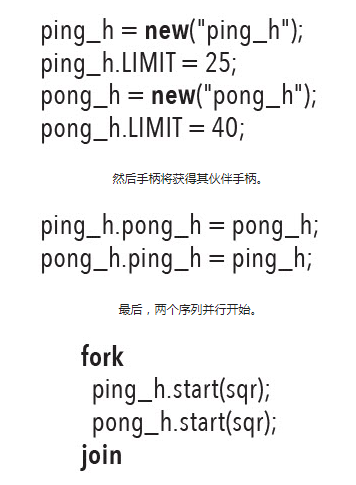

虛擬序列就像一個(gè)木偶大師,控制著其他序列。虛擬序列可能如下所示:

在下面的代碼段中,有兩個(gè)序列,即ping和pong。他們每個(gè)人都有彼此相處的地方。它們旨在輪流使用。第一個(gè)發(fā)送五個(gè)事務(wù),然后另一個(gè)發(fā)送,依此類推。有關(guān)完整代碼,請參見附錄。

首先構(gòu)造手柄,并設(shè)置運(yùn)行極限。

自檢和流量生成器序列

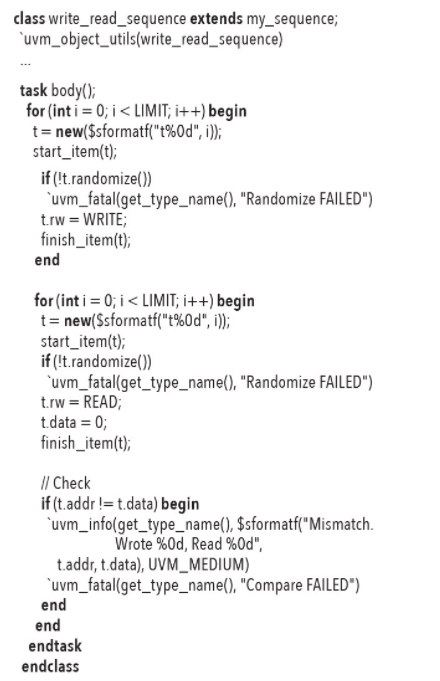

自檢序列是導(dǎo)致一些活動(dòng),然后檢查結(jié)果是否正常的序列。最簡單的自檢序列在一個(gè)地址處發(fā)出寫操作,然后從同一地址進(jìn)行讀操作。現(xiàn)在將讀取的數(shù)據(jù)與寫入的數(shù)據(jù)進(jìn)行比較。在某些方面,序列成為黃金模型。

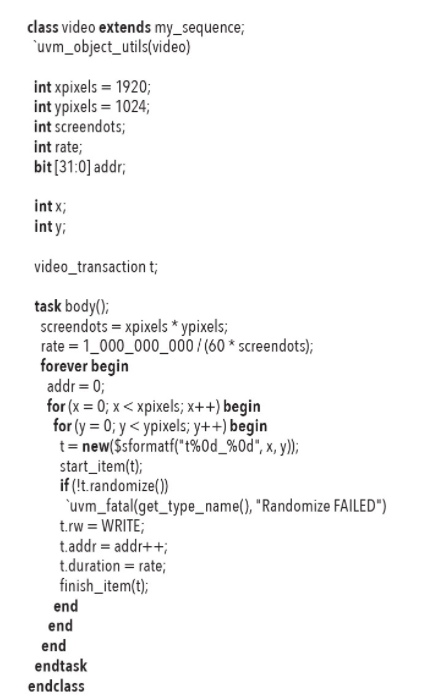

可以編寫視頻流量生成器以生成背景流量流,該流模擬或建模視頻顯示可能需要的數(shù)據(jù)量。視頻有最低帶寬要求。該計(jì)算將隨接口或總線上的負(fù)載而變化,但是對于此示例而言,簡單的計(jì)算就足夠了。視頻流量將每秒生成60次數(shù)據(jù)屏幕。每個(gè)屏幕將具有1920×1024點(diǎn)。每個(gè)點(diǎn)由一個(gè)32位字表示。使用這些數(shù)字,流量生成器必須每秒創(chuàng)建471MB。

更加完善的流量生成器將根據(jù)當(dāng)前條件調(diào)整到達(dá)率-隨著其他流量的上升或下降,應(yīng)調(diào)整視頻流量的生成率。

同步序列

序列將用于同步其他序列(所謂的虛擬序列)。通常,兩個(gè)序列之間必須有正式的關(guān)系。例如,他們不能一起進(jìn)入其關(guān)鍵區(qū)域-他們必須成為單一文件。否則,它們只能在一些常見的關(guān)鍵區(qū)域通過后才能運(yùn)行。

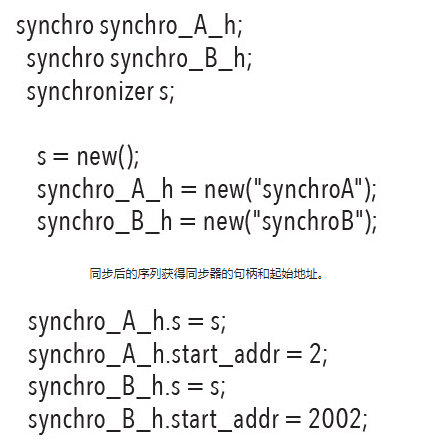

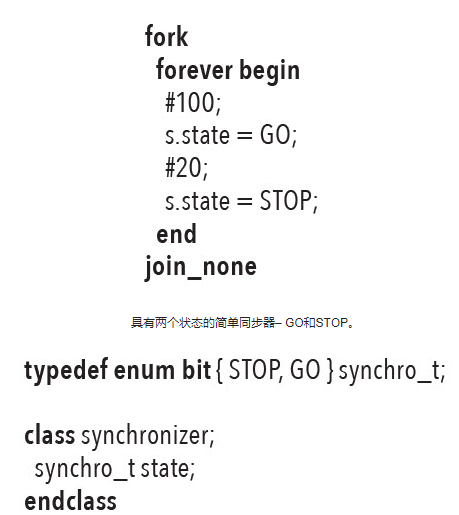

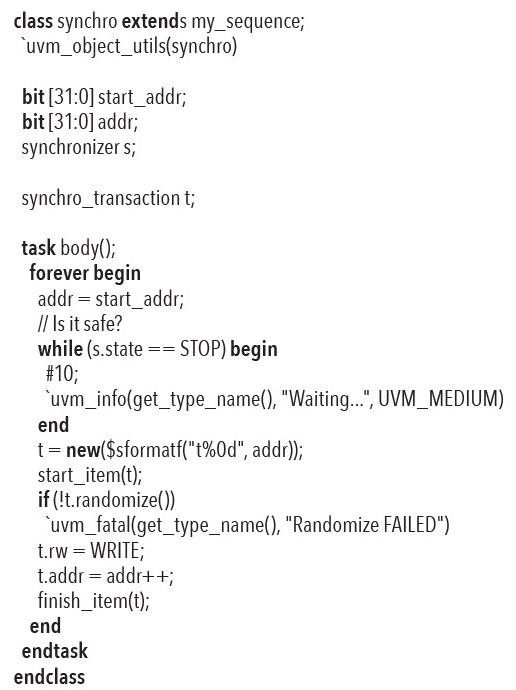

下面的代碼聲明了兩個(gè)要同步的序列(synchro_A_h和sync_B_h)。它還聲明了一個(gè)同步器。這些類沒有什么特別的-它們只是同意使用某種技術(shù)進(jìn)行同步。

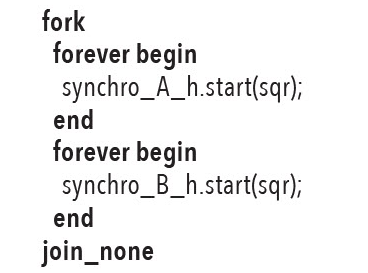

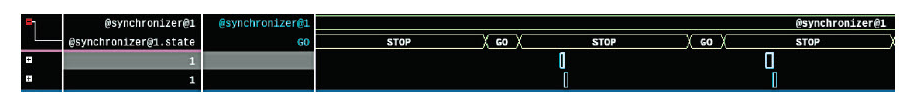

同步器控制非常簡單。它只是說GO 20滴答聲和STOP 100滴答聲。

同步的序列開始。他們運(yùn)行完成,然后只需重新啟動(dòng)即可。他們永遠(yuǎn)運(yùn)行。

使用同步器的類只有在被告知執(zhí)行后才能執(zhí)行。

在仿真中,序列等待直到同步器處于GO狀態(tài)。進(jìn)入GO狀態(tài)后,同步代碼將使用new生成事務(wù),然后調(diào)用start_item / finish_item來執(zhí)行該事務(wù)。在等待訪問驅(qū)動(dòng)程序并執(zhí)行之后,同步序列返回到循環(huán)頂部并檢查同步器狀態(tài)。它將再次運(yùn)行或停止/等待(圖2)。

圖2仿真中的同步器等待GO狀態(tài)。

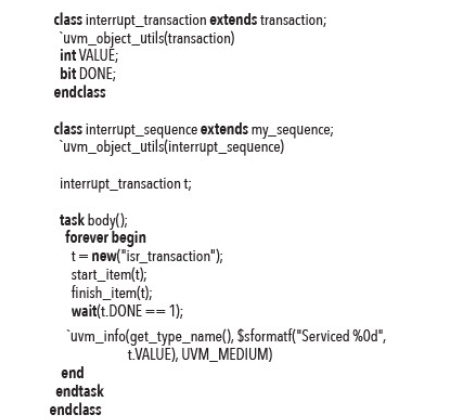

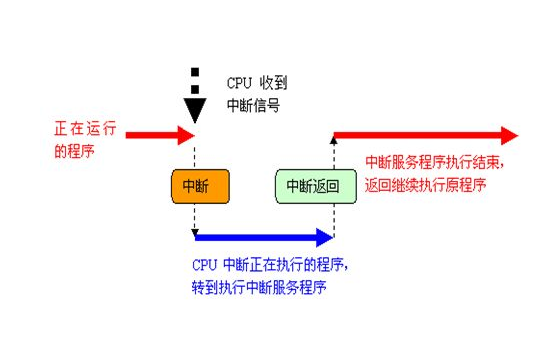

實(shí)現(xiàn)中斷服務(wù)程序

序列將用于提供中斷服務(wù)程序。中斷服務(wù)程序會(huì)一直休眠直到需要時(shí)為止。這是一種獨(dú)特的序列。在此示例實(shí)現(xiàn)中,它創(chuàng)建一個(gè)中斷服務(wù)事務(wù)并執(zhí)行start_item和finish_item。這樣,它可以將該ISR事務(wù)句柄發(fā)送給驅(qū)動(dòng)程序。然后,驅(qū)動(dòng)程序?qū)⑽兆≡摼浔钡桨l(fā)生中斷。

驅(qū)動(dòng)程序?qū)⑵渥鳛樘幚鞸ystemVerilog接口的整體工作的一部分來處理中斷。在這種情況下,處理中斷意味著將一些數(shù)據(jù)放入保留的句柄中,然后將該句柄標(biāo)記為完成。同時(shí),中斷服務(wù)序列一直在等待事務(wù)被標(biāo)記為完成。用某種說法,這被稱為真正完成的項(xiàng)目。在UVM中,還有其他機(jī)制可以處理此類問題,但它們比這種解決方案更不可靠且更復(fù)雜。

實(shí)用程序庫

序列實(shí)用程序庫將被創(chuàng)建和使用。實(shí)用程序庫是一些簡單的代碼,可用于序列編寫器,輔助函數(shù)或驗(yàn)證過程的其他抽象。

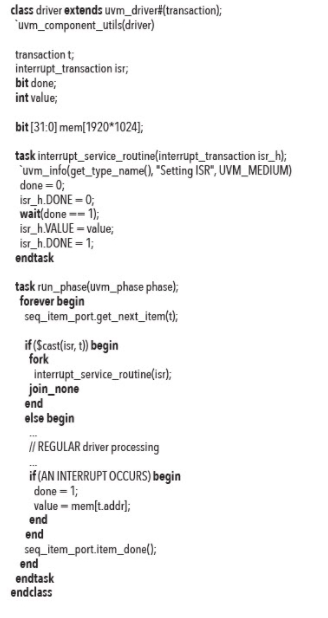

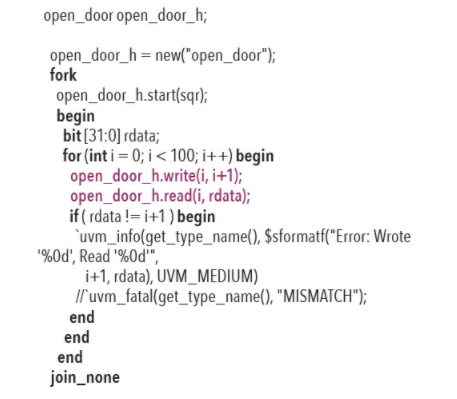

下面的open_door序列正如其名稱所暗示的那樣工作。它為音序器和驅(qū)動(dòng)器打開了大門。現(xiàn)在可以使用序列對象句柄(例如seq.read()和seq.write())隨意進(jìn)行外部調(diào)用。

打開open_door,然后使用常規(guī)方法啟動(dòng)。然后,測試程序可以像下面的紅線一樣簡單地發(fā)出讀寫操作。

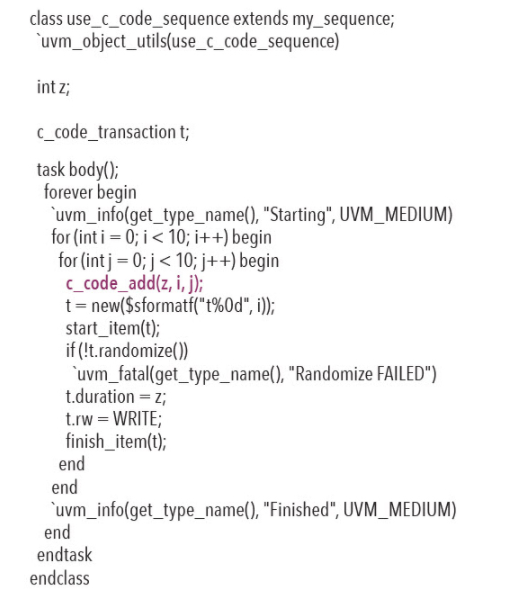

從序列中調(diào)用C代碼

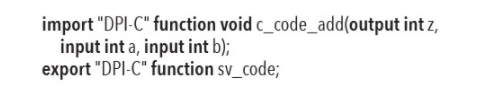

從序列調(diào)用C代碼(使用DPI-C)很容易,但是有一些限制。DPI導(dǎo)入和導(dǎo)出語句不能放置在類內(nèi)部,因此在文件,全局或包范圍內(nèi),它們必須在類之外。因此,它們沒有設(shè)計(jì)或類對象范圍。

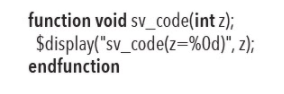

DPI-C導(dǎo)出功能或任務(wù)只是使用export命令導(dǎo)出的SystemVerilog功能或任務(wù)。

DPI-C導(dǎo)入函數(shù)或任務(wù)是具有返回值的C函數(shù)。對于任務(wù),返回值為“ int”(有關(guān)詳細(xì)信息,請參見SystemVerilog LRM)。對于函數(shù),返回值應(yīng)為返回值。

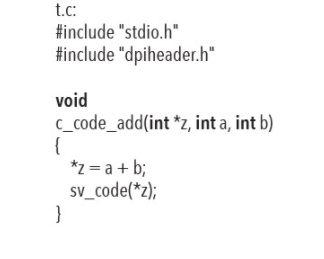

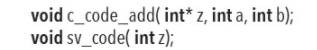

下面定義了簡單的void函數(shù)c_code_add()。它有兩個(gè)輸入,并在指針* z中返回一個(gè)值。此C函數(shù)調(diào)用導(dǎo)出的SystemVerilog函數(shù)sv_code()。

dpiheader.h是檢查DPI-C API的便捷方法。在此示例中,dpiheader.h(下圖)非常簡單。

這個(gè)序列沒有什么特別的特殊之處。它生成事務(wù),但確實(shí)調(diào)用了C函數(shù)(下面的c_code_add紅線)。就編寫調(diào)用C代碼的序列而言,實(shí)際上沒有什么特別的事情要做。DPI-C代碼必須正確編寫,并且必須在適當(dāng)?shù)姆秶鷥?nèi)聲明。

順序和交易記錄

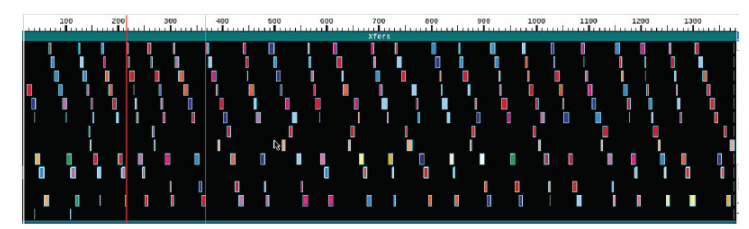

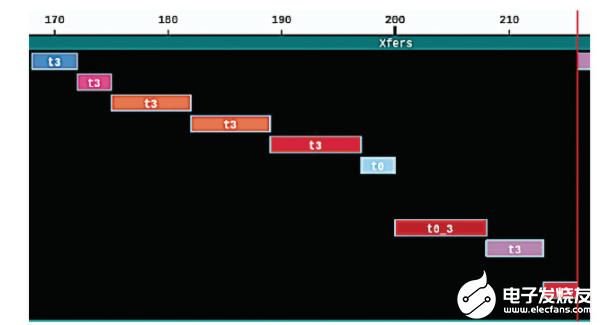

在本文討論的示例代碼中,每個(gè)序列并行運(yùn)行-在單個(gè)定序器上同時(shí)運(yùn)行。在下面的兩個(gè)屏幕截圖(圖3和圖4)中可以很容易地看到,每個(gè)序列是如何輪流發(fā)送并在驅(qū)動(dòng)程序上執(zhí)行事務(wù)的。

圖3此展開視圖顯示了每個(gè)序列如何輪流發(fā)送和執(zhí)行事務(wù)。

圖4這是事務(wù)的放大視圖。

Rich Edelman是西門子Mentor的高級驗(yàn)證方法學(xué)家。

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603001 -

UVM

+關(guān)注

關(guān)注

0文章

182瀏覽量

19167 -

序列

+關(guān)注

關(guān)注

0文章

70瀏覽量

19555 -

中斷程序

+關(guān)注

關(guān)注

0文章

34瀏覽量

8686

發(fā)布評論請先 登錄

相關(guān)推薦

《Visual C# 2008程序設(shè)計(jì)經(jīng)典案例設(shè)計(jì)與實(shí)現(xiàn)》---動(dòng)態(tài)創(chuàng)建和刪除文件夾及顯示其是否存在

請問一下在UVM中的UVMsequences是什么意思啊

DevEco Studio3.0Beta-OpenHarmony創(chuàng)建和運(yùn)行HelloWorld

創(chuàng)建和編輯VI程序、及建立和調(diào)用子VI

vxworks中斷服務(wù)程序

WindowsCE異常和中斷服務(wù)程序

如何創(chuàng)建和使用Xilinx的UltraScale PCI Express解決方案

中斷時(shí)間間隔的中斷服務(wù)程序實(shí)現(xiàn)免費(fèi)下載

Arduino板是什么如何使用IDE軟件創(chuàng)建和上傳Arduino程序到Arduino板

單片機(jī)的中斷程序如何運(yùn)行

中斷服務(wù)子程序是如何被執(zhí)行的 ?

UVM序列的創(chuàng)建和運(yùn)行及中斷服務(wù)程序?qū)崿F(xiàn)方案

UVM序列的創(chuàng)建和運(yùn)行及中斷服務(wù)程序?qū)崿F(xiàn)方案

評論