完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)技術(shù)文庫(kù)為您提供最新技術(shù)文章,最實(shí)用的電子技術(shù)文章,是您了解電子技術(shù)動(dòng)態(tài)的最佳平臺(tái)。

工欲善其事必先利其器,工程師要想設(shè)計(jì)出優(yōu)秀的電路,首先就要有功能強(qiáng)勁的電路設(shè)計(jì)軟件。本文總結(jié)了數(shù)款主流的電子電路設(shè)計(jì)軟件,為工程師的電路設(shè)計(jì)提供參考。##Protues##Multisim##Quartus II##OrCAD##EWB##Allegro##Powerpcb...

EDA技術(shù)是在電子CAD技術(shù)基礎(chǔ)上發(fā)展起來的計(jì)算機(jī)軟件系統(tǒng),是指以計(jì)算機(jī)為工作平臺(tái),融合了應(yīng)用電子技術(shù)、計(jì)算機(jī)技術(shù)、信息處理及智能化技術(shù)的最新成果,進(jìn)行電子產(chǎn)品的自動(dòng)設(shè)計(jì)。利用EDA工具,可以將電子產(chǎn)品從電路設(shè)計(jì)、性能分析到設(shè)計(jì)出IC版圖或PCB版圖的整個(gè)過程在計(jì)算機(jī)上自動(dòng)處理完成。##PLD設(shè)計(jì)工...

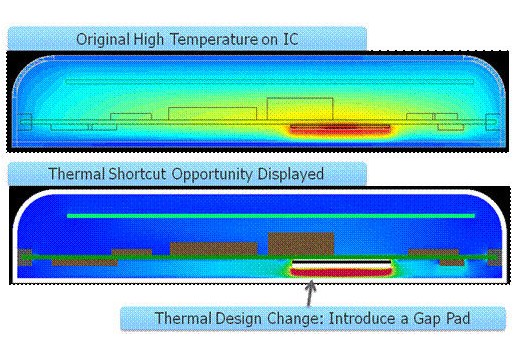

功耗過高已經(jīng)成為半導(dǎo)體制程尺寸進(jìn)一步微縮的主要障礙,并且嚴(yán)重威脅到所有電子領(lǐng)域的一切進(jìn)展,以下討論五種可用于降低未來IC功耗的技術(shù)。這些技術(shù)目前已經(jīng)在開發(fā)中,可望共同解決未來十年內(nèi)將會(huì)面臨的功耗問題。##透過縮短互連線的長(zhǎng)度并降低其電線,就能支援更小的驅(qū)動(dòng)器電晶體,從而降低IC的功耗。縮短互連線長(zhǎng)度...

通常情況下,對(duì)于微波以下頻段的電路( 包括低頻和低頻數(shù)字電路) ,在全面掌握各類設(shè)計(jì)原則前提下的仔細(xì)規(guī)劃是一次性成功設(shè)計(jì)的保證。對(duì)于微波以上頻段和高頻的PC類數(shù)字電路,則需要2~3個(gè)版本的PCB方能保證電路品質(zhì)。...

在芯片設(shè)計(jì)中,低功耗一直是一個(gè)重要的目標(biāo),受到封裝、供電、散熱的約束,并且最大功耗限制越來越嚴(yán)格。在本文中,首先討論了芯片中的功耗來源。接著,闡述了在設(shè)計(jì)過程初期可以采用的幾項(xiàng)可以降低功耗的技巧。本文提出的方法用于架構(gòu)設(shè)計(jì)和前段設(shè)計(jì)的初期,如功耗估計(jì)、低功耗架構(gòu)優(yōu)化和時(shí)鐘門控等。##功耗的估算##功...

本文介紹了EDA技術(shù)主要特點(diǎn)和功能,并對(duì)將EDA技術(shù)引入到數(shù)字電路設(shè)計(jì)工作方案進(jìn)行了探討。##EDA技術(shù)在數(shù)字系統(tǒng)中應(yīng)用以基于AlteraEPM7128SLC84-15芯片和MAX PlusII 10.0軟件平臺(tái)數(shù)字鐘設(shè)計(jì)為例,討論EDA技術(shù)在數(shù)字系統(tǒng)中具體應(yīng)用。...

富士通半導(dǎo)體(上海)有限公司今日宣布,成功開發(fā)了專為先進(jìn)的28 nm SoC器件量身打造的全新設(shè)計(jì)方法,不僅能實(shí)現(xiàn)更高的電路密度,同時(shí)也可有效縮短開發(fā)時(shí)間。...

在本文中,我們將與方法專家和實(shí)際設(shè)計(jì)人員進(jìn)行討論,當(dāng)系統(tǒng)需求變化時(shí),到底會(huì)怎樣,有沒有一種一致的方法。然后,我們將在幾種真實(shí)設(shè)計(jì)環(huán)境中應(yīng)用這種工作方法,通過它來建議應(yīng)采用怎樣的設(shè)計(jì)過程,怎樣使其更好的工作。...

在特定條件下采用更智能的技術(shù)來隔離特定錯(cuò)誤,找到問題電路的源頭并漸進(jìn)式修復(fù)錯(cuò)誤,這很重要。Synopsys 公司的Synplify Premier 和Synplify Pro FPGA設(shè)計(jì)工具以及Identify RTLDebugger 等產(chǎn)品能幫助設(shè)計(jì)人員完成上述工作。...

如何解決多樣性價(jià)值和復(fù)雜性成本之間的矛盾,已成為當(dāng)今汽車制造商面臨的最大挑戰(zhàn)之一。電氣設(shè)計(jì)領(lǐng)域?qū)Υ烁惺茏钌睿驗(yàn)椤半姎庀到y(tǒng)”幾乎受所有設(shè)計(jì)決策和客戶選擇的影響。...

目前測(cè)試工程師所面臨的最大挑戰(zhàn)之一,即是個(gè)人觀念局限于目前的技術(shù)中而停滯不前,因此,本文特別提供技術(shù)趨勢(shì)的相關(guān)知識(shí),針對(duì)測(cè)試與量測(cè)產(chǎn)業(yè),探討足以影響整個(gè)產(chǎn)業(yè)的重要技術(shù)與方法。...

EWIS 規(guī)定不僅僅針對(duì)安裝和維護(hù)。如今,設(shè)計(jì)階段也包括在內(nèi)。一個(gè)完整的 COTS 設(shè)計(jì)解決方案可提供諸多功能,如跨域關(guān)聯(lián),并且有助于盡快高效地了解 EWIS 要求,從而持續(xù)應(yīng)用在整個(gè)項(xiàng)目周期之中。...

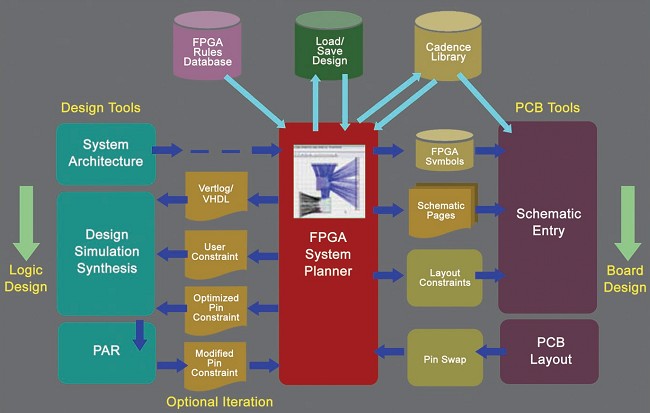

Cadence FPGA System Planner(FSP)是一款完整性高的FPGA-PCB系統(tǒng)化協(xié)同設(shè)計(jì)工具。此次主要為大家介紹FPGA System Planner的基本情況,詳見原文。...

如果PCB在娛樂產(chǎn)品中發(fā)生故障,人們的性命不受威脅;但要是在汽車中發(fā)生故障,人們的性命就岌岌可危了。因此,汽車電子部件的可靠性設(shè)計(jì)是設(shè)計(jì)過程中需要考慮的一個(gè)主要方面。...

當(dāng)電路從前工序設(shè)計(jì)人員轉(zhuǎn)移到后工序布線工程師時(shí),可以認(rèn)為時(shí)鐘概述與圖表是必須溝通的最關(guān)鍵信息。本文主要展述布線工程師如何充分“掌控”時(shí)鐘信號(hào)?...

有些資料的文字層有很多文字框,且文字框到線路PAD 間距不滿足制程能力時(shí);當(dāng)資料有大面積銅箔覆蓋,線路或PAD與銅皮的距離不在制作要求之內(nèi),且外型尺寸又較大時(shí)...可借鑒本文的處理方法...

微芯片設(shè)計(jì)有時(shí)就如同我們的生活一樣,有時(shí)很小的東西會(huì)慢慢積累而變成一件很了不起的東西。設(shè)計(jì)一個(gè)巧妙的微電路,然后將它刻在一片硅上,你的一個(gè)小小的杰作就可能會(huì)引發(fā)一...

硅電視調(diào)諧器IC正在迅速取代傳統(tǒng)的混頻振蕩器鎖相環(huán)(MOPLL)CAN調(diào)諧器技術(shù),以降低成本縮小尺寸并提高性能。硅調(diào)諧器IC在2007年以前就已開始采用,并在2010年由于平板電視和機(jī)頂盒銷...