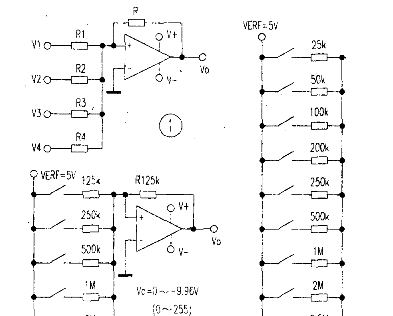

數模轉換器 (DAC) 的模擬輸出可以是電壓輸出,也可以是電流輸出�。輸出阻抗是任何輸出類型的重要參數之一�����。對于電壓模式輸出,一般會應用二進制加權電阻網絡進行數模轉換。

2023-05-11 09:41:42 480

480

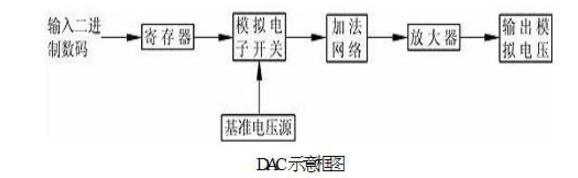

數模轉換器(DAC)將數字(用于計算機���,如微控制器)轉換為模擬電壓�。它們與模數轉換器(ADC)相反。數模轉換器(DAC)有兩種主要類型:二進制加權和R-2R

2023-07-19 15:03:31 723

723

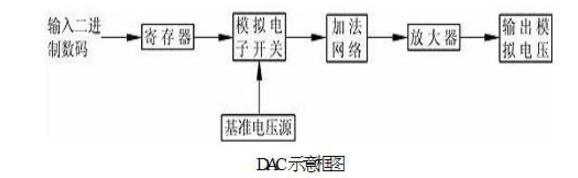

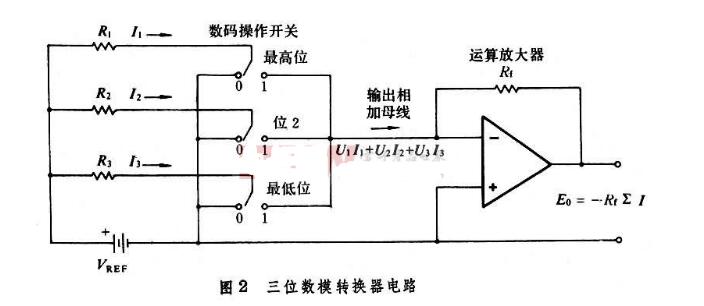

數模轉換器(DAC)是將數字量轉換成模擬量,完成這個轉換的器件叫做數模轉換器。本文將介紹數模轉換器的概念��、原理�、主要技術指標以及不同類型DAC特點進行介紹。

2016-08-16 10:17:02 16792

16792 2602型數字源表數模轉換器的測試實例講解

2021-05-11 07:03:22

概述:MAX5820是雙路、8位����、電壓輸出的數模轉換器(DAC)����,具有I2C兼容的2線接口��,工作時鐘頻率可達400kHz����。該器件采用2.7V至5.5V單電源供電(VDD=3.6V時��,電源電流115&micr...

2021-04-20 07:02:40

本帖最后由 eehome 于 2013-1-5 09:47 編輯

AD5542是ADI公司的一款單通道���、16位��、串行輸入、電壓輸出數模轉換器�����,采用5V單電源供電��。采用多功能三線式接口,并且

2011-01-26 09:26:43

數模轉換器LTC2601資料下載內容主要介紹了:LTC2601功能和特點LTC2601引腳功能LTC2601內部方框圖LTC2601典型應用電LTC2601電氣參數

2021-03-24 07:49:38

數模轉換器LTC2611資料下載內容包括:LTC2611功能和特點LTC2611引腳功能LTC2611內部方框圖LTC2611典型應用電路LTC2611電氣參數

2021-03-25 07:52:27

數模轉換器LTC2616資料下載內容主要介紹了:LTC2616功能和特點LTC2616引腳功能LTC2616內部方框圖LTC2616典型應用電路LTC2616電氣參數

2021-03-30 07:08:40

數模轉換器LTC2621資料下載內容主要介紹了:LTC2621功能和特點LTC2621引腳功能LTC2621內部方框圖LTC2621典型應用電路LTC2621電氣參數

2021-03-24 07:14:40

數模轉換器LTC2633資料下載內容包括:LTC2633特點LTC2633引腳功能LTC2633內部方框圖LTC2633典型應用電路LTC2633電氣參數

2021-04-16 07:47:28

數模轉換器MAX5558資料下載內容包括:MAX5558功能和特點MAX5558引腳功能MAX5558內部方框圖MAX5558典型應用電路

2021-03-24 06:22:09

需要用數模轉換器TLC5615的輸出做基準電壓,紋波太大�����,有一百多mV,很什么好的濾波方法�,或者有那款數模轉換器輸出紋波可以保持在20mV之內。

2015-11-05 18:31:40

數模轉換器TQ6124資料下載內容主要介紹了:TQ6124功能和特性TQ6124引腳功能TQ6124內部方框圖

2021-03-24 07:40:55

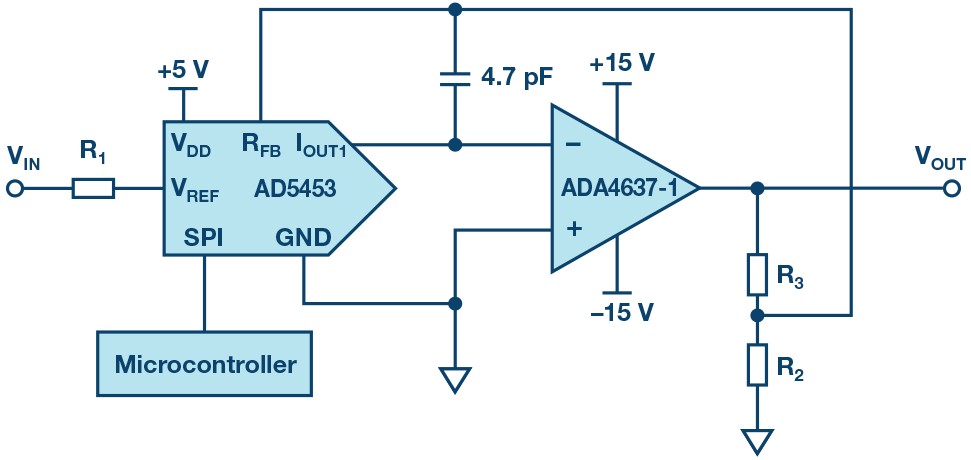

`數模轉換器ad5453接運放ad8066��,運放發燙,怎么回事����。`

2017-11-20 11:11:11

數模轉換器使用過程中的誤差有哪些��?

2020-11-05 06:32:07

數模轉換器到底是什么?[/td]

[td]

2021-09-29 06:21:11

即A/D轉換器,簡稱ADC,它是把連續的模擬信號轉變為離散的數字信號的器件�。12中文名數模轉換器簡 稱DAC模數轉換器即A/D轉換器輸出最小電壓-12V概念一種將二進制數字量形式的離散信號轉換成以標準量(或參考量)為基準的模擬量的轉換器����,簡稱 DAC

2021-07-26 06:44:38

您可能會把模數轉換器或者數模轉換器缺少輸出穩定性的原因歸咎于實際轉換器本身�。但其實轉換器周圍的電壓參考才是真正的罪魁禍首。我們將圍繞電壓參考如何改變轉換器性能作介紹��?

2021-04-07 06:33:14

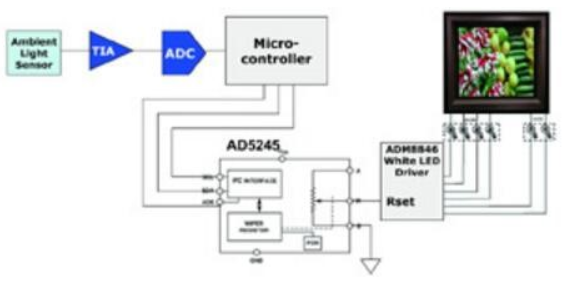

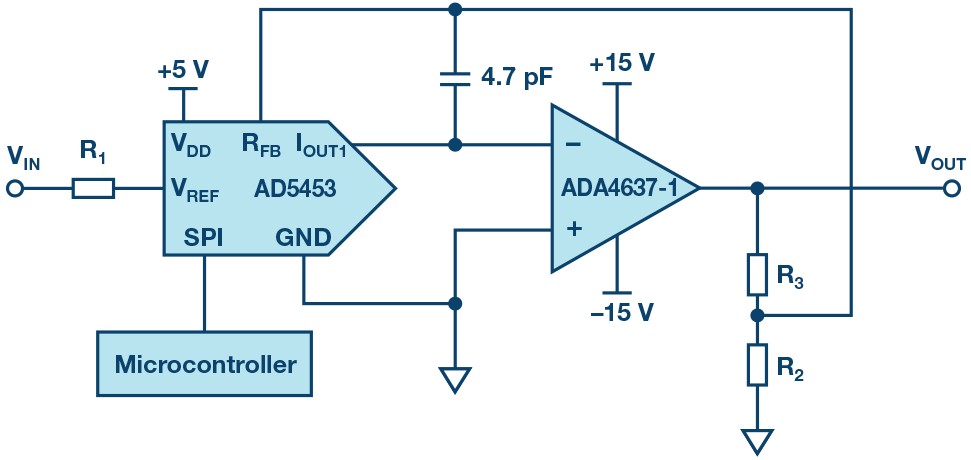

EVAL-AD5453SDZ����,用于評估AD5453電流輸出/串行輸入DAC的評估板��。 AD5453是CMOS 14位,電流輸出���,數模轉換器(DAC)。 AD5453采用2.5 V至5.5 V電源供電

2019-10-29 08:37:09

我想知道AD5541數模轉換器能夠轉換的信號帶寬是多少��,為什么芯片手冊上沒有��,我用這款芯片對10kHz的信號可以進行轉換,而換成25kHz左右的信號卻不能正常轉換���,這是怎么回事?

2023-12-20 06:00:32

AD5546是一款精密16位����,乘法����,低功耗���,電流輸出����,并行輸入數模轉換器。它采用2.7 V至5.5 V單電源供電,具有±10 V乘法參考電壓�����,可實現四象限輸出

2019-10-29 08:40:14

范圍數模轉換器(DAC)�,提供1600 MSPS采樣速率,可以產生達奈奎斯特頻率的多載波。AD9142 TxDAC+?具有針對直接變頻傳輸應用進行優化的特性�����,包括復數數字調制�、輸入信號功率檢測以及增益

2019-05-13 10:05:16

AD9162BBCAZ 數模轉換器產品介紹AD9162BBCAZ 詢價熱線AD9162BBCAZ現貨AD9162BBCAZ代理王先生*** 深圳市首質誠科技有限公司, AD9162BBCAZ是一款

2018-08-28 17:24:18

AD9164BBCZ數模轉換器產品介紹AD9164BBCZ詢價熱線AD9164BBCZ現貨AD9164BBCZ代理王先生*** 深圳市首質誠科技有限公司, AD9164BBCZAD9164是一款

2018-09-07 11:59:39

AD9172BBPZ數模轉換器產品介紹AD9172BBPZ報價AD9172BBPZ代理AD9172BBPZ咨詢熱線AD9172BBPZ現貨,王先生深圳市首質誠科技有限公司AD9172是一款高性能

2018-06-19 09:10:50

、卓越的線性度以及較低的功耗。產品型號:AD9208BBPZ-3000產品名稱:數模轉換器AD9208BBPZ-3000特征支持每線高達 16 Gbps 的線速 3 GSPS 時每通道的總功率為

2018-11-09 11:51:30

數模轉換器陀螺儀/MARKI混頻器巴倫/INTEGRA功率管/ SUMITOMO ELECTRIC功率管/MAXIM放大器/Z-COMM模塊/UMS放大器/Interpoint模塊/Kionix 加速度計/PULSAR調制器`

2018-09-03 16:27:49

輸入應用●過程控制●ATE引腳電子設備●閉環伺服控制●電機控制●數據采集系統●每針數模轉換器編程器說明DAC7624和DAC7625是12位四路電壓輸出數模轉換器,在規定的溫度范圍內保證12位的單調

2020-09-15 17:10:50

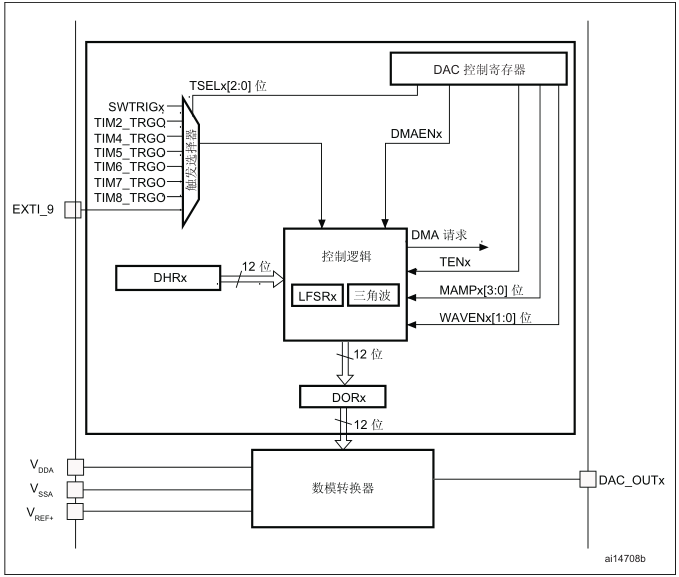

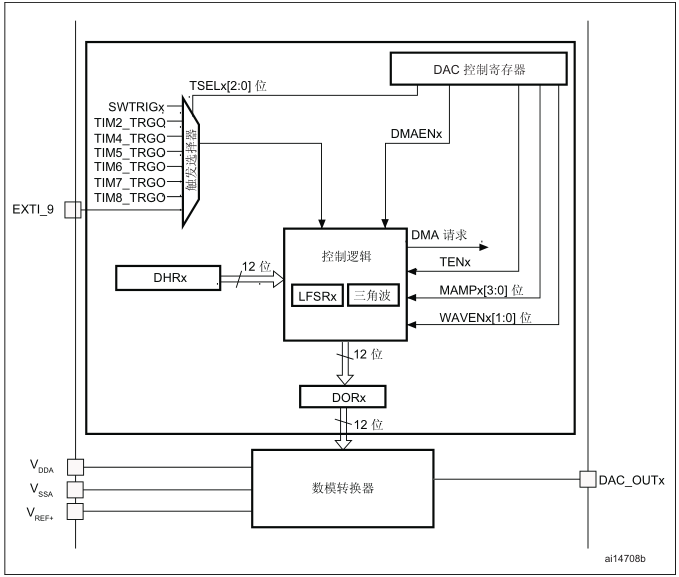

DAC:數模轉換器,即將數字量(數字123)轉化為模擬量(電壓值1v2v3v)��。STM32的DAC模塊主要特點有:① 2個DAC轉換器2個輸出通道���,每個轉換器對應1個輸出通道② 8位或者12位輸出

2022-01-11 07:01:31

DACx0501系列DAC包括哪些產品?DACx0501數模轉換器(DAC)有哪些優點�?主要應用于哪些領域����?

2021-07-08 06:54:05

第36章 STM32F429的FMC總線應用之DMA雙緩沖驅動AD7606(8通道同步采樣, 16bit, 正負10V)本章節為大家講解FMC DMA雙緩沖方式驅動數模轉換器AD7606,實戰性較強

2021-08-09 08:40:52

��,最后才給數模轉換器�����、開關電容濾波器上電,同時輸出端輸出靜態電壓 VQ。 輸出瞬態控制 MS4344 采用Pop-guard 技術來減小上電和下電時的瞬態響應��。 上電 輸出端的直流電平就由 VQ 端

2021-01-17 18:47:57

電壓輸出數模轉換器����,可以配置為8位或12位模式,也可以與DMA控制器配合使用。在12位模式下�����,數據可使用左對

2021-08-12 07:16:38

EVAL-AD5380SDZ����,用于評估具有片上基準電壓的AD5380 40通道,14位電壓輸出數模轉換器(DAC)的評估板。 EVAL-AD5380SDZ評估板旨在幫助用戶快速創建新AD5380電路

2020-05-25 09:11:08

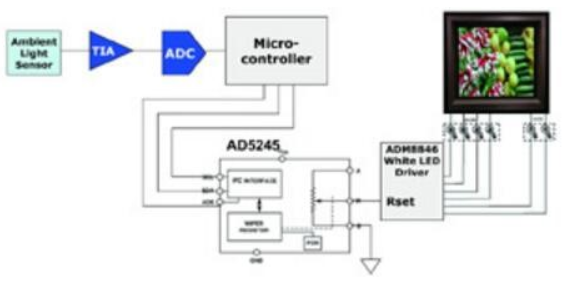

(Gavin Bakshi是本技術文章的合著者)技術文章《智能數模轉換器科普》介紹了智能數模轉換器(DAC)及其如何為諸多應用帶來價值�。智能DAC可減輕軟件開發的負擔從而提高設計效率�����,還能提供很多

2022-11-04 06:10:33

如何圍繞高速數模轉換器中的相位噪聲貢獻進行設計?怎么解決相位噪聲問題���?

2021-03-11 06:47:43

16位400M DAC的系統構架結構框圖是如何的?高速數模轉換器校準電路設計原理是什么����?方案整體測試結果和電路是什么情況��?

2021-04-06 09:21:51

如何選擇低速數模轉換器?有什么注意事項�?如何進一步了解DAC DC性能規格����?

2021-04-19 09:36:09

#來自學渣的問候這個是一個學完之后的總結DAC——數模轉換器�,將數字信號轉換成模擬信號(電壓、電流)。模擬信號:信號的頻率����、幅值、相位隨時間連續變化�。在一定時間內�����,任意取值都能得到一個瞬間的數量

2021-07-26 07:18:48

模數與數模轉換器方案

2016-06-27 18:21:43

低功耗數模轉換器AD7846的硬件設計低功耗數模轉換器AD7846的軟件設計設計數模轉換器AD7846應注意哪些問題?

2021-04-23 06:08:20

我知道一款高性能數模轉換器AD5763 ���; 想請教一下怎么用AD5763來實現雙極性電壓輸出數模轉換����?

2021-04-07 07:04:54

AD的技術專家們����,我想知道AD5541數模轉換器能夠轉換的信號帶寬是多少�����,為什么芯片手冊上沒有,我用這款芯片對10kHz的信號可以進行轉換��,而換成25kHz左右的信號卻不能正常轉換��,這是怎么回事?

2018-10-16 19:49:37

誰能告訴我一下 AD公司的數模轉換器的命名規則 這樣可以方便查閱跟選型

2018-10-09 17:58:24

原因�,電子設備制造商通常不愿意為每種輸入電壓開發不同的電源。所以�,讓我們來看看如何設計一種具有超寬輸入電壓范圍(19至265VAC和19至375VDC)的小功率(在500mW的范圍內)反激式轉換器��。 該小功率

2018-09-05 15:53:52

選擇和使用高準確度數模轉換器

2019-06-21 08:45:43

高速10位雙通道數模轉換器DAC1008D750具有哪些主要特性及應用��?

2021-04-20 06:26:32

16位方波電壓輸出數模轉換器DAC7644

2009-04-30 17:28:16 38

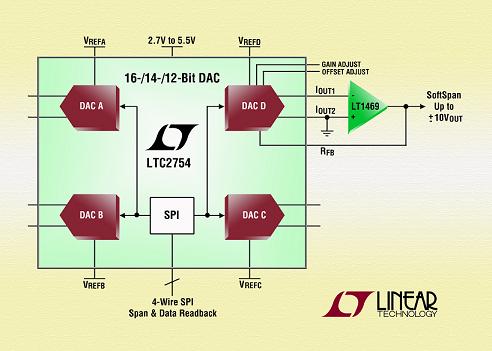

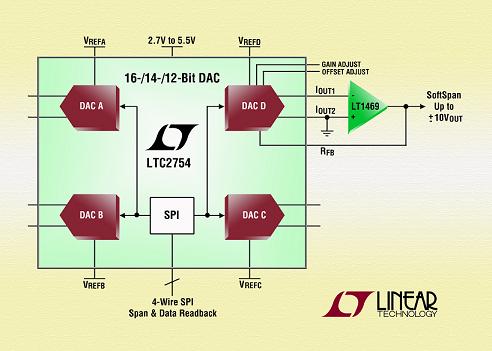

38 LTC2754-16 4通道16位電流輸出數模轉換器 (DAC)

凌力爾特公司 (Linear Technology Corporation) 推出4通道16位電流輸出數模轉換器 (DAC) LTC2754-16���,該器件實現了 ±1

2009-06-29 07:42:52 1374

1374

4通道電壓輸出16 位和12 位數模轉換器系列LTC2654(Linear)

Linear Technology Corporation推出4通道電壓輸出16位和12位數模轉換器(DAC)系列 LTC2654����,該器件具內部基準和 SPI 接口。在

2010-03-20 18:11:08 799

799 R/2R階梯數模轉換器,R/2R階梯數模轉換器原理

DAC的發展經歷了從電子管���、晶體管到集成電路的發展過程,早期的DAC采用電子管組裝而成����。進入五十

2010-03-24 13:52:49 5033

5033 (1)數模轉換器DAC的基本原理及多種數模轉換器DAC的轉換原理��。 (2)數模轉換器DAC的主要性能。 (3)模數轉換器ADC的基本原理及多種模數轉換器ADC的主要性能指標���。 (4)常用集成

2011-04-06 17:28:00 135

135 AD5541A是一款單通道、16位����、串行輸入�、無緩沖電壓輸 出數模轉換器(DAC)�,采用2.7 V至5.5 V單電源供電。 DAC輸出范圍為0V至VREF�,可保證單調性�����,16位時能提 供1 LSB INL精度,在.40C至+125C的額

2011-04-11 15:32:40 72

72 PSoC 4 電流數模轉換器

2017-10-09 15:58:31 6

6 數模轉換器

2017-10-25 08:46:19 16

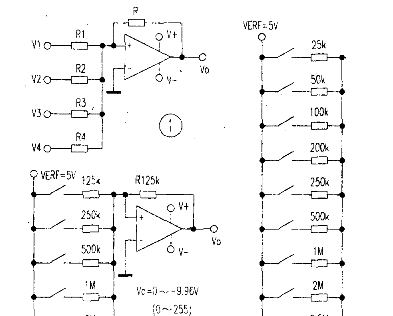

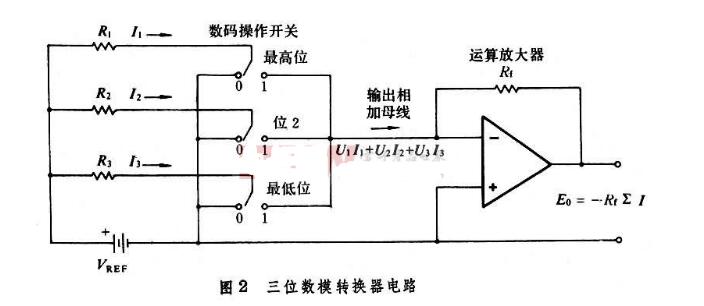

16 集成電路數模轉換器都是二進制輸入的����,而用運放構成的數模轉換器則不受數制和位數的限制。它運用了運放的反相加法器原理,如圖1所示。 當運放的增益足夠高時,其反相輸入端為虛地����,其輸出電壓v0由下式決定

2017-11-28 15:30:26 17692

17692

本文首先介紹了數模轉換器的概念與結構����,其次闡述了數模轉換器工作原理與數模轉換器的速度極限�����,最后介紹了數模轉換器兩個應用實例���。

2018-04-20 11:18:15 6189

6189

本文首先介紹了數模轉換器(DAC)原理�,其次介紹了集成電路數模轉換器的原理及作用與二進制數模轉換器電路圖���,最后介紹了理想數模轉換器 (DAC) 的重要屬性�。

2018-04-20 12:39:49 16585

16585

TLC5615是一個10位電壓輸出數模轉換器(DAC)與緩沖的參考輸入(高阻抗)。DAC的輸出電壓范圍是基準電壓的2倍,DAC是單調的�����。該裝置使用簡單��,從一個5V的電源運行���。內置電源復位功能�,以確?����?芍貜蛦訔l件。

2018-05-14 11:53:24 83

83 最受歡迎的數模轉換器架構

2018-08-16 02:00:00 3587

3587 數模轉換器(Digital-to-Analog Converter���,DAC)可將寫入數據寄存器(DAC.DATA)的數字值轉換為模擬電壓。輸出可連接至物理引腳�,也可在內部使用����。轉換范圍介于 GND 和所選內部參考電壓(VREF)之間。

2021-04-15 15:13:49 32

32 本文中,小編將對數模轉換器的誤差來源以及數模轉換器的兩大應用予以介紹,如果你想對數模轉換器的詳細情況有所認識��,或者想要增進對數模轉換器的了解程度����,不妨請看以下內容哦。

2021-04-15 17:22:43 8818

8818

UG-983:評估AD5342 12位雙通道電壓輸出數模轉換器(DAC)

2021-05-12 20:34:59 4

4 UG-964:評估AD5311R 10位����、單通道電壓輸出數模轉換器(DAC)

2021-05-13 09:30:25 3

3 UG-974:評估AD5323 12位雙通道電壓輸出數模轉換器(DAC)

2021-05-13 09:31:46 3

3 UG-981:評估AD5340 12位單通道電壓輸出數模轉換器(DAC)

2021-05-13 10:26:28 2

2 UG-986:評估AD5664R 16位四通道電壓輸出數模轉換器(DAC)

2021-05-13 11:19:24 7

7 UG-972:評估AD5321 12位、單通道電壓輸出數模轉換器(DAC)

2021-05-13 11:32:45 8

8 UG-975:評估AD5324 12位四通道電壓輸出數模轉換器(DAC)

2021-05-13 11:34:52 6

6 UG-976:AD5325 12位四通道電壓輸出數模轉換器(DAC)評估板

2021-05-13 12:18:57 2

2 UG-929:AD5327 12位四通道電壓輸出數模轉換器(DAC)評估板

2021-05-13 12:21:40 1

1 UG-965:評估AD5313R 10位雙通道電壓輸出數模轉換器(DAC)

2021-05-13 12:28:28 8

8 UG-977:AD5326 12位四通道電壓輸出數模轉換器(DAC)評估板

2021-05-13 13:07:13 3

3 UG-984:評估AD5343 12位雙通道電壓輸出數模轉換器(DAC)

2021-05-13 13:09:27 1

1 UG-980:評估AD5339 12位雙通道電壓輸出數模轉換器(DAC)

2021-05-13 13:27:25 19

19 UG-985:評估AD5344 12位四通道電壓輸出數模轉換器(DAC)

2021-05-13 13:30:14 3

3 UG-982:評估AD5341 12位����、單通道、電壓輸出、數模轉換器(DAC)

2021-05-20 10:27:44 4

4 AD5530/AD5531:串行輸入、電壓輸出12/14位數模轉換器數據表

2021-05-24 20:40:22 14

14 多通道電壓輸出數模轉換器AD5664參考代碼

2021-09-09 16:24:49 45

45 MCP48xx_雙電壓輸出數模轉換器數據手冊.pdf

2021-12-02 10:57:18 3

3 智能數模轉換器科普

2022-10-28 12:00:16 0

0 您的數模轉換器有多精確�����?

2022-11-04 09:52:15 2

2 高速數模轉換器的數字特性

2022-11-07 08:07:30 0

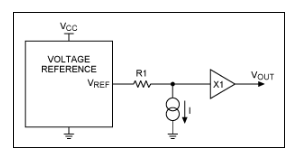

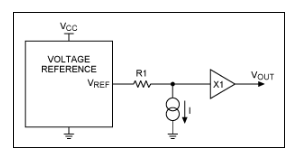

0 模數轉換器(ADC)和數模轉換器(DAC)需要穩定的基準電壓來精確測量或生成模擬信號。本應用筆記介紹了如何使用電阻�、吸電流/源極和緩沖放大器調整任何三端基準電壓源����,以動態校準基準電壓源���、微調其輸出值或生成略有不同的值�����。

2023-02-07 14:32:33 497

497

大多數數模轉換器(DAC)采用固定的正基準電壓和輸出電壓或與基準電壓和設定數字代碼的乘積成比例的電流工作。對于所謂的乘法數模轉換器(MDAC)�,情況并非如此��。這里,基準電壓可能會發生變化����,通常在±10 V范圍內���。然后���,模擬輸出可以通過基準電壓和數字代碼受到動態影響����。

2023-02-16 11:17:07 413

413

今日為大家介紹DAC數模轉換器���。

2023-03-22 10:45:26 1667

1667 STM32F4xx系列提供的DAC模塊是12 位電壓輸出數模轉換器�。DAC可以按 8 位或 12 位模式進行配置,并且可與DMA控制器配合使用���。

2023-07-22 16:43:46 1776

1776

電子發燒友網站提供《5位數模轉換器.pdf》資料免費下載

2023-09-20 14:55:05 0

0 數模轉換器的分辨率是指其能夠表示和轉換的數字信號的精度和粒度。

2023-11-28 09:20:56 380

380

電子發燒友App

電子發燒友App

評論