后PC 時代,由于網絡技術和集成電路技術的迅速發展,利用嵌入式系統進行數字信號處理與傳輸成為可能。在ARM 和DSP 構成的雙處理器系統中,嵌入式作為主設備,主要完成數據處理、存儲與網絡傳輸工作,而DSP 作為從設備需要負責復雜的算法實現。

在此高速數據采集和處理系統中,隨著采樣數據量的增大和處理任務的增加,對數據的傳送要求越來越高,如果在兩個系統端口之間沒有能夠高速傳送數據的接口,將會造成數據傳送的阻塞,嚴重影響系統的實時性與處理數據的能力,因此此系統設計的重點之一是主從設備之間的數據通信。本文介紹用雙端口RAMIDT70261 完成TMS320C6211DSP 與嵌入式ARM920T之間的數據通信。

1 IDT70261雙端口RAM功能簡介

IDT70261 是美國IDT 公司生產的高速16K×16 的雙端口SRAM,其典型功耗為750mW,它具有兩個等級的存取時間:商業級有 15/20/25/35/55 ns (max),工業級有20/25/35/55ns (max)。雙端口RAM 有兩個完全獨立的端口,它們各自有一套相應的數據總線、地址總線和控制總線,允許兩個控制器單獨或異步的讀寫其中任意一個存儲單元。兩個端口具有同樣的對雙端口RAM 的讀寫操作能力,但是當兩個端口同時對同一地址進行讀寫操作時,會因為數據的沖突而造成存儲或讀取的錯誤。對同一存儲單元的操作存在以下四種情況:

(1) 兩個端口不同時對同一地址單元進行讀寫數據。

(2) 兩個端口同時對同一地址單元進行讀出數據。

(3) 兩個端口同時對同一地址單元進行寫入數據。

(4) 兩個端口同時對一個地址單元,一個寫入數據,另一個讀出數據。

前兩種情況不會造成對雙端口RAM的讀寫錯誤,第三種情況會造成寫入數據的錯誤,第四種情況會造成讀出錯誤。為了避免對雙端口RAM 造成讀寫錯誤,IDT70261 有以下幾種仲裁控制方法。

1.1 遇忙邏輯控制

當雙端口同時對同一地址單元進行控制時,IDT70261 提供一種/BUSY 控制機制。雙端口不對同一地址單元進行控制時,兩個端口的/BUSY 引腳都為高,左右兩個端口均可正常訪問存儲空間。當兩個端口對同一地址單元進行存取時,一個端口的/BUSY 引腳為高(允許對存儲空間的讀寫操作),另一個端口的引腳為低(禁止對存儲空間的讀寫操作),哪一個請求信號在前,其端口引腳為高,另一個為低。兩個端口請求讀寫的時間差最小為5ns,當時間小于5ns 時,系統會自動允許一個引腳讀寫,屏蔽另外一個引腳,防止出現對同一地址單元的讀寫錯誤。

1.2 中斷控制機制

IDT70261 具有中斷輸出功能,中斷工作時,雙端口RAM 的兩個最高地址單元3FFE、3FFF 作為“郵箱”來傳遞相應的命令。當中斷功能不使用時,3FFE、3FFF兩個單元作為正常的存儲單元使用。下面介紹中斷工作原理。

左端口寫地址單元3FFF,/INTR 變為有效(低電平),向右端口發送中斷請求,右端口響應中斷請求后,可向3FFF 地址單元執行一次讀操作,清除中斷標志(/INTR 變為高電平)。同理,右端口寫地址單元3FFE,/INTL 變為有效(低電平),向左端口發送中斷請求,左端口響應中斷請求后,可向3FFE 地址單元執行一次讀操作,清除中斷標志(/INTL 變為高電平)。

1.3 令牌傳遞原理

IDT70261 內部有8 個獨立于雙端口RAM 的邏輯鎖存單元,用來標明共享的雙端口RAM 是否正在使用。在此工作模式下,/SEM 用作鎖存器的“片選”信號,地址線A2~A0 用來尋址8 個標志鎖存器,數據線D0用來標志鎖存器的狀態。

端口向鎖存器寫入0 表示申請控制權,寫入1 表示放棄使用權。當左端口要使用雙端口RAM 時,先寫入0 到標志鎖存器,然后讀出標志鎖存器的狀態,若讀出的值為0,則左端口獲得該存儲單元的使用權;若讀出的值為1,表明右端口正在使用該存儲單元。

此時,左端口要么循環檢測鎖存器狀態,直到右端口使用結束,要么向鎖存器寫入1,撤銷請求。同理,若右端口使用雙端口RAM 時,仍按照上述步驟進行操作[1,2]。

2 基于IDT70261的接口電路

本系統為視頻數據采集處理系統,當攝像頭采集后的數據經DSP 壓縮編碼后輸入到雙端口RAM 芯片中,ARM 處理器接收到數據請求后,接收圖像數據,對數據進行存儲和傳輸工作,最終將圖像經過解碼顯示在終端PC 機上。

基于IDT70261 的接口電路圖如圖1 所示,此系統采用中斷控制機制,雙端口RAM 的一些功能引腳并不需要全部使用。雙端口RAM 的左端是ARM920T芯片,右端是TMS320C6211 DSP 芯片。雙端口RAM兩個獨立的數據線D0L-D15L 和D0R-D15R 分別與ARM920 芯片和DSP 芯片連接,地址線A0L-A13L 和A0R-A13R 也分別與上述兩芯片連接。/CE 為芯片使能引腳,R/W 為讀寫控制引腳,/OE 為輸出使能引腳,/INT 為中斷標志引腳,/BUSY 為遇忙控制引腳,其連接電路如圖1 所示。

圖1 接口電路

3 數據通信的軟件實現

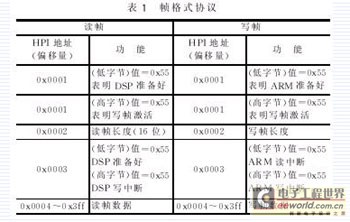

本系統采用中斷控制方式來實現對雙端口RAM的讀寫操作。DSP 主要負責圖像數據壓縮工作,壓縮后的數據傳送給雙端口RAM.傳送數據時,DSP 向信令字單元3FFF 寫入‘55H’,在ARM 方產生中斷后,ARM 讀信令字單元3FFF,如果是‘55H’,說明數據正在傳輸,讀完數據后,向信令字單元3FFE 寫入‘AAH’,代表讀完數據。DSP 接收到中斷后,讀信令字單元3FFEH,如果為‘AAH’,表示傳輸數據成功。

ARM完成整個系統的實時控制,對雙端口RAM的圖像數據進行讀取然后經過網絡傳遞給PC 機,因此需要驅動程序來實現雙端口RAM與ARM之間的數據通信。驅動程序是應用程序與硬件之間的接口,用戶可以通過驅動程序來間接的實現對硬件的讀寫控制操作。雙端口RAM 的驅動程序主要任務是讀雙端口RAM 數據到用戶空間、把用戶空間命令寫入雙端口RAM 相應地址以及相應雙端口RAM 產生的中斷。在驅動程序中,最主要的結構便是file_operation,在里面包含了對文件的打開、關閉、讀寫和其他控制函數,file_operation 結構如下:

在使用設備之前需要對設備進行初始化,包括配置ARM 接口寄存器、注冊設備、申請中斷和分配虛擬地址空間等。配置寄存器和注冊申請工作在加載模塊時實現,分配資源工作在dualram_open 函數內實現。

配置接口寄存器,AT91RM9200 具有一個EBI 接口,可以方便的連接各種存儲設備,可以使用EBI 接口中的SMC 來控制讀寫,由CS4 接口來控制雙端口RAM 的使能信號,通過向相應寄存器內寫入控制字來實現ARM 對雙端口RAM 的端口初始化工作。

在初始化函數init_dualram 中,用register_chrdev將雙端口RAM 注冊為一個字符型設備,用request_irq為設備申請相應的中斷資源,函數如下:

myirq=request_irq(AT91RM_IRQ1,dualport_inter,SA_INTERRUPT,“dualram”,NULL)

在裝載驅動時進行注冊和申請,在卸載模塊時必須進行注銷,即在dualram_exit 內執行unregister_chrdev 和free_irq 來釋放資源。

Linux 無法直接訪問某一物理地址空間,必須通過虛擬地址空間的映射機制來完成訪問。映射工作在dualram_open 函數內完成,因此每次打開設備都會完成此工作。所要用到的地址資源和數據結構定義如下:

#define dualram_base_addr 0x60000000

#define dualram_size ox3fff

u16 *remaddr

通過使用函數remaddr = ioremap (dualram_base_addr ,dualram_size);進行虛擬地址映射,此后就可以使用remaddr 來完成對實際雙端口RAM 空間的訪問了。

為了有效的提高數據傳輸效率,驅動程序與應用程序之間采用異步通知的機制,這樣上層應用程序便可以知道RAM 中的數據量是否達到閾值,而不用采用輪詢的方式,占用處理器資源。異步通知機制分三步完成,首先需要讓內核知道驅動程序與哪個進程通信,當進程使用系統函數fcntl 執行F_SETOWN 命令時,設備文件擁有者(owner)的ID 號會被記錄在flip-》f_owner 中,此時內核知道了與驅動進行通信的進程,然后應用程序調用fcntl 的F_SETFL 命令來激活異步通知機制,這樣新數據到達時輸入文件便可發送一個SIGIO 信號到flip-》f_owner 中指定的進程。

圖像數據到達后,Linux 內的應用程序完成對數據的讀寫操作,寫操作函數為:dualram_write,就是利用copy_from_user 把用戶空間的數據寫入到雙端口RAM中,讀操作函數:dualram_read,就是利用copy_to_user把雙端口RAM 中的數據讀入到用戶空間中[5,7]。

4 測試結果

視頻監控系統的測試環境是ARM 920T 與TMS320C6211 通過網絡與PC 互連構成一個簡單的局域網。通過網絡抓包軟件可以統計網絡的數據流量,通過CCS 分析工具分析系統的實時性。系統的量化階距越高,圖像的壓縮比率越大,所獲得的圖像質量越差,本系統設置的量化階距設置為75.經測試本系統的主要參數如下:圖像的壓縮格式為JPEG,分辨率為BMP(240×160),最大編碼速度為15 幀/秒,數據流量為50-200kbps,網絡采用UDP/IP 協議,網絡接口為RJ-45 100Mbps.

5 結語

本文結合了嵌入式圖像數據采集系統的設計,介紹了通過雙端口RAM 實現ARM920T 與 TMS320C6211 DSP 之間的通信。利用雙端口RAM 的強大功能可以實現各種形式的處理器之間的高速數據通信。在信號處理領域和高速數據采集中,利用雙端口RAM的幾種不同仲裁機制,可以完成不同的數據傳送要求。

用它構成的接口電路具有傳送速率高、實時性好、可靠性高、電路簡單等優點。

電子發燒友App

電子發燒友App

評論