1 引言?

Petri網是一種系統的、數學的和圖形的描述和分析工具[1],隨著超大規模集成電路FPGA和CPLD的發展,Petri網的硬件實現成為可能,而基于Petri網的邏輯控制器的邏輯電路實現方法成為最近幾年的研究熱點[2]。在目前的Petri網硬件實現的研究中,主要給出了petri網C/E系統和P/T系統的幾種實現方法,但主要存在如下缺點:1)使用基本門電路和觸發器用圖形法自底向上實現了Petri網基本元件庫所與變遷。這種設計方法的最大缺點是不易于任意修改邏輯電路設計。2)用VHDL語言實現了整體電路設計的軟件化,但未形成模塊化的Petri網元件。

VHDL語言由于其其強大的行為描述能力及與硬件行為無關的特性,被廣泛的用于數字系統設計,實現了硬件電路設計的軟件化,成為實現Petri網邏輯控制器的有力的工具。用VHDL語言進行數字電路設計的很大的優勢是其自頂向下的設計方法,可以充分的實現電路的層次化設計,從而很方便的修改頂層的控制器電路。本文分別用VHDL語言研究了幾種Petri網系統的硬件實現,包括同步PN、時延PN,尤其是高級網系統有色PN。在當前的研究中有色Petri網的硬件實現是一個難點。

2 同步Petri網的實現

2.1同步Petri網簡介

定義1 [1]同步PN是一個三元組

R是一已標識的PN

E是外界事件集

Sync是從R的變遷集到事件集的函數。

在同步PN中,每個變遷總是與一個事件相聯系,當變遷是使能的,且與變遷聯系的事件發生時,產生變遷的激發。

2.2同步Petri網的元件實現

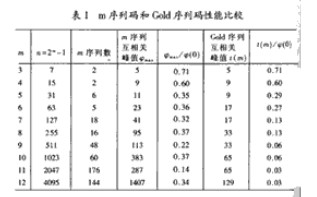

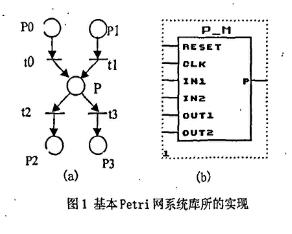

元件P_M實現了基本的同步Petri網系統(如圖1(a))中的庫所模塊,庫所P具有兩個輸入變遷和兩個輸出變遷,且每個變遷均與外部事件有關。當庫所P中沒有托肯且庫所P0或P1中有托肯時,外部事件E發生,變遷t0或t1激發,則托肯從庫所P0或P1移動到庫所P;當P中有托肯且庫所P2或P3中沒有托肯時,外部事件E發生,變遷t2或t3激發,則托肯從庫所P移動到庫所P2或P3;元件P_M(如圖1(b))是在EDA軟件Max+PlusⅡ中采用VHDL語言描述,經過編譯、仿真后形成模塊并存放與元件庫中的。它有兩個輸入變遷in1,in2和兩個輸出變遷out1,out2,當變遷激發時,其值為邏輯1,否則為邏輯0;reset為復位信號,用來設置庫所的初始狀態。clk為全局時鐘。P的值表示庫所中是否含有托肯,若含有托肯,取值為邏輯1,否則為邏輯0。

變遷元件T_M(如圖1(d)),具有兩個輸入庫所P0和P1,兩個輸出庫所P2和P3,且受外部事件x的控制,如圖1(c)所示,其激發規則是當庫所P0和P1中有托肯,而庫所P2和P3中沒有托肯,且事件x發生時,變遷激發。變遷元件T_M 輸入端in1,in2,out1,out2分別表示輸入庫所和輸出庫所中含有托肯的狀態,若含有托肯,則取值為邏輯1,否則為邏輯0,x是外部事件。T表示變遷的激發狀態,若可激發則取值為邏輯1。

用VHDL語言描述部分源程序如下:

architecture beh of t_m is

signal t0: std_logic;

begin??t<=x and in1 and in2 and (not out1) and (not out2);??end beh;

庫所元件P_M和變遷元件T_M均存放在Max+PlusⅡ中建立的元件庫中,是可以調用使用的。

3??時延Petri網的實現

3.1時延Petri網的定義

????

時延PN被用來描述其運行與時間有關的系統。主要有兩種:P時延PN和T時延PN。因二者是等效的,其中一個模型可以轉換成另一個模型,故在此主要實現了T時延PN。

定義2[1]??T時延PN是二元組

Tempo是從變遷集T到非負有理數集的函數,Tempo(Tj)=dj是與變遷Tj相聯系的時限,它規定了Petri網中的每一個變遷的持續時間。

在T時延PN中,每個變遷均有一為零或任一正實數的持續時間。而庫所中沒有持續時間,只要和它相連的變遷激發,庫所就可失去或獲得托肯。當變遷的輸入庫所中含有托肯時,變遷是使能的,但要真正激發需要經過一段持續時間。

3.2變遷時化Petri網元件的實現

T時延PN中庫所元件與同步Petri網一致。

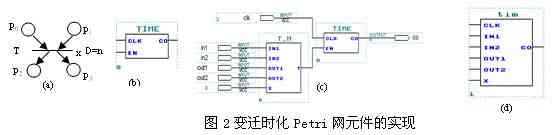

T時延PN中變遷元件的實現是在基本Petri網中變遷元件的基礎上設計了一個計時器TIME,如圖2(b),clk為計時頻率,決定了計時的精度;en為其使能端,當變遷可激發時,en為1,計時器開始計時,計時結束時co輸出為1。

在圖2(a)中變遷T與時延D=n相連,當庫所P0和P1中各有一個托肯時,變遷T獲得發生權,但到T發生,需有n個單位的延時.調用元件T_M和計時元件TIME,建立邏輯電路如圖2(c)示,并經過編譯形成圖2(d)所示邏輯模塊時化變遷元件tim。

用VHDL語言實現計時器模塊源程序如下:

if clkevent and clk=1 then

if en=1 then

???if q=n then q<=0;co<=1;???else q<=q+1; co<=0;??end if;

else q<=0; co<=0;??end if;??end if;??

3.3變遷時化Petri網元件實現的應用舉例

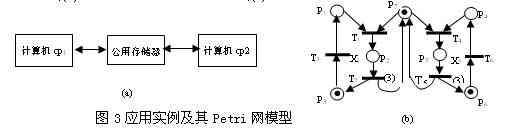

兩臺計算機使用一個公共存儲器,如圖3(a),假設每臺計算機可以有三種狀態:(a)不需要該存儲器;(b)需要存儲器但還沒有使用它;(c)正在使用存儲器。

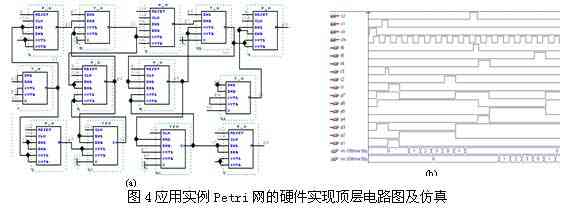

則對其建立Petri網模型如圖3(b)示。各庫所和變遷的含義解釋為:P1,P4分別表示CP1、CP2發出需要該存儲器請求;P2、P5分別表示CP1、CP2占用該存儲器;P3,P6分別表示CP1、CP2不需要該存儲器;P7表示存儲器;變遷中與時間相關的是T2、T5,分別表示cp占用存儲器的時間。這是一個時延Petri網系統。分別調用元件庫中所形成的庫所元件、變遷元件和時延變遷元件,作出該系統的邏輯電路圖如圖4(a),并在EDA軟件Max+PlusⅡ中對其編譯、仿真下載,仿真波形如圖4(b)示。

4??變遷時化有色Petri網CTPN的實現

4.1 CTPN網簡介

CTPN={P, T, F, C, S, G}為變遷時間化的有色Petri網,其中,

P 是一個有限的庫所集合。庫所包含有色托肯。

T 是一個有限的變遷集合。每個變遷均有一正實數的持續時間。一個激發顏色集與變遷相聯系,其中每種顏色表明了一種激發的可能性。

F 是與變遷相聯系的函數,表明了變遷激發后其輸入弧和輸出弧上信息的轉換關系,若F為恒等函數,則省略不標。

C 是與庫所相連的顏色的集合,C={C1,C2…Ci}。

4.2 CTPN網的元件實現

PROCESS進程是VHDL語言中最有特色的部分。在一個VHDL語言設計中,一個結構體中可以包括多個進程,而進程之間是并發的關系,同時又可以通過信號實現進程之間的聯系。在有色Petri網的實現過程中,主要利用了vhdl語言中的進程語句process,根據庫所中的顏色設置所需的進程,并將每一種顏色作為每一個相對應進程的敏感信號,而敏感信號的任何變化都可以啟動進程的運行,當敏感信號不發生變化時,進程是掛起的,從而實現了有色Petri網中庫所對不同顏色的識別。

如圖5(a)所示為一個簡單的變遷時化有色petri網模型,具有顏色集{b,y},如果P1中有標記b(或y),則變遷T1對于顏色b(或y)是使能的,T1的激發包括從庫所P1中移去一個標記b(或y),在P2中增加一個標記b(或y)。該模型的庫所和變遷元件的實現如圖5(b)、(c),其部分源程序為:

architecture beh of p_c is

begin

process(clk,reset,inb,outb)

…

end process;

process(clk,reset,iny,outy)

…

end process;??…????end beh;

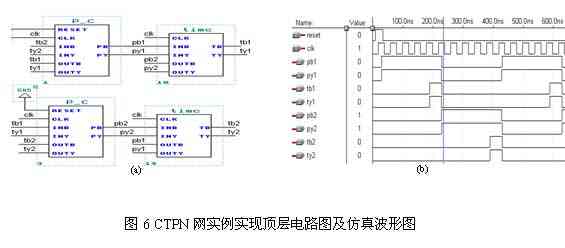

變遷元件T_C的實現是將同步PN網中的變遷根據激發顏色進行細化。將變遷元件T_C和計時器相連即可實現時化的有色變遷,在Max+PlusⅡ中形成可調用的時化變遷元件timc。

對圖5(a)模型的硬件實現通過調用庫所元件P_C和變遷元件T_C、timc實現,其實現的頂層元件圖如圖6(a)所示。并在Max+PlusⅡ中對其作仿真,波形圖如圖6(b)。

5 本文作者創新點

本文給出了幾種Petri網系統的硬件實現方案,采用VHDL語言分模塊實現,描述元件的功能并將元件存入WORK庫中,使設計具有很強的可讀性、可重復性、及可修改性,大大提高了系統的開發效率。

參考文獻

[1] R. 大衛、H. 奧蘭 著,黃建文、趙不賄譯。佩特利網和邏輯控制

器圖形表示工具[M],北京:機械工業出版社,1996

[2]趙不賄,景亮,嚴仰光。Petri網的硬件實現[J],軟件學報,2002(10):1652-1658

[3] Naehyuck Chang, Wook Hyun Kwon, Jaehyun Park. FPGA-based Implementation of Synchronous Petre Nets, Industrial Elecronics, Contorl and Instrumenation,1996,Proceed.

[4] 祝習兵,胡健生,黃金志。基于CPLD的基本Petri網系統的硬件實現[J],現代電子技術,2004(3):102-105

[5] 趙不賄,嚴仰光,陸繼遠,唐平. 控制電路基于Petri網的圖形化設計與仿真研究[J],電路與系統學報,2005(5):54-58

[6] 沈憲明,白瑞林,章智慧. 基于FPGA的模糊CMAC網絡的硬件實現

[J]. 微計算機信息, 2006, 2-2: 基于FPGA的模糊CMAC網絡的硬件實現

電子發燒友App

電子發燒友App

評論