Gigabit以太網(wǎng)絡(luò)收發(fā)器引爆連接端口成長風(fēng)潮

以太網(wǎng)絡(luò)已成為全球應(yīng)用最廣泛的企業(yè)通訊標(biāo)準(zhǔn),隨著多數(shù)企業(yè)開始將傳統(tǒng)信息系統(tǒng)轉(zhuǎn)移到網(wǎng)絡(luò)上,企業(yè)網(wǎng)絡(luò)的頻寬使用量每年都出現(xiàn)大幅成長;除此之外,桌上型會議、網(wǎng)絡(luò)虛擬會議、和群組導(dǎo)向的生產(chǎn)力應(yīng)用等新技術(shù)也讓今日的網(wǎng)絡(luò)永遠(yuǎn)處于尖峰使用狀態(tài)。

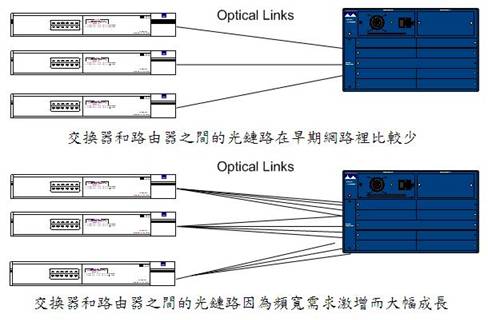

隨著頻寬需求飛快增加,交換路由器 (switch router) 設(shè)備制造商也開始發(fā)展能夠延展擴(kuò)充的系統(tǒng),以便滿足市場對于傳輸頻寬的無止境要求。這個結(jié)果就反映在交換路由器的連接埠數(shù)目上,典型交換路由器的埠數(shù)在短時間內(nèi)就從每套系統(tǒng)8個連接端口激增為72個連接埠。

交換路由器設(shè)計人員現(xiàn)正面臨增加連接端口密度、降低成本、減少功耗、以及縮小系統(tǒng)體積等重要考驗。多端口千兆位以太網(wǎng)絡(luò) (Multi-port Gigabit Ethernet) 收發(fā)器便是針對這些問題而推出的一項重要進(jìn)展,本文將深入探討這類收發(fā)器在以太網(wǎng)絡(luò)交換路由器設(shè)計中所扮演的重要角色。

?

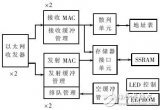

圖1:Gigabit以太網(wǎng)絡(luò)訊號鏈

Gigabit以太網(wǎng)絡(luò)可分為兩大類,第一類收發(fā)器統(tǒng)稱為1000BaseT收發(fā)器 (與IEEE802.3ab兼容的Gigabit以太網(wǎng)絡(luò)銅線實體層組件),第二類收發(fā)器則是用來驅(qū)動SFP (Small Form Factor Pluggable) 以及GBIC (Gigabit Interface Converter) 等光模塊的電路收發(fā)器組件,這些收發(fā)器通常稱為Gigabit以太網(wǎng)絡(luò)收發(fā)器,或Serdes (符合IEEE803.z標(biāo)準(zhǔn))。本文將針對第二類收發(fā)器,及其對于現(xiàn)有系統(tǒng)設(shè)計的成本、功耗、和體積產(chǎn)生的重大影響做討論。

設(shè)計人員必須了解,隨著企業(yè)網(wǎng)絡(luò)的10/100/1000BaseT連接埠數(shù)目不斷加,Gigabit以太網(wǎng)絡(luò)上行端口 (uplink port) 將成為路由器的主要技術(shù)瓶頸。交換路由器不僅需要更多個Gigabit以太網(wǎng)絡(luò)上行端口,網(wǎng)絡(luò)集線箱與數(shù)據(jù)中心也需要更大型的Gigabit以太網(wǎng)絡(luò)交換器。

?

圖2:光網(wǎng)連接埠的演進(jìn)

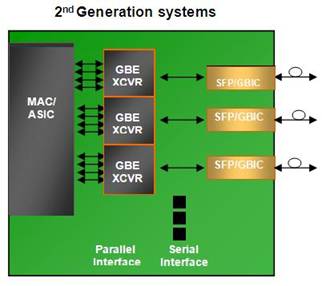

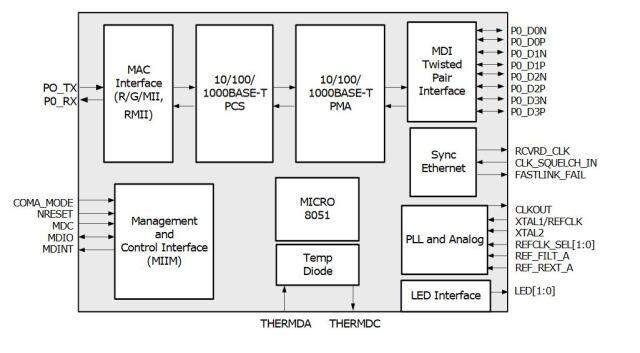

過去十年里,專門驅(qū)動光學(xué)上行端口的Gigabit以太網(wǎng)絡(luò)收發(fā)器已從單端口組件演變成復(fù)雜的多端口系統(tǒng)單芯片。圖3為Gigabit以太網(wǎng)絡(luò)收發(fā)器在過去十年的演進(jìn)過程。

?

?

?

圖3:系統(tǒng)演進(jìn)

圖4可做為參考,它是Gigabit以太網(wǎng)絡(luò)光纖連接端口的成長情形以及未來的成長預(yù)測。

?

?

圖4:Gigabit以太網(wǎng)絡(luò)光學(xué)連接端口數(shù)目的預(yù)測

從圖4的圖表看出,由于10/100/1000BaseT埠數(shù)不斷增加,Gigabit以太網(wǎng)絡(luò)交換路由器設(shè)計人員必須繼續(xù)發(fā)展新技術(shù)來增加Gigabit以太網(wǎng)絡(luò)的上行端口數(shù)目。

隨著產(chǎn)品設(shè)計世代交替,交換路由器設(shè)計人員已開始處理或解決功耗、成本、和電路板面積等重要問題;這些問題會回過頭來影響產(chǎn)品價格、擴(kuò)充性、使用性、和服務(wù)能力等重要客戶要求。

?

圖5:重要的設(shè)計問題與要求

本文接下來的重點將放在如何選擇Gigabit以太網(wǎng)絡(luò)收發(fā)器以實現(xiàn)系統(tǒng)目標(biāo),并同時解決所有Gigabit以太網(wǎng)絡(luò)交換路由器設(shè)計人員所面臨的重要挑戰(zhàn)。

選擇正確的收發(fā)器

為應(yīng)用選擇Gigabit以太網(wǎng)絡(luò)收發(fā)器時,由于發(fā)展多連接端口產(chǎn)品可能遇到龐大電源需求、功耗、以及有限的電路板面積等問題,因此交換路由器研發(fā)人員必須考慮許多因素。選擇Gigabit以太網(wǎng)絡(luò)收發(fā)器時,設(shè)計人員必須考慮界面 (并列和串行)、功耗、封裝、和成本等四個關(guān)鍵領(lǐng)域。本文將針對此四領(lǐng)域逐一討論。

一.界面

1.1 并列界面

Gigabit以太網(wǎng)絡(luò)收發(fā)器有許多需要設(shè)計人員深入考慮和選擇的界面,包括并列數(shù)據(jù)界面、高速串行界面、和控制界面。Gigabit以太網(wǎng)絡(luò)收發(fā)器的并列界面近來發(fā)展相當(dāng)快速。過去許多年里,由于10位并列界面的設(shè)計和實作都很簡單,因此成為Gigabit以太網(wǎng)絡(luò)收發(fā)器的主要界面。10位界面 (Ten-Bit Interface,TBI) 是從Gigabit Media Independent Interface (GMII) 演變而來,而GMII則是由負(fù)責(zé)管理以太網(wǎng)絡(luò)規(guī)格的標(biāo)準(zhǔn)機(jī)構(gòu)所制定。

TBI/GMII界面采用LVTTL訊號位準(zhǔn),數(shù)據(jù)則由參考頻率的上升邊緣所控制。GMII界面與TBI界面的主要區(qū)別在于,GMII界面包含Physical Coding Sub-layer (PCS) 功能,而支持TBI界面的組件通常不會提供這些功能。選擇TBI或GMII界面的關(guān)鍵在于所使用的媒體存取控制器 (MAC),以及這些媒體存取控制器是否內(nèi)建所需的PCS功能,或者需要由收發(fā)器提供這些功能。

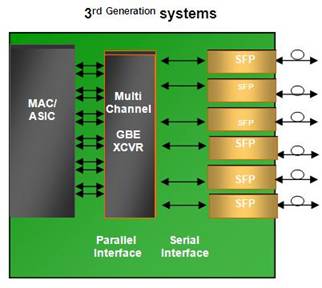

這些年來,TBI/GMII界面已逐漸被精簡位界面 (reduced bit interface) 取代,這些界面會減少接腳總數(shù)和芯片面積,并同時提高連接端口密度。這項改變的主因在于設(shè)計人員需增加系統(tǒng)的連接端口數(shù)目,同時將相關(guān)的ASIC和MAC組件成本降至最低。Reduced Ten Bit Interface (RTBI) 以及 Reduced Gigabit Media Independent Interface (RGMII) 是目前應(yīng)用最廣泛的精簡位界面。RTBI是傳統(tǒng)10位界面的精簡版本,它將原始并列位的寬度從8/10位減少至4/5位 (根據(jù)芯片是否執(zhí)行8b/10b編碼/譯碼來決定為8/10或4/5位);訊號位準(zhǔn)則從LVTTL和SSTL2改變?yōu)镠STL。這些4/5位會以參考頻率的上升和下降邊緣做為控制,也就是說精簡位界面只需要一半接腳,就能達(dá)到與傳統(tǒng)10位界面相同的實際數(shù)據(jù)速率。接腳數(shù)目減半對于擁有24或48個Gigabit以太網(wǎng)絡(luò)連接端口的系統(tǒng)有極大好處。 ?

?

圖6:精簡位界面

RGMII主要用來擔(dān)任TBI/GMII和RTBI的替代選項。它會在參考頻率的上升和下降邊緣利用四個控制訊號將數(shù)據(jù)多任務(wù)化,使I/O接腳的最大數(shù)目從23只 (TBI界面的并列端) 減少到12只 (包括控制接腳)。

設(shè)計人員為其應(yīng)用選擇界面時,必須仔細(xì)規(guī)劃和了解訊號鏈;在做Gigabit以太網(wǎng)絡(luò)收發(fā)器界面的MAC/ASIC設(shè)計時,更須如此。若設(shè)計人員的目標(biāo)是盡可能增加Gigabit以太網(wǎng)絡(luò)的連接端口數(shù)目,并維持系統(tǒng)體積不變,就應(yīng)考慮采用某種精簡位界面 (RTBI/RGMII)。

圖7:精簡位界面的接腳說明

訊號名稱?RTBI?RGMII?說明

TXC?MAC?MAC?隨著速度不同,傳送參考頻率為125 MHz、25 MHz、或是2.5 MHz ± 50 ppm

TD[3:0]?PCS?MAC?在RTBI模式下,它在TXC上升邊緣時包含位3:0,下降邊緣時包含位8:5。在RGMII模式下,它在TXC上升邊緣時包含位3:0,下降邊緣時包含位7:4

TX_CTL?PHY?PHY?在RTBI模式下,它在TXC上升邊緣時包含位5,下降邊緣時包含位10。在RGMII模式下,它在TXC上升邊緣時包含TXEN,下降邊緣時包含TXEN和TXERR的邏輯微分值 (logical derivative)

RXC?PHY?PHY?連續(xù)性接收參考頻率為125 MHz、25 MHz或2.5 MHz ± 50 ppm,并從其接收的數(shù)據(jù)串流產(chǎn)生

RD[3:0]?PHY?PHY?在RTBI模式下,它在RXC上升邊緣時包含位3:0,下降邊緣時包含位8:5。在RGMII模式下,它在RXC上升邊緣時包含位3:0,下降邊緣時包含位7:4

RX_CTL?PHY?PHY?在RTBI模式下,它在RXC上升邊緣時包含位5,下降邊緣時包含位10。在RGMII模式下,它在RXC上升邊緣時包含RXDV,下降邊緣時包含RXDV和RXERR的微分值

1.2 串行界面

Gigabit以太網(wǎng)絡(luò)收發(fā)器目前所提供的高速串行界面可分為LVPECL (Low Voltage Pseudo Emitter Coupled Logic)、CML (Current Mode Logic) 以及VML (Voltage Mode Logic) 等三種訊號位準(zhǔn) (邏輯位準(zhǔn)的比較請參考圖8)。串行界面的選擇過去是由收發(fā)器所連接的光模塊種類來決定;現(xiàn)今設(shè)計則使用交流耦合的SFP光模塊,這項考慮已不如I/O電力供應(yīng)能力或終端匹配等因素來得重要。舉例來說,德州儀器 (TI) 的新型收發(fā)器就采用內(nèi)建終端匹配功能的VML技術(shù)。VML驅(qū)動器只要采用交流耦合方式,就能與LVPECL訊號完全兼容。

VML驅(qū)動組件采用CMOS制程技術(shù),其優(yōu)點在于不需要外接提升電阻,因為它們所采用的NMOS 和PMOS晶體管架構(gòu)可同時驅(qū)動下降/上升訊號邊緣。

不同邏輯位準(zhǔn)的額定電壓參數(shù)

參數(shù)?LVPECL?CML?VML?LVDS

VOH?2.4 V?1.9 V?1.65 V?1.4 V

VOL?1.6 V?1.1 V?0.85 V?1 V

輸出電壓 (單端)?800 mV?800 mV?800 mV?400 mV

共模電壓?2 V?1.5 V?1.25 V?1.2 V

圖8:串行I/O的邏輯位準(zhǔn)

選擇正確串行界面所應(yīng)考慮的主要因素:

- 對于功耗的整體沖擊

- 對于實作的整體沖擊

- 與光模塊和電路模塊的互用性

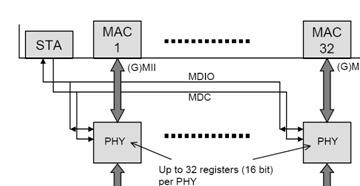

1.3 控制界面

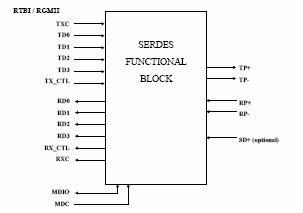

隨著芯片的連接端口不斷增加,控制界面也開始從各埠獨立的I/O接腳,演變成可靠的串行通訊總線。以太網(wǎng)絡(luò)的串行通訊總線又稱為Management Data Input Output (MDIO),它是由IEEE根據(jù)以太網(wǎng)絡(luò)標(biāo)準(zhǔn)IEEE802.3的多項內(nèi)容所定義 (第22條款)。MDIO為簡單的雙線式串行界面,它會將如微處理器的管理組件,連接到支持管理功能的收發(fā)器 (例如多端口Gigabit以太網(wǎng)絡(luò)收發(fā)器或是10GbE XAUI收發(fā)器),以便控制接收器及搜集收發(fā)器傳來的狀態(tài)信息。MDIO能夠搜集的信息包括:

- 鏈路狀態(tài)

- 速度能力和選擇

- 關(guān)機(jī)

- 省電休眠狀態(tài)

- TX/RX模式選擇

- 自動協(xié)商控制

- 回路模式控制

- 其它功能

除了IEEE要求的功能之外,收發(fā)器制造商還可自行增加其它的信息搜集功能。

? ?

?

圖9:MDIO應(yīng)用范例

設(shè)計人員在選擇Gigabit以太網(wǎng)絡(luò)收發(fā)器時,最好選擇內(nèi)建MDIO的組件,不要考慮未提供這個強(qiáng)大控制界面的產(chǎn)品。

二.功耗

功耗是選擇Gigabit以太網(wǎng)絡(luò)收發(fā)器的另一項重要考慮,幾乎所有現(xiàn)代電子裝置都很重視功耗。對于以太網(wǎng)絡(luò)交換器和路由器來說,它更成為許多連接埠密集設(shè)計的主要考慮因素。雖然Gigabit以太網(wǎng)絡(luò)連接端口密度持續(xù)增加,只要產(chǎn)品體積不變,其功率預(yù)算通常也會保持固定。基本上,設(shè)計人員必須把更多個連接埠擠進(jìn)單一機(jī)殼內(nèi),并確保總功耗不變,或僅微幅增加。新型Gigabit以太網(wǎng)絡(luò)收發(fā)器已能幫助設(shè)計人員解決這方面的部份困擾。在過去五年里,Gigabit以太網(wǎng)絡(luò)收發(fā)器所采用的芯片制程已從BiCMOS/BiPolar轉(zhuǎn)移到低功耗CMOS技術(shù),使得每個埠的功耗從1 W減少到200 mW以下。

? ?

?

圖10:功耗下降曲線

選擇Gigabit以太網(wǎng)絡(luò)收發(fā)器時,一個有用的經(jīng)驗規(guī)則是選擇CMOS制程產(chǎn)品;這類組件的個別信道功耗約從200 mW到300 mW。制程技術(shù)進(jìn)步使得組件所需電壓降低,目前多數(shù)組件都能使用2.5 V或是1.8 V電源。

三?封裝

目前大部份的多通道收發(fā)器都采用大型PBGA封裝,其接腳間距從1厘米到0.8厘米。圖11為多信道和單信道組件之間的區(qū)別。

?

圖11:多信道與單信道組件的面積比較

封裝對設(shè)計所能提供的連接埠數(shù)目有極大影響。在Gigabit以太網(wǎng)絡(luò)收發(fā)器的例子里,設(shè)計人員必須采用支持DDR并列信道模式的大型BGA封裝 (如前所述) 才能達(dá)成設(shè)計目標(biāo)。封裝的選擇應(yīng)與電路板設(shè)計限制和整體系統(tǒng)架構(gòu)一并考慮;比方說,BGA封裝雖能縮小組件體積,但當(dāng)其縮小到某個程度時,實作成本就會遠(yuǎn)超過增加連接埠所帶來的好處。隨著信道數(shù)目增加,組件也要采用更復(fù)雜麻煩的界面模式,因此今日的Gigabit以太網(wǎng)絡(luò)收發(fā)器會在這些因素之間做出適當(dāng)取舍。

選擇今日的多信道Gigabit以太網(wǎng)絡(luò)收發(fā)器時,最好選擇300只接腳以下 (視組件所支持的連接端口數(shù)目而定)、接腳間距約為1厘米、以及組件面積小于20 × 20厘米的BGA封裝。

四?成本

每埠成本是設(shè)計人員在比較不同廠商所提供的Gigabit以太網(wǎng)絡(luò)收發(fā)器時,所關(guān)心的重要因素。新型Gigabit以太網(wǎng)絡(luò)收發(fā)器大都是以針對成本最佳化的CMOS制程技術(shù)發(fā)展而成。除此之外,封裝技術(shù)的進(jìn)步、以及封裝代工市場的激烈競爭,也為市場帶來更具成本競爭力的解決方案。今天,Gigabit以太網(wǎng)絡(luò)收發(fā)器的每端口量產(chǎn)成本約從2.50美元到1.50美元。

其它直接影響成本的因素還包括實作成本 (外部零件)、電源管理需求、和散熱管理需求 (散熱片和風(fēng)扇等)。除此之外,收發(fā)器的選擇通常也會將ASIC/FPGA/MAC的發(fā)展目標(biāo)列入考慮。因此工程師不應(yīng)僅考慮Gigabit以太網(wǎng)絡(luò)收發(fā)器成本,而要將整個設(shè)計 (ASIC和收發(fā)器) 的成本當(dāng)成決策因素。

選擇Gigabit以太網(wǎng)絡(luò)收發(fā)器時,設(shè)計人員必須將整個訊號鏈納入考慮,同時將主要設(shè)計目標(biāo)當(dāng)成零件選擇的重要參考。

選擇檢查表:

1. 界面

- ASIC/FPGA的選擇和研發(fā)

- 時序零件的選擇和實作

- 控制機(jī)制

2. 電源:

- 電源層 (power plane) 設(shè)計

- 散熱管理

3. 封裝:

- 電路板設(shè)計

- 電路板布局

4. 成本:

- 系統(tǒng)整體可行性

- 實作成本

- 電路板總成本

就效能而言,所有Gigabit以太網(wǎng)絡(luò)收發(fā)器都須達(dá)到IEEE要求,才能成為合格的Gigabit以太網(wǎng)絡(luò) (IEEE802.3z) 收發(fā)器。但只有效能達(dá)到標(biāo)準(zhǔn),仍不足以在今日的市場上競爭;設(shè)計人員必須找出對其設(shè)計影響最大的其它區(qū)隔要素,例如功耗、體積、和成本等。

設(shè)計人員可以分析需要多個Gigabit以太網(wǎng)絡(luò)連接端口的應(yīng)用,以藉此了解在設(shè)計中采用新型多信道Gigabit以太網(wǎng)絡(luò)收發(fā)器會產(chǎn)生的沖擊。在此我們以24端口Gigabit以太網(wǎng)絡(luò)交換路由器為例,然后比較單信道Gigabit以太網(wǎng)絡(luò)收發(fā)器和多信道組件所造成的影響。

TI量產(chǎn)中的TLK2208A,與樣品供應(yīng)中的TLK2226是多信道Gigabit以太網(wǎng)絡(luò)收發(fā)器的兩個最佳范例。這兩顆收發(fā)器組件的重要參數(shù)如下表所示:

|

|

TLK2208B

|

TLK2226

|

|

通道數(shù)目

|

8

|

6

|

|

並列界面

|

DDR-TBI

|

RTBI/RGMII

|

|

串列

|

VML

|

VML

|

|

接腳數(shù)

|

289

|

196

|

|

封裝

|

BGA

|

BGA

|

|

封裝大小

|

19 × 19釐米

|

15 × 15釐米

|

|

總功耗

|

1.2 W

|

1 W

|

圖12:組件重要參數(shù)

在這個交換路由器的例子中,我們選擇TLK2208B做為目標(biāo)設(shè)計的收發(fā)器;其主要考慮在于節(jié)省電路板面積和降低功耗,并將ASIC界面的接腳數(shù)目減至最少。為了實作24埠解決方案,我們使用三顆TLK2208B來支持所有24個連接埠;相形之下,此設(shè)計若采用以前的單信道Gigabit以太網(wǎng)絡(luò)收發(fā)器組件,整個解決方案就需要24顆收發(fā)器。從下圖可看出,利用多信道Gigabit以太網(wǎng)絡(luò)收發(fā)器實作這套解決方案,確實能省下可觀的電路板面積。

?

圖13:電路板使用面積比較

在這個例子中若使用八通道TLK2208B收發(fā)器,就能節(jié)省高達(dá)1,300平方厘米的電路板面積。除此之外,單通道解決方案可能還需要較大的組件間距和繞線面積,這將使其占用的總電路板面積增加。

大型多信道組件多半采用新型CMOS制程技術(shù),其架構(gòu)的工作效率也高于先前產(chǎn)品,因此新型Gigabit以太網(wǎng)絡(luò)收發(fā)器設(shè)計在功耗方面自然占有優(yōu)勢。例如TLK2208B的每個通道功耗約為165 mW,傳統(tǒng)單信道組件則從250 mW到600 mW (視技術(shù)而定);這表示相較于傳統(tǒng)單通道收發(fā)器,TLK2208B之類的組件可將功耗減少35%到75%。

由于TLK2208B采用以上升邊緣和下降邊緣做為頻率的精簡位界面、共享式MDIO控制總線、和單一參考頻率輸入,因此它與MAC/ASIC的界面就比單通道解決方案更簡潔、成本也更低。若產(chǎn)品發(fā)展包括設(shè)計新的ASIC組件,那么選擇TLK2208B之類的組件就可能是唯一符合成本效益的ASIC實作解決方案。圖14是利用單信道和多信道組件進(jìn)行實作的接腳數(shù)比較。

|

使用元件

|

解決方案的接腳數(shù)目

|

|

3顆TLK2208B

|

867隻接腳

|

|

24顆64隻接腳的單通道收發(fā)器

|

1536隻接腳

|

圖 14:接腳數(shù)比較

從圖14可以看出,只要使用今日的多信道Gigabit以太網(wǎng)絡(luò)收發(fā)器,設(shè)計人員就能發(fā)展更多連接端口的系統(tǒng),并滿足功耗更少、成本更低、和體積更小等需求。在許多情形下,多信道組件的節(jié)省幅度確實相當(dāng)可觀。

根據(jù)前述的各種范例,我們可以清楚看出,今日的多端口Gigabit以太網(wǎng)絡(luò)交換器和路由器的設(shè)計并不容易。成功的數(shù)據(jù)通訊產(chǎn)品尤其如此,因為它們有眾多變量需要考慮;其中之一就是驅(qū)動Gigabit以太網(wǎng)絡(luò)光鏈路的Gigabit以太網(wǎng)絡(luò)收發(fā)器。只要選擇TI的TLK2208B和TLK2226等新型多信道Gigabit以太網(wǎng)絡(luò)收發(fā)器組件,設(shè)計人員就可以:

- 減少系統(tǒng)總功耗

- 減少總電路板面積

- 減少I/O接腳數(shù)

- 減少ASIC界面復(fù)雜性

- 減少整體的實作風(fēng)險

系統(tǒng)廠商可以利用這些優(yōu)點,發(fā)展出更可靠和更具成本競爭優(yōu)勢的設(shè)計,以確保其產(chǎn)品獲得更廣泛接受,并在市場上創(chuàng)下更輝煌的成功記錄。隨著半導(dǎo)體技術(shù)不斷進(jìn)步,系統(tǒng)的連接端口數(shù)目不斷增加, Gigabit以太網(wǎng)絡(luò)收發(fā)器組件將成為設(shè)計工程師推動Gigabit以太網(wǎng)絡(luò)連接端口快速成長的重要幫手。

電子發(fā)燒友App

電子發(fā)燒友App

評論