本文主要詳解基于FPGA的模糊PID控制器的設(shè)計(jì)實(shí)現(xiàn),首先介紹了FPGA工作原理、基本特點(diǎn)以及FPGA的優(yōu)勢(shì),其次闡述了使用Altera的FPGA設(shè)計(jì)實(shí)現(xiàn)的數(shù)字模糊PID控制器,具體的跟隨小編一起來了解一下。

2018-06-01 09:26:51 15747

15747 的認(rèn)識(shí)以外,還必須能將E1原理準(zhǔn)確地運(yùn)用到障礙處理中。一、E1(2M)電路從物理結(jié)構(gòu)上看,E1傳輸設(shè)備的E1物理接頭都是有2個(gè),一收一發(fā)。E1物理接頭阻抗可分為75Ω非平衡和120Ω平衡,75Ω非平衡

2018-02-23 10:00:09

首先要能及時(shí)和準(zhǔn)確地處理E1線路障礙,除了必須要對(duì)E1原理有清楚的認(rèn)識(shí)以外,還必須能將E1原理準(zhǔn)確地運(yùn)用到障礙處理中。一、E1(2M)電路從物理結(jié)構(gòu)上看,E1傳輸設(shè)備的E1物理接頭都是有2個(gè),一收

2017-10-28 15:32:18

當(dāng)連接E1到CS+, 電機(jī)download會(huì)出現(xiàn)下面的錯(cuò)誤,這是哪里沒有設(shè)對(duì)嗎?相同的連接使用flash programmer是可以燒寫程序的。謝謝!

2018-11-09 12:11:35

E1接口對(duì)接時(shí),雙方的E1不能有信號(hào)丟失/幀失步/復(fù)幀失步/滑碼告警,但是雙方在E1接口參數(shù)上必須完全一致,因?yàn)閭€(gè)別特性參數(shù)的不一致,不會(huì)在指示燈或者告警臺(tái)上有任何告警,但是會(huì)造成數(shù)據(jù)通道的不通/誤碼/滑碼/失步等情況。

2019-10-23 09:12:19

AE400系列E1接口音頻編解碼器,是采用先進(jìn)數(shù)字處理芯片,使用先進(jìn)的FPGA、數(shù)字編解碼轉(zhuǎn)換和時(shí)鐘恢復(fù)技術(shù)方法設(shè)計(jì)的。適用于廣播節(jié)目源傳輸的設(shè)備。音頻編碼器是將輸入的立體聲音頻信號(hào)或AES數(shù)字音頻

2011-03-02 20:51:53

FPGA實(shí)現(xiàn)的SATA控制器FPGA實(shí)現(xiàn)的SATA控制器

2012-08-11 18:08:52

我正在設(shè)計(jì)一個(gè)HDLC接收器接口。該接口看起來非常類似于SPI從器件,除了沒有外部芯片選擇進(jìn)入。幀同步發(fā)生在數(shù)據(jù)中使用唯一的令牌。因此有2個(gè)信號(hào)進(jìn)入FPGA:EXT_CLK:在我的情況下幾兆DIN

2019-04-28 12:39:33

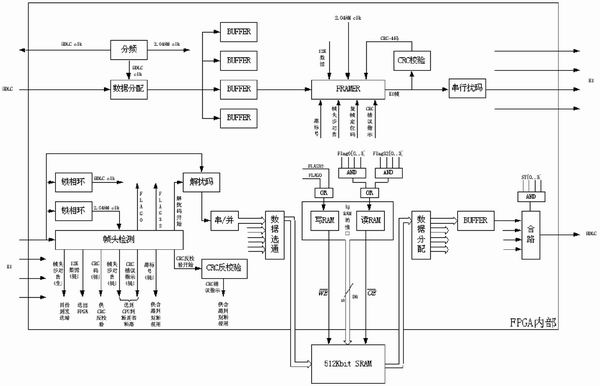

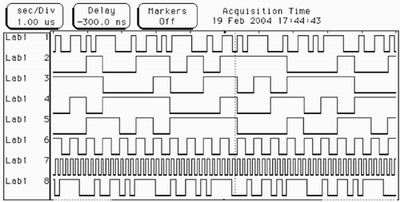

5個(gè)連“1”則在其后插入1個(gè)“0”,數(shù)據(jù)發(fā)送結(jié)束后發(fā)送幀尾“7E”。FPGA設(shè)計(jì)FPGA中實(shí)現(xiàn)的主要是鏈路層協(xié)議完成HDLC數(shù)據(jù)接口的收發(fā),并完成與DSP的數(shù)據(jù)交互,該電路由接口模塊interface

2011-03-17 10:23:56

The Keysight J3914A E1 WanProbe is a MIPS-based, SNMP-managed WANinterface monitor for E1 Wide Area Networks (WAN).

2019-07-10 14:32:38

基于SDRAM控制器實(shí)現(xiàn)FPGA模塊化和通用性的解決方案設(shè)計(jì)

2020-12-22 07:58:55

個(gè)高效、可靠的LBS控制器來實(shí)現(xiàn)FPGA和PEX8311的通信。如圖1所示。本系統(tǒng)的控制的核心是LBS控制器,該控制器是通過FPGA采用VerilogHDL實(shí)現(xiàn)的,其優(yōu)點(diǎn)是穩(wěn)定性強(qiáng)、不會(huì)造成死機(jī)

2015-01-29 14:09:17

PowerPC,dsp和fpga實(shí)現(xiàn),fpga負(fù)責(zé)接收E1口,K口等數(shù)據(jù),通過dsp的mcbsp接口傳輸到dsp,進(jìn)行話音編解碼處理,然后通過HPI接口與PowerPC交互,或者通過dsp的網(wǎng)口直接收發(fā)數(shù)據(jù)。整個(gè)設(shè)備相當(dāng)于一個(gè)路由器,它可以接入各種電臺(tái)!

2015-09-10 11:15:14

申請(qǐng)理由:項(xiàng)目描述:1.拿到開發(fā)板后,我會(huì)先把小e開發(fā)板上的模塊進(jìn)行驗(yàn)證并觀察實(shí)驗(yàn)現(xiàn)象,熟悉ESP8266芯片的時(shí)序以及寄存器。然后將手頭的Ov2640攝像頭和小e開發(fā)板連接,將正點(diǎn)原子的程序移植到

2016-10-27 11:46:02

收到小e1已經(jīng)有一段時(shí)間了,由于不知道在哪發(fā)帖(出笑話了),所以想發(fā)也一直沒發(fā),聯(lián)系“電子發(fā)燒友”后,現(xiàn)在知道在這里發(fā)帖了,好了,廢話不多說,下面開始我的分享:1 包裝簡(jiǎn)潔大方,收到開發(fā)板的第一眼

2016-12-01 19:52:01

:小E1硬件資源1耳機(jī)插孔2按鍵3USB接口 4電源開關(guān)5電源指示6氣壓傳感器 7OLED屏8跳線(4種功能)9RGB變色燈 10溫濕度傳感器11IR發(fā)射管12wifi模塊 13wifi指示燈14IR接收管15跳線帽*3以上就為小E1的開箱初體驗(yàn)。合理的布局,豐富的硬件資源是不是也讓你心動(dòng)呢?`

2016-11-01 22:33:16

本帖最后由 huajiata 于 2016-11-28 16:36 編輯

小E1的下載程序與傳統(tǒng)的略有不同,采用的為虛擬機(jī)下載,所以需要我們熟悉下載流程。準(zhǔn)備工作:1、下載小E1參考程序(附件

2016-11-28 16:30:13

距離傳感器檢測(cè)是否有阻擋物。·小e1有耳機(jī)接口,可播放音頻。硬件整體上都不錯(cuò),模塊齊全。2.軟件/云 先看看機(jī)智云:左邊是app,右邊是微信上的操作界面。送風(fēng)抽濕是控制電機(jī)的。下面來看小e1:小e1有

2016-10-29 11:39:01

平臺(tái)交互控制下,實(shí)現(xiàn)了澆花,開窗換氣,監(jiān)測(cè)土壤濕度彩虹燈效果等幾個(gè)簡(jiǎn)單功能。在兩個(gè)月的時(shí)間里,我們和小e1和諧相處,主要采用官方提供的虛擬機(jī)環(huán)境,對(duì)小e1漸漸了解,摸索開發(fā),逐步完成了各個(gè)子功能,最后

2016-12-25 17:19:00

了解了小E1,也就是從應(yīng)用層面上熟悉了小E1的使用方法,這對(duì)程序猿來說只是個(gè)開始。我們還有項(xiàng)目要做,現(xiàn)在,核心設(shè)備已經(jīng)到位,并進(jìn)行了簡(jiǎn)單的接觸,下邊需要親密接觸,來了解小E1能干什么,不能干什么,需要

2016-11-02 16:08:48

E1仿真器是瑞薩的片上調(diào)試仿真器,能用于大部分瑞薩MCU,包括RL78。 1、E1與單片機(jī)的連接,有兩種通信方式可供選擇:串行連接和JTAG連接。取決于你使用的MCU的調(diào)試接口。RL78使用單線串行

2014-12-31 17:35:36

使用Verilog實(shí)現(xiàn)基于FPGA的SDRAM控制器

2012-08-20 19:35:27

關(guān)于以太網(wǎng)到多路E1適配電路設(shè)計(jì)及FPGA實(shí)現(xiàn)你想知道的都在這

2021-05-06 06:17:04

分享如何利用FPGA設(shè)計(jì)幀存控制器的方法?從而去實(shí)現(xiàn)幀存的交替 、上電清屏等。

2021-04-08 06:19:05

D/A 轉(zhuǎn) 換 之 后 進(jìn) 行 低 通 濾 波 ,集成壓控震蕩器[9]提供載波頻率,并且可以 通 過 FPGA 配 置,IQ 上變頻器調(diào)制到射頻,再經(jīng)功放進(jìn)行功率放大,之后通過天線進(jìn)行發(fā)射 e

2023-11-07 11:33:53

目前伺服控制器的設(shè)計(jì)多以DSP或MCU為控制核心,但DSP的靈活性不如FPGA,且在某些環(huán)境比較惡劣的條件如高溫高壓下DSP的應(yīng)用效果會(huì)大打折扣,因此以FPGA為控制核心,對(duì)應(yīng)用于機(jī)載三軸伺服控制平臺(tái)的控制器進(jìn)行了設(shè)計(jì)與優(yōu)化。

2019-07-16 07:41:04

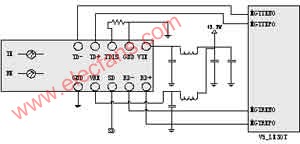

的應(yīng)用也越來越普遍。E1是我國(guó)電信傳輸網(wǎng)一次群使用的傳輸標(biāo)準(zhǔn),速率是2.048 Mb/s。實(shí)現(xiàn)多路接口與E1協(xié)議的相互轉(zhuǎn)換,將可以把多種設(shè)備同時(shí)連接至高速的E1線路。本文基于FPGA(Field

2019-06-10 05:00:04

如何實(shí)現(xiàn)家電遠(yuǎn)程控制器的設(shè)計(jì)?實(shí)現(xiàn)家電遠(yuǎn)程控制的原理及系統(tǒng)結(jié)構(gòu)是什么?Actel數(shù)模結(jié)合FPGA的特點(diǎn)有哪些?

2021-04-08 06:37:35

EFT/ESD干擾電路正常工作的機(jī)理E1抗干擾開發(fā)系統(tǒng)由那幾部分組成?如何使用E1抗干擾開發(fā)系統(tǒng)測(cè)量和定位EFT/ESD?

2021-04-08 06:49:56

本文提出了一種基于FPGA的SDRAM控制器的設(shè)計(jì)方法,并用Verilog給于實(shí)現(xiàn),仿真結(jié)果表明通過該方法設(shè)計(jì)實(shí)現(xiàn)的控制器可以在FPGA芯片內(nèi)組成如圖1所示的SDRAM接口,從而使得系統(tǒng)用戶對(duì)SDRAM的操作非常方便。

2021-04-15 06:46:56

本文研究設(shè)計(jì)了一種基于高速隔離芯片的高速串行隔離型ADC。該數(shù)字隔離型ADC頻帶寬,延時(shí)小,穩(wěn)定性高并且電路結(jié)構(gòu)簡(jiǎn)單。利用FPGA作為控制器,很好地實(shí)現(xiàn)了模數(shù)轉(zhuǎn)換和隔離傳輸。

2021-05-06 06:38:57

基于FPGA的SDRAM控制器包括哪些部分呢?如何去實(shí)現(xiàn)一種基于FPGA的SDRAM控制器設(shè)計(jì)呢?

2021-11-04 06:47:44

晚上好,如何將微控制器與FPGA連接?如何使用微控制器配置FPGA?如何使用微控制器或軟件程序?yàn)?b class="flag-6" style="color: red">FPGA創(chuàng)建.bit文件以使用微控制器配置FPGA?任何人都可以告訴發(fā)送與這些排隊(duì)相關(guān)的文件....提前致謝問候Vimala

2020-03-25 09:22:18

本文描述了E1 幀的基本結(jié)構(gòu),詳細(xì)介紹了E1 基本幀和CRC 復(fù)幀同步的算法,采用VHDL 語言對(duì)符 合G.704 和G.706 標(biāo)準(zhǔn)的成/解幀電路進(jìn)行了RTL 描述,并最終得到ASIC 實(shí)現(xiàn)。

2021-04-27 06:11:42

本文介紹通過FPGA實(shí)現(xiàn)的步進(jìn)電機(jī)控制器。該控制器可以作為單片機(jī)或DSP的一個(gè)直接數(shù)字控制的外設(shè),只需向控制器的控制寄存器和分頻寄存器寫入數(shù)據(jù),即可實(shí)現(xiàn)對(duì)步進(jìn)電機(jī)的控制。

2021-04-29 06:05:44

快速浮_定點(diǎn)PID控制器FPGA的研究與實(shí)現(xiàn)提出了基于 的快速 控制器技術(shù),采用流水線運(yùn)算方法,具有高速 穩(wěn)定精確的實(shí)時(shí)控制性能,實(shí)現(xiàn)了速度和資源的優(yōu)化匹配研究并分析了位置式 不同算式的特點(diǎn),完成

2012-08-11 15:58:43

怎么判斷一個(gè)產(chǎn)品有沒有E1接口或者說E1接口是什么樣的?最近看到產(chǎn)品EMC設(shè)計(jì)中提到E1端口需要有濾波設(shè)計(jì),但是不是很明白,我們的板子一般只有網(wǎng)口、串口之類的!求前輩指點(diǎn)!!!

2016-04-23 11:36:56

與低速的E1信號(hào)結(jié)合起來,實(shí)現(xiàn)以太網(wǎng)與E1信號(hào)的復(fù)用。既滿足了用戶對(duì)大帶寬、高容量數(shù)據(jù)的傳輸要求,又提供了E1信號(hào)接入功能,實(shí)現(xiàn)電話業(yè)務(wù)及其他專用通信系統(tǒng)的接入功能。

2019-08-14 08:01:09

親愛的朋友們,我聽說我們甚至可以通過FPGA實(shí)現(xiàn)微控制器。例如,我們可以用FPGA實(shí)現(xiàn)AVR micro。我的問題是:我們?cè)鯓硬拍苁褂盟考僭O(shè)我們已經(jīng)用C語言編寫了代碼,現(xiàn)在我們改變了主意,決定用

2019-03-22 07:32:06

求一種基于FPGA的HDLC協(xié)議控制器設(shè)計(jì)方案

2021-04-30 06:53:06

本帖最后由 eehome 于 2013-1-5 10:08 編輯

現(xiàn)有USB(CP210X)轉(zhuǎn)GPIB控制器,安裝完驅(qū)動(dòng)后設(shè)備管理器中設(shè)備顯示為COM,如何通過這個(gè)COM來通過GPIB控制儀器,求各位前輩指點(diǎn).在此獻(xiàn)出全副身家 3E!~~~謝謝!!

2012-10-16 17:41:36

使用E1仿真器在E2 studio調(diào)試,芯片是Rh850,求解決辦法

2017-10-18 17:41:43

我是新手,使用附件的E1接線方式下載HEX數(shù)據(jù)到R5F51115這個(gè)芯片中,E1提示沒法連到芯片,有哪位可以指導(dǎo)下嗎?

2020-04-15 10:04:50

基于FPGA的MCU設(shè)計(jì)有兩種基本實(shí)現(xiàn)方式如何實(shí)現(xiàn)微控制器與FPGA的接口設(shè)計(jì)

2021-05-06 10:05:17

針對(duì)微控制器應(yīng)用的FPGA的實(shí)現(xiàn)

2012-08-20 23:47:47

一:概述1路E1 PDH光端機(jī)是漢源高科(北京)科技有限公司以超大規(guī)模集成電路核心構(gòu)成的1路光電合一傳輸設(shè)備。可提供面向電信的E1傳輸,面向ISDN的傳輸和多種接口(音頻、數(shù)據(jù)),面向 LAN

2022-06-13 21:14:08

本文主要以 ARM7TDMI 為內(nèi)核的Samsung’s S3C4510B 網(wǎng)絡(luò)微控制器(NetworkingMCU)為基礎(chǔ),重點(diǎn)論述了如何通過DMA(直接內(nèi)存訪問)方式實(shí)現(xiàn)HDLC 通信。對(duì)軟件設(shè)計(jì)中緩沖描述符,DMA 狀態(tài)配置

2009-04-16 14:24:40 13

13 本文主要以 ARM7TDMI 為內(nèi)核的Samsung’s S3C4510B 網(wǎng)絡(luò)微控制器(NetworkingMCU)為基礎(chǔ),重點(diǎn)論述了如何通過DMA(直接內(nèi)存訪問)方式實(shí)現(xiàn)HDLC 通信。對(duì)軟件設(shè)計(jì)中緩沖描述符,DMA 狀態(tài)配置

2009-05-14 14:24:44 18

18 傳統(tǒng)交通燈控制器多數(shù)由單片機(jī)或PLC 實(shí)現(xiàn)。本論文介紹一種用FPGA 實(shí)現(xiàn)交通燈控制器的設(shè)計(jì)方法。關(guān)鍵詞:FPGA; VHDL; MAXPLUSll; 交通燈控制器Abstract:Traffic light controller is usually

2009-06-12 11:12:52 90

90 以太網(wǎng)到多路E1適配電路設(shè)計(jì)及FPGA實(shí)現(xiàn)

摘要:介紹了一種基于現(xiàn)場(chǎng)可編程門陣列(FPGA)的以太網(wǎng)數(shù)據(jù)-多路E1反向復(fù)用器同步電路設(shè)計(jì),分析了FPGA具體實(shí)現(xiàn)過程中的一些常

2009-11-13 20:59:00 22

22 基于ARM和FPGA的圓網(wǎng)印花機(jī)控制器的實(shí)現(xiàn):根據(jù)傳統(tǒng)圓網(wǎng)印花機(jī)的結(jié)構(gòu)以及存在的問題。提出了基于ARNi和FPGA的嵌入式圓網(wǎng)印花機(jī)控制器的設(shè)計(jì)方案。并開發(fā)了試驗(yàn)樣機(jī)系統(tǒng)。充分利用

2009-11-20 17:43:36 12

12 NandFlash控制器的FPGA實(shí)現(xiàn)方法技巧與程序案例分享。

2017-09-21 09:40:00 78

78 使用嵌入式微處理器S3C4510B內(nèi)部包含的HDLC控制器封裝和解析HDLC協(xié)議,微處理器既可實(shí)現(xiàn)系統(tǒng)功能,又可完成HDLC協(xié)議的數(shù)據(jù)傳輸,降低了設(shè)計(jì)的復(fù)雜度。本設(shè)計(jì)已應(yīng)用于微波網(wǎng)絡(luò)管理

2010-07-08 15:26:27 46

46 利用FPGA 設(shè)計(jì)一個(gè)類似點(diǎn)陣LCD 顯示的VGA 顯示控制器,可實(shí)現(xiàn)文字及簡(jiǎn)單的圖表顯示。工作時(shí)只需將要顯示內(nèi)容轉(zhuǎn)換成對(duì)應(yīng)字模送入FPGA,即可實(shí)現(xiàn)相應(yīng)內(nèi)容的顯示。關(guān)鍵詞:FPGA

2010-09-22 10:17:23 137

137 為了滿足某測(cè)控平臺(tái)的設(shè)計(jì)要求,設(shè)計(jì)并實(shí)現(xiàn)了基于FPGA的六通道HDLC并行通信系統(tǒng)。該系統(tǒng)以FPGA為核心,包括FPGA、DSP、485轉(zhuǎn)換接口等部分。給出了系統(tǒng)的電路設(shè)計(jì)、關(guān)鍵模塊及軟件

2010-09-30 16:49:30 43

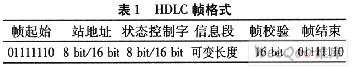

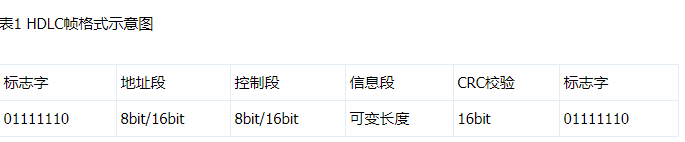

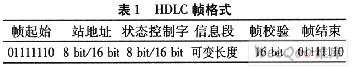

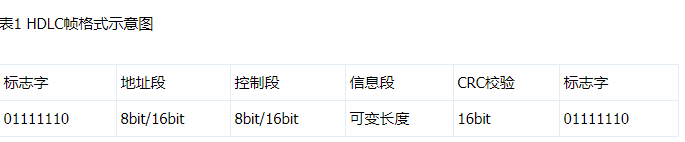

43 高級(jí)數(shù)據(jù)鏈路控制HDLC協(xié)議是一種面向比特的鏈路層協(xié)議,具有同步傳輸數(shù)據(jù)、冗余度低等特點(diǎn),是在通信領(lǐng)域中應(yīng)用最廣泛的鏈路層協(xié)議之一。提出實(shí)現(xiàn)HDLC通信協(xié)議的主要模塊—

2010-11-26 16:51:03 32

32 在WTB底層協(xié)議的研究中,其基本幀格式與ISO3309的HDLC要求一致,故設(shè)計(jì)了一種基于FPGA的HDLC編解碼器。重點(diǎn)介紹了協(xié)議和實(shí)現(xiàn)方法,給出了相應(yīng)的Verilog代碼,通過硬件下載與標(biāo)準(zhǔn)的WTB

2010-12-11 16:07:25 26

26 DS31256 HDLC控制器的配置步驟—橋接模式

本應(yīng)用筆記提供了怎樣配置橋接模式下DS31256 HDLC控制器T1端口的例子。文章提供了一個(gè)實(shí)際例程,以方便最終用戶使用,幫助他

2009-04-21 14:59:48 1374

1374

DS31256 -256通道、高吞吐率HDLC控制器

概述

DS31256是一款256通道高層數(shù)據(jù)鏈路控制器(HDLC),

2009-04-21 23:17:11 1235

1235

摘 要:介紹了SDRAM的特點(diǎn)和工作原理,提出了一種基于FPGA的SDRAM控制器的設(shè)計(jì)方法,使用該方法實(shí)現(xiàn)的控制器可非常方便地對(duì)SDRAM進(jìn)行控制。

關(guān)鍵

2009-06-20 13:04:51 2075

2075 摘要: HDLC(高級(jí)數(shù)據(jù)鏈路控制)的一般實(shí)現(xiàn)方法為采用ASIC器件和軟件編程等。應(yīng)用ASIC器件時(shí)設(shè)計(jì)簡(jiǎn)單,但靈活性較差;軟件編程方法靈活,但占用處理器資源多

2009-06-20 13:47:15 3244

3244

基于FPGA的多通道HDLC收發(fā)電路設(shè)計(jì)

HDLC(High Level Date Link Control)協(xié)議是通信領(lǐng)域中應(yīng)用最廣泛的協(xié)議之一,它是面向比特的高級(jí)數(shù)據(jù)鏈路控制規(guī)程,具有差錯(cuò)檢測(cè)功能強(qiáng)大

2009-12-10 10:14:35 1435

1435 高級(jí)數(shù)據(jù)鏈路控制(HDLC)是什么意思

高級(jí)數(shù)據(jù)鏈路控制(HDLC)協(xié)議是基于的一種數(shù)據(jù)鏈路層協(xié)議,促進(jìn)傳送到下一層的數(shù)據(jù)在傳輸過程中能夠準(zhǔn)確

2010-03-18 15:30:24 1346

1346 本文設(shè)計(jì)的基于Xilinx FPGA的千兆位以太網(wǎng)及E1信號(hào)的光纖傳輸系統(tǒng)采用Xilinx XC5VLX30T芯片,通過以太網(wǎng)測(cè)試儀和數(shù)據(jù)誤碼儀對(duì)本系

2010-07-06 09:09:10 2337

2337

摘要:為了實(shí)現(xiàn)高速HDLC通訊協(xié)議,設(shè)計(jì)了DSP+FPGA結(jié)構(gòu)的485通訊接口,接口包括DSP、FPGA、485轉(zhuǎn)換等硬件電路,以及DSP與FPGA之間的數(shù)據(jù)交換程序和FPGA內(nèi)部狀態(tài)機(jī);其中DSP用于實(shí)現(xiàn)數(shù)據(jù)控制,FPGA用于實(shí)現(xiàn)HDLC通訊協(xié)議,DSP與FPGA之間采用XINTF方式,通過雙FI

2011-02-25 17:24:34 98

98 HDLC協(xié)議是通信領(lǐng)域中應(yīng)用最廣泛的協(xié)議之一! 它是面向位的高級(jí)數(shù)據(jù)鏈路控制規(guī)程! 具有差錯(cuò)檢測(cè)功能強(qiáng)大 高效和同步傳輸的特點(diǎn),目前市場(chǎng)上有很多專用的HDLC芯片! 但這些芯片功能和接

2011-05-17 10:40:26 91

91 為了實(shí)現(xiàn)軍航管制系統(tǒng)中雷達(dá)數(shù)據(jù)的可靠傳輸,根據(jù) HDLC 協(xié)議的幀結(jié)構(gòu)和循環(huán)冗余校驗(yàn)(CRC)原理,提出了一種新型的基于并行機(jī)制的HDLC協(xié)議控制器,討論采用FPGA新技術(shù)實(shí)現(xiàn)HDLC協(xié)議幀的構(gòu)成

2011-07-20 16:17:50 93

93 研究實(shí)現(xiàn)了一種 HDLC (High Level Data Link Contr01)協(xié)議的改進(jìn)方法,該方法把HDLC協(xié)議傳統(tǒng)的同步傳榆方式改成了異步傳輸方式,既保留了原有HDLC協(xié)議的主要優(yōu)點(diǎn),又增強(qiáng)了傳榆教據(jù)的抗干擾

2011-07-20 17:25:50 62

62 介紹了HDLC協(xié)議RS485總線控制器的FPGA實(shí)現(xiàn)

2012-02-14 14:59:36 100

100 介紹了一種基于FPGA的多軸控制器,控制器主要由ARM7(LPC2214)和FPGA(EP2C5T144C8)及其外圍電路組成,用于同時(shí)控制多路電機(jī)的運(yùn)動(dòng)。利用Verilog HDL 硬件描述語言在FPGA中實(shí)現(xiàn)了電機(jī)控制邏

2013-04-27 16:23:11 82

82 Xilinx FPGA工程例子源碼:FPGA實(shí)現(xiàn)CAN總線控制器源碼

2016-06-07 14:13:43 87

87 基于FPGA的VGA圖像控制器的設(shè)計(jì)與實(shí)現(xiàn)

2016-08-30 15:10:14 11

11 一種基于FPGA的E1數(shù)字傳輸分析儀成解幀實(shí)現(xiàn)方法_耿立華

2017-03-14 16:50:00 2

2 DSP和FPGA的HDLC協(xié)議通訊電路設(shè)計(jì)

2017-10-19 14:46:11 7

7 引言 HDLC(高級(jí)數(shù)據(jù)鏈路控制)廣泛應(yīng)用于數(shù)據(jù)通信領(lǐng)域,是確保數(shù)據(jù)信息可靠互通的重要技術(shù)。實(shí)施HDLC的一般方法通常是采用ASIC器件或軟件編程等。 HDLC的ASIC芯片使用簡(jiǎn)易,功能針對(duì)性

2017-10-25 16:52:15 0

0 HDLC(高級(jí)數(shù)據(jù)鏈路控制)廣泛應(yīng)用于數(shù)據(jù)通信領(lǐng)域,是確保數(shù)據(jù)信息可靠互通的重要技術(shù)。實(shí)施HDLC的一般方法通常是采用ASIC器件或軟件編程等。 HDLC的ASIC芯片使用簡(jiǎn)易,功能針對(duì)性強(qiáng),性能

2017-10-26 16:50:59 1

1 嘗試在 FPGA 上實(shí)現(xiàn)對(duì) IC 卡的控制, 運(yùn)用 EDK 中的 IP 開發(fā)工具生成一個(gè)智能卡控制器的 IP 核,用以實(shí)現(xiàn)對(duì) IC 卡的硬件控制。 智 能 卡 (Smart Card

2017-11-07 16:17:56 2

2 高級(jí)數(shù)據(jù)鏈路控制(HDLC,High-Level Data Control)是一種同步數(shù)據(jù)傳輸、面向比特的數(shù)據(jù)鏈路層協(xié)議,具有差錯(cuò)檢測(cè)功能強(qiáng)大、高效和同步傳輸的特點(diǎn),目前HDLC協(xié)議已成為是通信領(lǐng)域中應(yīng)用最廣泛的協(xié)議之一,在飛行器設(shè)計(jì)領(lǐng)域經(jīng)常用作飛控與舵機(jī),助推器等之間通信的通信協(xié)議。

2018-05-05 09:26:00 2457

2457

FPGA能對(duì)任意數(shù)據(jù)寬度的信號(hào)進(jìn)行處理,內(nèi)部的功能模塊可以并行處理。因此,采用FPGA技術(shù)設(shè)計(jì)HDLC協(xié)議控制器可以均衡整個(gè)系統(tǒng)的負(fù)荷,實(shí)現(xiàn)多通道的高性能HDLC協(xié)議控制器,保證通信的可靠性。同時(shí)

2018-12-30 11:00:00 2975

2975

上百萬門.同時(shí)它還具有設(shè)計(jì)開發(fā)周期短、設(shè)計(jì)制造成本低、可實(shí)時(shí)在線檢驗(yàn)等優(yōu)點(diǎn),因此被廣泛用于特殊芯片設(shè)計(jì)中.本設(shè)計(jì)中采用Altera公司的FLEX10K芯片EPF10K20RC240-3來實(shí)現(xiàn)HDLC協(xié)議控制器.

2020-09-27 21:00:12 933

933

為了實(shí)現(xiàn)軍航管制系統(tǒng)中雷達(dá)數(shù)據(jù)的可靠傳輸,根據(jù)HDLC協(xié)議的幀結(jié)構(gòu)和循環(huán)冗余校驗(yàn)(CRC)原理,提出了一種新型的基于并行機(jī)制的HDLC協(xié)議控制器,討論采用FPGA新技術(shù)實(shí)現(xiàn)HDLC協(xié)議幀的構(gòu)成

2020-11-04 18:04:10 15

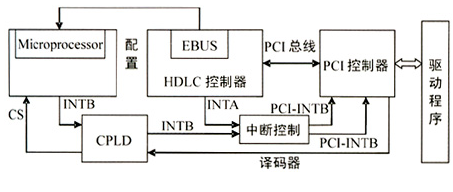

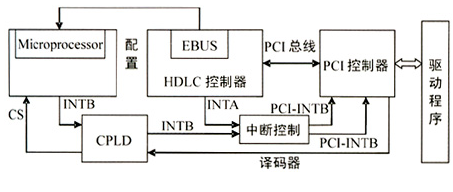

15 E1數(shù)據(jù)采集卡從E1線上采集信令消息(包括七號(hào)信令等),用以監(jiān)視和仿真整個(gè)通話流程。控制流程如圖1所示,PCI接口芯片(HDLC控制器)是一個(gè)多功能設(shè)備,包括一個(gè)網(wǎng)絡(luò)控制器和一個(gè)PCI橋設(shè)備

2021-05-22 15:31:17 2813

2813

實(shí)現(xiàn)基于FPGA的SPIFlash控制器設(shè)計(jì)(嵌入式開發(fā)工作怎么樣)-該文檔為實(shí)現(xiàn)基于FPGA的SPIFlash控制器設(shè)計(jì)簡(jiǎn)介資料,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-30 09:10:17 4

4 DS31256有16個(gè)物理端口(16 Tx和16 Rx)或鏈路,可配置為信道化或非信道化。通道化端口可以處理一個(gè)、兩個(gè)或四個(gè) T1 或 E1 數(shù)據(jù)鏈路。這些端口或鏈路的時(shí)鐘可以支持間隔時(shí)鐘。本應(yīng)用筆記介紹如何在256通道HDLC控制器DS31256中實(shí)現(xiàn)間隙時(shí)鐘應(yīng)用。

2023-01-13 10:25:28 479

479

電子發(fā)燒友網(wǎng)站提供《步進(jìn)電機(jī)控制器的FPGA的實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-10-07 16:29:17 1

1 實(shí)時(shí)視頻SDRAM控制器的FPGA設(shè)計(jì)與實(shí)現(xiàn)

2022-12-30 09:21:26 3

3

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論