同步模塊是每個系統的心臟,它為系統中的其他每個模塊饋送正確的時鐘信號。因此需要對同步模塊的設計和實現給予特別關注。本文對影響系統設計的時鐘特性進行了考察,并對信號惡化的原因進行了評估。本文還分析了同步惡化的影響,并對標準化組織為確保傳輸質量和各種傳輸設備的互操作性而制定的標準要求進行了探討。

摘要:

網絡同步和時鐘產生是高速傳輸系統設計的重要方面。為了通過降低發射和接收錯誤來提高網絡效率,必須使系統的各個階段都要使用的時鐘的質量保持特定的等級。網絡標準定義同步網絡的體系結構及其在標準接口上的預期性能,以保證傳輸質量和傳輸設備的無縫集成。有大量的同步問題,系統設計人員在建立系統體系結構時必須十分清楚。本文論述了時鐘惡化的各種來源,如抖動和漂移。本文還討論了傳輸系統中時鐘惡化的原因和影響,并分析了標準要求,提出了各種實現技巧。

基本概念:抖動和漂移

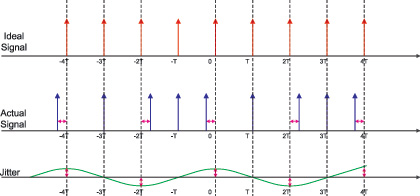

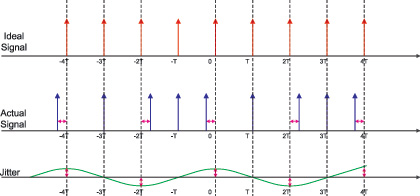

抖動的一般定義可以是“一個事件對其理想出現的短暫偏離”。在數字傳輸系統中,抖動被定義為數字信號的重要時刻在時間上偏離其理想位置的短暫變動。重要時刻可以是一個周期為 T1 的位流的最佳采樣時刻。雖然希望各個位在 T 的整數倍位置出現,但實際上會有所不同。這種脈沖位置調制被認為是一種抖動。這也被稱為數字信號的相位噪聲。在下圖中,實際信號邊沿在理想信號邊沿附近作周期性移動,演示了周期性抖動的概念。

圖 1.抖動示意

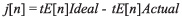

抖動,不同于相位噪聲,它以單位間隔 (UI) 為單位來表示。一個單位間隔相當于一個信號周期 (T),等于 360 度。假設事件為 E,第 n 次出現表示為 tE[n] 。則瞬時抖動可以表示為:

一組包括 N 個抖動測量的峰到峰抖動值使用最小和最大瞬時抖動測量計算如下:

漂移是低頻抖動。兩者之間的典型劃分點為 10 Hz。抖動和漂移所導致的影響會顯現在傳輸系統的不同但特定的區域。

抖動類型

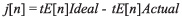

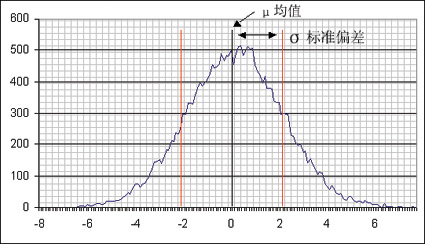

根據產生原因,抖動可分成兩種主要類型:隨機抖動和確定性抖動。隨機抖動,正如其名,是不可預測的,由隨機的噪聲影響如熱噪聲等引起。隨機抖動通常發生在數字信號的邊沿轉換期間,造成隨機的區間交叉。毫無疑問,隨機抖動具有高斯概率密度函數 (PDF),由其均值 (μ) 和均方根值 (rms) (σ) 決定。由于高斯函數的尾在均值的兩側無限延伸,瞬時抖動和峰到峰抖動可以是無限值。因此隨機抖動通常采用其均方根值來表示和測量。

圖 2.以高斯概率密度函數表示的隨機抖動

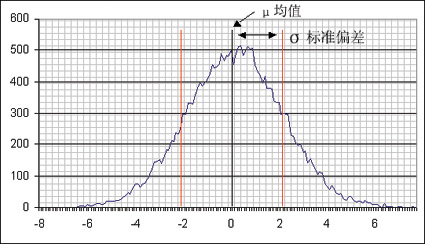

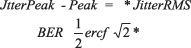

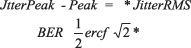

對抖動余量來講,峰到峰抖動比均方根抖動更為有用,因此需要把隨機抖動的均方根值轉換成峰到峰值。為將均方根抖動轉換成峰到峰抖動,定義了隨機抖動高斯函數的任意極限 (arbitrary limit)。誤碼率 (BER) 是這種轉換中的一個有用參數,其假設高斯函數中的瞬時抖動一旦落在其強制極限之外即出現誤碼。通過下面兩個公式,就可以得到均方根抖動到峰到峰抖動的換算。3

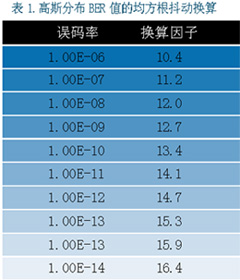

由公式可得到下表,表中峰到峰抖動對應不同的 BER 值。

確定性抖動是有界的,因此可以預測,且具有確定的幅度極限。考慮集成電路 (IC) 系統,有大量的工藝、器件和系統級因素將會影響確定性抖動。占空比失真 (DCD) 和脈沖寬度失真 (PWD) 會造成數字信號的失真,使過零區間偏離理想位置,向上或向下移動。這些失真通常是由信號的上升沿和下降沿之間時序不同而造成。如果非平衡系統中存在地電位漂移、差分輸入之間存在電壓偏移、信號的上升和下降時間出現變化等,也可能造成這種失真。

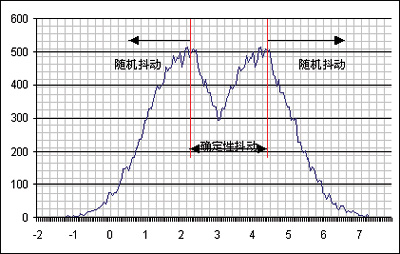

圖 3,總抖動的雙模表示

數據相關抖動 (DDJ) 和符號間干擾 (ISI) 致使信號具有不同的過零區間電平,導致每種唯一的位型出現不同的信號轉換。這也稱為模式相關抖動 (PDJ)。信號路徑的低頻截止點和高頻帶寬將影響 DDJ。當信號路徑的帶寬可與信號的帶寬進行比較時,位就會延伸到相鄰位時間內,造成符號間干擾 (ISI)。低頻截止點會使低頻器件的信號出現失真,而系統的高頻帶寬限制將使高頻器件性能下降。7

正弦抖動以正弦模式調制信號邊沿。這可能是由于供給整個系統的電源或者甚至系統中的其他振蕩造成。接地反彈和其他電源變動也可能造成正弦抖動。正弦抖動廣泛用于抖動環境的測試和仿真。不相關抖動可能由電源噪聲或串擾和其他電磁干擾造成。

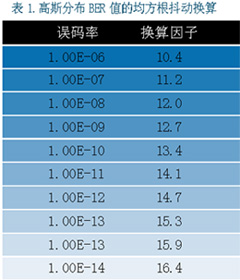

考慮抖動對數字信號的影響時,需要將整個確定性抖動和隨機抖動考慮在內。確定性抖動和隨機抖動的總計結果將產生另外一種概率分布4:雙模響應,其中部表示確定性抖動,尾部為高斯響應,表示隨機抖動分量。

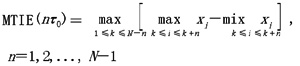

抖動測量 — TIE、MITE 和 TEDV

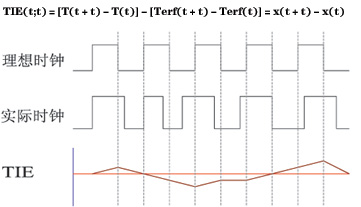

時間間隔誤差 (TIE) 是通過對實際時鐘間隔的測量和對理想參考時鐘同一間隔的測量得到的。在給定時間 t,以一個稱為觀測間隔的時間間隔產生時間 T(t) 的時鐘,其相對于時鐘 Tref(t) 的TIE 可通過下面公式表示。(x(t) 稱為誤差函數。)

TIE 表示信號中的高頻相位噪聲,提供了實際時鐘的每個周期偏離理想情況的直接信息。TIE 用于計算大量統計派生函數如 MTIE、TDEV 等。

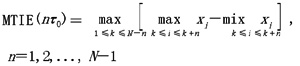

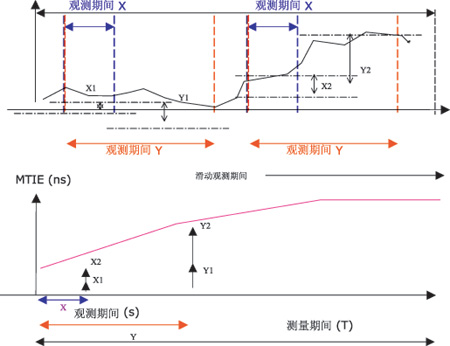

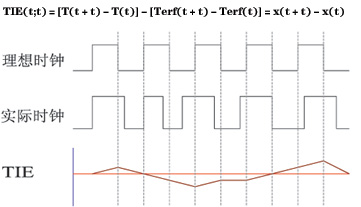

最大時間間隔誤差 (MTIE) 定義為,在一個觀測時間 (t=nt0) 內,一個給定時鐘信號相對于一個理想時鐘信號的最大峰到峰延遲變化,其中該長度的所有觀測時間均在測量周期 (T) 之內。使用下面公式進行估計:

MTIE是針對時間的緩變或漂移而定義的。當需要分析時鐘的長期特性時,就需要對MTIE進行測量。MTIE 值是對一個時鐘信號的長期穩定性的一種衡量。

圖 4.TIE 的圖形表示

TDEV 是另外一個統計參數,作為集成時間的函數對一個信號的預期時間變化的測量。DEV 也能提供有關信號相位(時間)噪聲頻譜分量的信息。TIE 圖中每個點的標準偏差是對一個觀測間隔計算的,該觀測間隔滑過整個測量時間。該值在整個上述測量時間內進行平均以得到該特定間隔的 TDEV 值。增大觀測間隔,重復測量過程。TDEV 是對短期穩定性的一種衡量,在評估時鐘振蕩器性能時有用。TDEV 屬于時間單位。

高速傳輸系統中抖動和漂移的原因

最常用的一種時鐘體系結構是,在備板上運行一個低頻時鐘,在每個傳輸卡上產生同步的高頻時鐘。低頻時鐘在集成電路內或通過分立 PLL 實現進行倍頻以產生高頻時鐘。通過典型的 PLL 倍頻,倍頻后時鐘上的相位噪聲增大為原來時鐘相位噪聲的 20*log(N) 次方,其中 N 為倍頻系數。此外,PLL 參考時鐘輸入上的抖動將延長鎖定時間,且當輸入抖動過大時高速 PLL 甚至無法實現鎖定。在備板上采用一種更高速的差分時鐘將比采用低速單端時鐘具有更好的抖動性能。

由于 VCO 對輸入電壓變化較為敏感,因此電源噪聲是增大時鐘抖動的一個主要因素。輸出時鐘抖動幅度與電源噪聲幅度、VCO 增益成正比,與噪聲頻率成反比。因導線電阻形成的電阻下降和因導線電感形成的電感噪聲而造成的電源或接地反彈,會對上述輸出時鐘抖動產生相似的影響。在系統板上對電源進行充分過濾,靠近集成電路電源引腳提供去耦電容,可以確保 PLL 獲得更高的抖動性能。

在系統板內,時鐘和數據相互獨立,發射和接收端在啟動、保持和延遲時間方面的變化對高速率非常關鍵。因數據和時鐘路徑中存在不同有源元件而使數據和時鐘路徑之間出現傳播延遲差異, 時鐘路徑之間的接線延遲差異,數據位之間的接線延遲差異,數據和時鐘路徑之間不同的負載情況,分組長度差異等等,均可能造成上述變化。在規劃系統抖動余量時,必須將不同信號路徑的變化考慮在內。

當在一段距離上進行傳輸時,在發射機和接收機中的很多點上存在抖動累積。在發射機物理層實現中,DAC 非線性或激光非線性等非線性特性會加重信號失真。在傳輸介質和接收機中,除了外部亂真源(大多在銅導線中)之外,因不同頻率和調制效應而導致的光纖失真、因接收機實現(主要與帶寬有關)和時鐘提取電路實現而導致的信號相關相位偏離,會加重信號流的抖動。

圖 5.來自 TIE 圖的 MTIE 偏差

具體到 SDH(同步數字系列)傳輸,有大量的系統級事件會導致抖動。在將 PDH(準同步數字系列)支路映射為 SDH 幀并通過 SDH NE(網絡組件)進行傳輸的典型傳輸系統中,在 PDH 支路于 SDH 的終端多路分配器解映射之前,將在每個中間節點處出現 VC(虛擬容器)的重新同步。有間隙的時鐘用于將各個支路映射到 STM-N 幀和從 STM-N 幀解映射,發出與開銷、固定填充和調整位相應的脈沖,因而造成映射抖動。采用調整機會位補償 PDF 支路中頻率偏移的方法會造成等待時間抖動。還有指針調整機制,用于對來自初始 NE 的輸入 VC 與本地產生的輸出 STM-N 幀之間的相位波動進行補償。根據頻率偏離,VC 在 STM-N 幀中前后移動。這將使 VC 提取點看到位流中的突然變化,導致稱為指針抖動的類型抖動。所有上述系統級抖動都將加重總的確定性抖動。

盡管所有上述因素都會加重從源到目的地之間信號傳播的抖動,標準要求仍然規定在傳輸點需具有比理論值更低的抖動數值。這樣,考慮到時鐘倍頻、電源變化、電-光-電轉換、發射和接收影響以及其他致使實際信號惡化的失真信號的影響,在源處驅動信號的時鐘將具有一個相對很低的抖動數值。

抖動對收發器的影響

理想情況下,數字信號是在兩個相鄰電平轉換點的中點進行采樣的。抖動之所以會造成誤碼,是由于相對于理想中點,它改變了信號的邊沿轉換點。誤碼可能由于信號流邊沿變化太晚(在時間上比理想中點晚0.5UI(單位間隔相當于信號的一個周期))或太早(在時間上比理想中點早0.5UI)所致。當時鐘采樣邊沿在信號流的任何一側錯過0.5UI 時,將出現 50% 的誤碼概率,假設平均轉換密度為 0.5。7如果分別知道確定性抖動和隨機抖動,可通過上述兩個數字和將峰到峰抖動值與均方根抖動值聯系在一起的表,來估計誤碼率。校準抖動,定義為數字信號的最佳采樣時刻與從其提取出來的采樣時鐘之間的短期變化,可以造成上述誤碼。對于商業應用,源時鐘和源發射接口抖動規范將遠遠低于 1UI。

發射接口抖動規范通常與接收端的輸入抖動容限相匹配。對于抖動測量回路濾波器截止頻率,尤其如此。例如,在 SDH 系統中,有兩種抖動測量帶寬,分別規定:一個用于寬帶測量濾波器(f1 到 f4),一個用于高頻帶測量濾波器(f3 到 f4)。數值 f1 指可在線路系統的 PLL 中使用的輸出時鐘信號的最窄時鐘截止頻率。低于此帶寬的頻率的抖動將通過系統,而較高頻率的抖動則被部分吸收。數值 f3 表示輸入時鐘捕獲電路的帶寬。高于此頻率的抖動將導致校準抖動。校準抖動造成光功率損失,需要額外光功率以防各種惡化。因此限制發射機端高頻帶頻譜的抖動十分重要。

漂移對收發器的影響

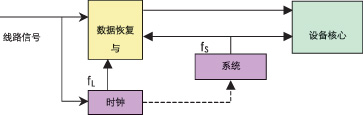

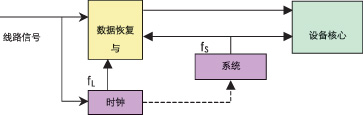

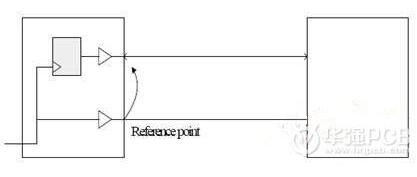

市場上銷售的大多數電信接收機都使用了一個緩沖器,以適應線路信號中存在的隨機波動。下面框圖6詳細表示出這一概念。恢復時鐘將數據送入富有彈性的緩沖器,而系統時鐘則將數據送出到設備的核心部位。

在準同步傳輸系統中,發射機和接收機工作在相互獨立而又極為接近的頻率上,fL和 Fs分別表示發射機和接收機的頻率。當兩者之間存在相位或頻率差異時,彈性存儲會將其消除,否則緩沖器將出現欠載或溢出(取決于差異的幅度和彈性緩沖器的大小),造成一次可控的幀滑動(基本速率傳輸)或一次位調整(高階異步多路復用器)。

在準同步應用中,根據可接受的緩沖滑動對頻率變化和緩沖器深度進行了標準化。最初的網絡主要用于語音傳輸,在一定的頻率門限之下不會造成語音質量下降。ITU-T 規范規定該變化為 +/-50ppm。但是隨著網絡開始傳送壓縮語音、傳真格式的數據、視頻以及其他種類的媒體應用,對于差錯和重傳以及剛剛興起的同步網絡,滑動使效率嚴重下降。

在同步傳輸系統中,系統時鐘通常同步到用于接收更高時鐘等級信號的接口的恢復時鐘上。恢復時鐘和系統時鐘之間相位和頻率的瞬時和累積差異將被彈性緩沖器吸收,否則將導致彈性存儲器溢出/欠載(取決于緩沖器大小和變化的幅度),造成指針調整而延遲或提前幀傳輸、幀滑動或系統中某處出現位調整。

在同步系統中,所有網絡組件工作在同一平均頻率,可以通過指針機制消除幀惡化。這些指針機制將提前或延遲有效載荷在傳輸幀中的位置,從而調整接收和系統時鐘中存在的頻率和相位變化。SDH 收發器中的緩沖器比 PDH 收發器中的要小,而且對于 SDH 系統中可能導致的指針移動等不規則性有限制。因此,與 PDH 系統相比,同步系統的要求更為嚴格。由于網絡發展的歷史和不同網絡之間的互操作連接,在某些階段或其他階段,這些同步網絡會通過準同步網絡來連接。因此 PDH 網絡的時鐘體系結構也要考慮在內。

MTIE 提供了時鐘相對于已知理想參考時鐘的峰值時間變化。在同步傳輸和交換設備的彈性緩沖器的設計中將用到 MTIE 值。在彈性存儲中,緩沖器填充水平與輸入數字信號和本地系統時鐘之間的 TIE 成正比。確保時鐘符合有關 MTIE 的時鐘規范,將保證不會超過一定的緩沖器門限。因此,在緩沖器設計中,其大小取決于 MTIE 的規定極限。

圖6,典型傳輸系統的接收機接口

系統時鐘輸出相位擾動對收發器的影響

一個時鐘的輸出相位變化可以通過分析其 MTIE 信息獲得。漂移產生(在自由振蕩模式和同步模式中)主要指系統中所用時鐘振蕩器的長期穩定性,在自由振蕩模式中系統的穩定性僅受振蕩器的穩定性影響。除了漂移產生之外,輸出時鐘相位還受到大量系統不規則特性的影響。

特別是對一個系統同步器而言,將參考源從一個不良或惡化參考時鐘轉換到一個正常參考時鐘可能會導致輸出相位擾動。傳輸用高速 PLL 中使用的傳統 VCO(壓控振蕩器)在改變參考時鐘時采用了切換電容器組的方法。這種切換轉換會對輸出時鐘造成暫時的相位偏移。采用超低抖動時鐘倍頻器電路可以解決這個問題。

高性能網絡時鐘在系統的所有參考時鐘都失去時采用一種稱為“保持”的機制。這是通過記憶存儲技術產生系統最后一個已知良好參考時鐘來實現的。進入和退出保持模式可能會對輸出造成相位擾動。當處于保持模式中時,由于準確頻率的再生不夠精確,因此會繼續產生輸出相位誤差。集成電路技術的進步已使保持精度達到了 0.01ppb。輸入參考時鐘惡化和對系統的維護測試(不會導致參考時鐘切換)過少,也會造成輸出相位擾動。

系統輸出擾動是有限的,取決于系統在較低層次可以接受的輸入容限。例如,符合 G.813 選項 1 的時鐘,其相位擾動中所允許的相位斜率和最大相位誤差被限制為 1μS,最大相位斜率為 7.5ppm,兩個 120ns 相位誤差段,其余部分的相位斜率為 0.05ppm。這些數字對應于 G.825 標準規定的輸入抖動容限,該標準描述了在 SDH 網絡內對抖動和漂移的控制。

當輸出相位被擾動時,將相位誤差的幅度和速率保持在標準組織所建議的極限之內,可確保在端到端系統中對信號惡化進行妥善處理,從而避免數據損壞或丟失。例如,當系統同步器進行參考時鐘切換時,如果輸出相位誤差位于規范要求之內,同步器就可實現“無間斷”參考時鐘切換,指示存在緩沖器溢出或欠載,造成指針移動、位調整或滑動。

結論

網絡同步和時鐘產生是所有高速傳輸網絡系統中最重要的部分。本文論述了時鐘惡化的不同類型,主要是抖動和漂移。文章還詳細論述了造成上述惡化的原因,以及它們如何影響傳輸系統。對時鐘子系統進行系統性設計和實現,將提高整個系統的性能,降低誤碼率,易于集成,提供更高的傳輸質量和效率。

摘要:

網絡同步和時鐘產生是高速傳輸系統設計的重要方面。為了通過降低發射和接收錯誤來提高網絡效率,必須使系統的各個階段都要使用的時鐘的質量保持特定的等級。網絡標準定義同步網絡的體系結構及其在標準接口上的預期性能,以保證傳輸質量和傳輸設備的無縫集成。有大量的同步問題,系統設計人員在建立系統體系結構時必須十分清楚。本文論述了時鐘惡化的各種來源,如抖動和漂移。本文還討論了傳輸系統中時鐘惡化的原因和影響,并分析了標準要求,提出了各種實現技巧。

基本概念:抖動和漂移

抖動的一般定義可以是“一個事件對其理想出現的短暫偏離”。在數字傳輸系統中,抖動被定義為數字信號的重要時刻在時間上偏離其理想位置的短暫變動。重要時刻可以是一個周期為 T1 的位流的最佳采樣時刻。雖然希望各個位在 T 的整數倍位置出現,但實際上會有所不同。這種脈沖位置調制被認為是一種抖動。這也被稱為數字信號的相位噪聲。在下圖中,實際信號邊沿在理想信號邊沿附近作周期性移動,演示了周期性抖動的概念。

圖 1.抖動示意

抖動,不同于相位噪聲,它以單位間隔 (UI) 為單位來表示。一個單位間隔相當于一個信號周期 (T),等于 360 度。假設事件為 E,第 n 次出現表示為 tE[n] 。則瞬時抖動可以表示為:

一組包括 N 個抖動測量的峰到峰抖動值使用最小和最大瞬時抖動測量計算如下:

漂移是低頻抖動。兩者之間的典型劃分點為 10 Hz。抖動和漂移所導致的影響會顯現在傳輸系統的不同但特定的區域。

抖動類型

根據產生原因,抖動可分成兩種主要類型:隨機抖動和確定性抖動。隨機抖動,正如其名,是不可預測的,由隨機的噪聲影響如熱噪聲等引起。隨機抖動通常發生在數字信號的邊沿轉換期間,造成隨機的區間交叉。毫無疑問,隨機抖動具有高斯概率密度函數 (PDF),由其均值 (μ) 和均方根值 (rms) (σ) 決定。由于高斯函數的尾在均值的兩側無限延伸,瞬時抖動和峰到峰抖動可以是無限值。因此隨機抖動通常采用其均方根值來表示和測量。

圖 2.以高斯概率密度函數表示的隨機抖動

對抖動余量來講,峰到峰抖動比均方根抖動更為有用,因此需要把隨機抖動的均方根值轉換成峰到峰值。為將均方根抖動轉換成峰到峰抖動,定義了隨機抖動高斯函數的任意極限 (arbitrary limit)。誤碼率 (BER) 是這種轉換中的一個有用參數,其假設高斯函數中的瞬時抖動一旦落在其強制極限之外即出現誤碼。通過下面兩個公式,就可以得到均方根抖動到峰到峰抖動的換算。3

由公式可得到下表,表中峰到峰抖動對應不同的 BER 值。

確定性抖動是有界的,因此可以預測,且具有確定的幅度極限。考慮集成電路 (IC) 系統,有大量的工藝、器件和系統級因素將會影響確定性抖動。占空比失真 (DCD) 和脈沖寬度失真 (PWD) 會造成數字信號的失真,使過零區間偏離理想位置,向上或向下移動。這些失真通常是由信號的上升沿和下降沿之間時序不同而造成。如果非平衡系統中存在地電位漂移、差分輸入之間存在電壓偏移、信號的上升和下降時間出現變化等,也可能造成這種失真。

圖 3,總抖動的雙模表示

數據相關抖動 (DDJ) 和符號間干擾 (ISI) 致使信號具有不同的過零區間電平,導致每種唯一的位型出現不同的信號轉換。這也稱為模式相關抖動 (PDJ)。信號路徑的低頻截止點和高頻帶寬將影響 DDJ。當信號路徑的帶寬可與信號的帶寬進行比較時,位就會延伸到相鄰位時間內,造成符號間干擾 (ISI)。低頻截止點會使低頻器件的信號出現失真,而系統的高頻帶寬限制將使高頻器件性能下降。7

正弦抖動以正弦模式調制信號邊沿。這可能是由于供給整個系統的電源或者甚至系統中的其他振蕩造成。接地反彈和其他電源變動也可能造成正弦抖動。正弦抖動廣泛用于抖動環境的測試和仿真。不相關抖動可能由電源噪聲或串擾和其他電磁干擾造成。

考慮抖動對數字信號的影響時,需要將整個確定性抖動和隨機抖動考慮在內。確定性抖動和隨機抖動的總計結果將產生另外一種概率分布4:雙模響應,其中部表示確定性抖動,尾部為高斯響應,表示隨機抖動分量。

抖動測量 — TIE、MITE 和 TEDV

時間間隔誤差 (TIE) 是通過對實際時鐘間隔的測量和對理想參考時鐘同一間隔的測量得到的。在給定時間 t,以一個稱為觀測間隔的時間間隔產生時間 T(t) 的時鐘,其相對于時鐘 Tref(t) 的TIE 可通過下面公式表示。(x(t) 稱為誤差函數。)

TIE 表示信號中的高頻相位噪聲,提供了實際時鐘的每個周期偏離理想情況的直接信息。TIE 用于計算大量統計派生函數如 MTIE、TDEV 等。

最大時間間隔誤差 (MTIE) 定義為,在一個觀測時間 (t=nt0) 內,一個給定時鐘信號相對于一個理想時鐘信號的最大峰到峰延遲變化,其中該長度的所有觀測時間均在測量周期 (T) 之內。使用下面公式進行估計:

MTIE是針對時間的緩變或漂移而定義的。當需要分析時鐘的長期特性時,就需要對MTIE進行測量。MTIE 值是對一個時鐘信號的長期穩定性的一種衡量。

圖 4.TIE 的圖形表示

TDEV 是另外一個統計參數,作為集成時間的函數對一個信號的預期時間變化的測量。DEV 也能提供有關信號相位(時間)噪聲頻譜分量的信息。TIE 圖中每個點的標準偏差是對一個觀測間隔計算的,該觀測間隔滑過整個測量時間。該值在整個上述測量時間內進行平均以得到該特定間隔的 TDEV 值。增大觀測間隔,重復測量過程。TDEV 是對短期穩定性的一種衡量,在評估時鐘振蕩器性能時有用。TDEV 屬于時間單位。

高速傳輸系統中抖動和漂移的原因

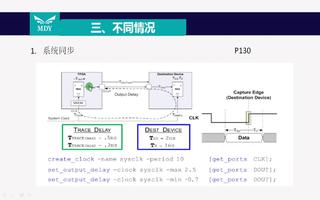

最常用的一種時鐘體系結構是,在備板上運行一個低頻時鐘,在每個傳輸卡上產生同步的高頻時鐘。低頻時鐘在集成電路內或通過分立 PLL 實現進行倍頻以產生高頻時鐘。通過典型的 PLL 倍頻,倍頻后時鐘上的相位噪聲增大為原來時鐘相位噪聲的 20*log(N) 次方,其中 N 為倍頻系數。此外,PLL 參考時鐘輸入上的抖動將延長鎖定時間,且當輸入抖動過大時高速 PLL 甚至無法實現鎖定。在備板上采用一種更高速的差分時鐘將比采用低速單端時鐘具有更好的抖動性能。

由于 VCO 對輸入電壓變化較為敏感,因此電源噪聲是增大時鐘抖動的一個主要因素。輸出時鐘抖動幅度與電源噪聲幅度、VCO 增益成正比,與噪聲頻率成反比。因導線電阻形成的電阻下降和因導線電感形成的電感噪聲而造成的電源或接地反彈,會對上述輸出時鐘抖動產生相似的影響。在系統板上對電源進行充分過濾,靠近集成電路電源引腳提供去耦電容,可以確保 PLL 獲得更高的抖動性能。

在系統板內,時鐘和數據相互獨立,發射和接收端在啟動、保持和延遲時間方面的變化對高速率非常關鍵。因數據和時鐘路徑中存在不同有源元件而使數據和時鐘路徑之間出現傳播延遲差異, 時鐘路徑之間的接線延遲差異,數據位之間的接線延遲差異,數據和時鐘路徑之間不同的負載情況,分組長度差異等等,均可能造成上述變化。在規劃系統抖動余量時,必須將不同信號路徑的變化考慮在內。

當在一段距離上進行傳輸時,在發射機和接收機中的很多點上存在抖動累積。在發射機物理層實現中,DAC 非線性或激光非線性等非線性特性會加重信號失真。在傳輸介質和接收機中,除了外部亂真源(大多在銅導線中)之外,因不同頻率和調制效應而導致的光纖失真、因接收機實現(主要與帶寬有關)和時鐘提取電路實現而導致的信號相關相位偏離,會加重信號流的抖動。

圖 5.來自 TIE 圖的 MTIE 偏差

具體到 SDH(同步數字系列)傳輸,有大量的系統級事件會導致抖動。在將 PDH(準同步數字系列)支路映射為 SDH 幀并通過 SDH NE(網絡組件)進行傳輸的典型傳輸系統中,在 PDH 支路于 SDH 的終端多路分配器解映射之前,將在每個中間節點處出現 VC(虛擬容器)的重新同步。有間隙的時鐘用于將各個支路映射到 STM-N 幀和從 STM-N 幀解映射,發出與開銷、固定填充和調整位相應的脈沖,因而造成映射抖動。采用調整機會位補償 PDF 支路中頻率偏移的方法會造成等待時間抖動。還有指針調整機制,用于對來自初始 NE 的輸入 VC 與本地產生的輸出 STM-N 幀之間的相位波動進行補償。根據頻率偏離,VC 在 STM-N 幀中前后移動。這將使 VC 提取點看到位流中的突然變化,導致稱為指針抖動的類型抖動。所有上述系統級抖動都將加重總的確定性抖動。

盡管所有上述因素都會加重從源到目的地之間信號傳播的抖動,標準要求仍然規定在傳輸點需具有比理論值更低的抖動數值。這樣,考慮到時鐘倍頻、電源變化、電-光-電轉換、發射和接收影響以及其他致使實際信號惡化的失真信號的影響,在源處驅動信號的時鐘將具有一個相對很低的抖動數值。

抖動對收發器的影響

理想情況下,數字信號是在兩個相鄰電平轉換點的中點進行采樣的。抖動之所以會造成誤碼,是由于相對于理想中點,它改變了信號的邊沿轉換點。誤碼可能由于信號流邊沿變化太晚(在時間上比理想中點晚0.5UI(單位間隔相當于信號的一個周期))或太早(在時間上比理想中點早0.5UI)所致。當時鐘采樣邊沿在信號流的任何一側錯過0.5UI 時,將出現 50% 的誤碼概率,假設平均轉換密度為 0.5。7如果分別知道確定性抖動和隨機抖動,可通過上述兩個數字和將峰到峰抖動值與均方根抖動值聯系在一起的表,來估計誤碼率。校準抖動,定義為數字信號的最佳采樣時刻與從其提取出來的采樣時鐘之間的短期變化,可以造成上述誤碼。對于商業應用,源時鐘和源發射接口抖動規范將遠遠低于 1UI。

發射接口抖動規范通常與接收端的輸入抖動容限相匹配。對于抖動測量回路濾波器截止頻率,尤其如此。例如,在 SDH 系統中,有兩種抖動測量帶寬,分別規定:一個用于寬帶測量濾波器(f1 到 f4),一個用于高頻帶測量濾波器(f3 到 f4)。數值 f1 指可在線路系統的 PLL 中使用的輸出時鐘信號的最窄時鐘截止頻率。低于此帶寬的頻率的抖動將通過系統,而較高頻率的抖動則被部分吸收。數值 f3 表示輸入時鐘捕獲電路的帶寬。高于此頻率的抖動將導致校準抖動。校準抖動造成光功率損失,需要額外光功率以防各種惡化。因此限制發射機端高頻帶頻譜的抖動十分重要。

漂移對收發器的影響

市場上銷售的大多數電信接收機都使用了一個緩沖器,以適應線路信號中存在的隨機波動。下面框圖6詳細表示出這一概念。恢復時鐘將數據送入富有彈性的緩沖器,而系統時鐘則將數據送出到設備的核心部位。

在準同步傳輸系統中,發射機和接收機工作在相互獨立而又極為接近的頻率上,fL和 Fs分別表示發射機和接收機的頻率。當兩者之間存在相位或頻率差異時,彈性存儲會將其消除,否則緩沖器將出現欠載或溢出(取決于差異的幅度和彈性緩沖器的大小),造成一次可控的幀滑動(基本速率傳輸)或一次位調整(高階異步多路復用器)。

在準同步應用中,根據可接受的緩沖滑動對頻率變化和緩沖器深度進行了標準化。最初的網絡主要用于語音傳輸,在一定的頻率門限之下不會造成語音質量下降。ITU-T 規范規定該變化為 +/-50ppm。但是隨著網絡開始傳送壓縮語音、傳真格式的數據、視頻以及其他種類的媒體應用,對于差錯和重傳以及剛剛興起的同步網絡,滑動使效率嚴重下降。

在同步傳輸系統中,系統時鐘通常同步到用于接收更高時鐘等級信號的接口的恢復時鐘上。恢復時鐘和系統時鐘之間相位和頻率的瞬時和累積差異將被彈性緩沖器吸收,否則將導致彈性存儲器溢出/欠載(取決于緩沖器大小和變化的幅度),造成指針調整而延遲或提前幀傳輸、幀滑動或系統中某處出現位調整。

在同步系統中,所有網絡組件工作在同一平均頻率,可以通過指針機制消除幀惡化。這些指針機制將提前或延遲有效載荷在傳輸幀中的位置,從而調整接收和系統時鐘中存在的頻率和相位變化。SDH 收發器中的緩沖器比 PDH 收發器中的要小,而且對于 SDH 系統中可能導致的指針移動等不規則性有限制。因此,與 PDH 系統相比,同步系統的要求更為嚴格。由于網絡發展的歷史和不同網絡之間的互操作連接,在某些階段或其他階段,這些同步網絡會通過準同步網絡來連接。因此 PDH 網絡的時鐘體系結構也要考慮在內。

MTIE 提供了時鐘相對于已知理想參考時鐘的峰值時間變化。在同步傳輸和交換設備的彈性緩沖器的設計中將用到 MTIE 值。在彈性存儲中,緩沖器填充水平與輸入數字信號和本地系統時鐘之間的 TIE 成正比。確保時鐘符合有關 MTIE 的時鐘規范,將保證不會超過一定的緩沖器門限。因此,在緩沖器設計中,其大小取決于 MTIE 的規定極限。

圖6,典型傳輸系統的接收機接口

系統時鐘輸出相位擾動對收發器的影響

一個時鐘的輸出相位變化可以通過分析其 MTIE 信息獲得。漂移產生(在自由振蕩模式和同步模式中)主要指系統中所用時鐘振蕩器的長期穩定性,在自由振蕩模式中系統的穩定性僅受振蕩器的穩定性影響。除了漂移產生之外,輸出時鐘相位還受到大量系統不規則特性的影響。

特別是對一個系統同步器而言,將參考源從一個不良或惡化參考時鐘轉換到一個正常參考時鐘可能會導致輸出相位擾動。傳輸用高速 PLL 中使用的傳統 VCO(壓控振蕩器)在改變參考時鐘時采用了切換電容器組的方法。這種切換轉換會對輸出時鐘造成暫時的相位偏移。采用超低抖動時鐘倍頻器電路可以解決這個問題。

高性能網絡時鐘在系統的所有參考時鐘都失去時采用一種稱為“保持”的機制。這是通過記憶存儲技術產生系統最后一個已知良好參考時鐘來實現的。進入和退出保持模式可能會對輸出造成相位擾動。當處于保持模式中時,由于準確頻率的再生不夠精確,因此會繼續產生輸出相位誤差。集成電路技術的進步已使保持精度達到了 0.01ppb。輸入參考時鐘惡化和對系統的維護測試(不會導致參考時鐘切換)過少,也會造成輸出相位擾動。

系統輸出擾動是有限的,取決于系統在較低層次可以接受的輸入容限。例如,符合 G.813 選項 1 的時鐘,其相位擾動中所允許的相位斜率和最大相位誤差被限制為 1μS,最大相位斜率為 7.5ppm,兩個 120ns 相位誤差段,其余部分的相位斜率為 0.05ppm。這些數字對應于 G.825 標準規定的輸入抖動容限,該標準描述了在 SDH 網絡內對抖動和漂移的控制。

當輸出相位被擾動時,將相位誤差的幅度和速率保持在標準組織所建議的極限之內,可確保在端到端系統中對信號惡化進行妥善處理,從而避免數據損壞或丟失。例如,當系統同步器進行參考時鐘切換時,如果輸出相位誤差位于規范要求之內,同步器就可實現“無間斷”參考時鐘切換,指示存在緩沖器溢出或欠載,造成指針移動、位調整或滑動。

結論

網絡同步和時鐘產生是所有高速傳輸網絡系統中最重要的部分。本文論述了時鐘惡化的不同類型,主要是抖動和漂移。文章還詳細論述了造成上述惡化的原因,以及它們如何影響傳輸系統。對時鐘子系統進行系統性設計和實現,將提高整個系統的性能,降低誤碼率,易于集成,提供更高的傳輸質量和效率。

電子發燒友App

電子發燒友App

評論