摘要

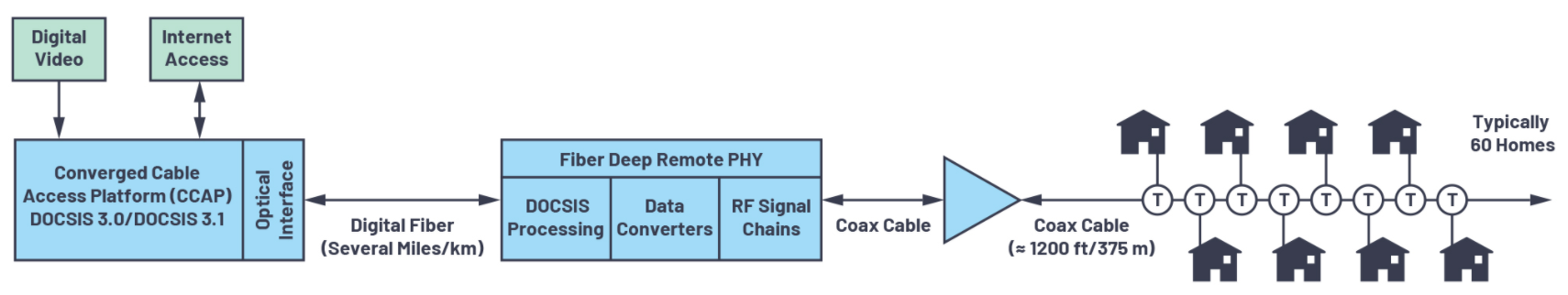

針對用戶需要更快互聯網連接的趨勢,有線電視行業已開發新的網絡架構,以便為用戶提供數Gb服務。該光纖深入方法采用遠程PHY設備(RPD),通過使用數字光纖將關鍵硬件移到更靠近用戶的位置。這可與無線(蜂窩)網絡中的遠程射頻頭相媲美,可節約空間,減少前端散熱,但也為遠程設備帶來了新的設計挑戰。

雖然有線電視信號絕對頻率較低,但其帶寬比無線信號寬得多,從108 MHz到1218 MHz擴展了幾個倍頻程,并具有多個帶內諧波。RPD讓設計人員面臨諸多挑戰,包括RF和混合信號硬件必須涵蓋更寬的頻率范圍,具有更高的RF功率、更低的底噪和更好的線性度,同時消耗更少的直流功耗。每個下行末級RF放大器的功率通常為18 W,對于4端口系統,這大約是通常能夠提供給RPD(由RPD消耗)的140 W至160 W功率預算的50%。

將ADI的有線電視數字預失真(DPD)效率增強技術,應用于DPD優化功率倍增器(ADCA3992),并結合先進的高速數據轉換器技術,利用單個DAC(例如AD9162)和單個ADC(如AD9208), 以及高度集成的時鐘解決方案(HMC7044),來實現全頻帶DPD。

本文介紹遠程PHY的演進,以及ADI公司如何使用專有DPD并將ADI的算法和IP內核集成到OEM的現有FPGA部署中來解決效率和線性度挑戰。

背景知識

自從60多年前作為社區接入電視(CATV)引入,有線電視已從簡單的單向(僅下行)模擬鏈路發展為復雜的多模、多頻道雙向系統(包括上行或反向路徑),支持模擬電視、基于IP的標清(SD)和高清(HD)數字電視以及高速數據互聯網下載和上傳。這些服務由多個系統運營商(MSO)提供。

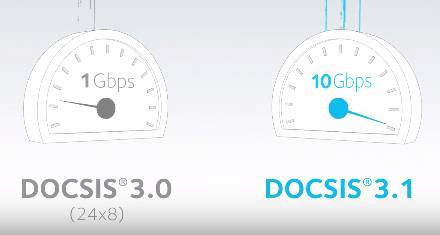

有線數據和數字電視服務把使用CableLabs及相關參與公司制定的有線電纜數據系統接口規范(DOCSIS)的數據提供給消費者。前端系統(電纜調制解調器終端系統或CMTS)的配置經過了多次演進,包括添加EdgeQAM調制器作為獨立單元,或與CMTS集成為有線電視融合接入技術平臺(CCAP)的一部分。對下行數據容量的需求現在正以約50%的復合年增長率(CAGR)增加,這意味著需求約每21個月翻一番。1為了滿足這種需求,自從1997年發布DOCSIS 1.0以來,下行數據速率已從40 Mbps增加到1.2 Gbps(通過廣泛部署實施DOCSIS 3.0)。

這些下行數據速率的提高通過結合使用多項技術來實現,包括頻道綁定、更復雜的調制(從64 QAM移至256 QAM)和更高的下行頻率上限(從550 MHz至750 MHz至1002 MHz)。在美國,所有這些都是在保留傳統模擬電視服務6 MHz頻道規劃的情況下實現的(EuroDOCSIS和C-DOCSIS為8 MHz),但為了支持高達10 Gbps的下行速率,有必要做出更根本的改變,于是在2013年,發布了DOCSIS 3.1標準。在保留對傳統標準支持的同時,DOCSIS 3.1采用頻譜效率更高的正交頻分多路復用(OFDM)技術,頻道帶寬高達190 MHz,支持高達4096 QAM。此外,下行頻率范圍的頻率上限增加了超過20%,達到1218 MHz,并可選擇擴展到1794 MHz。

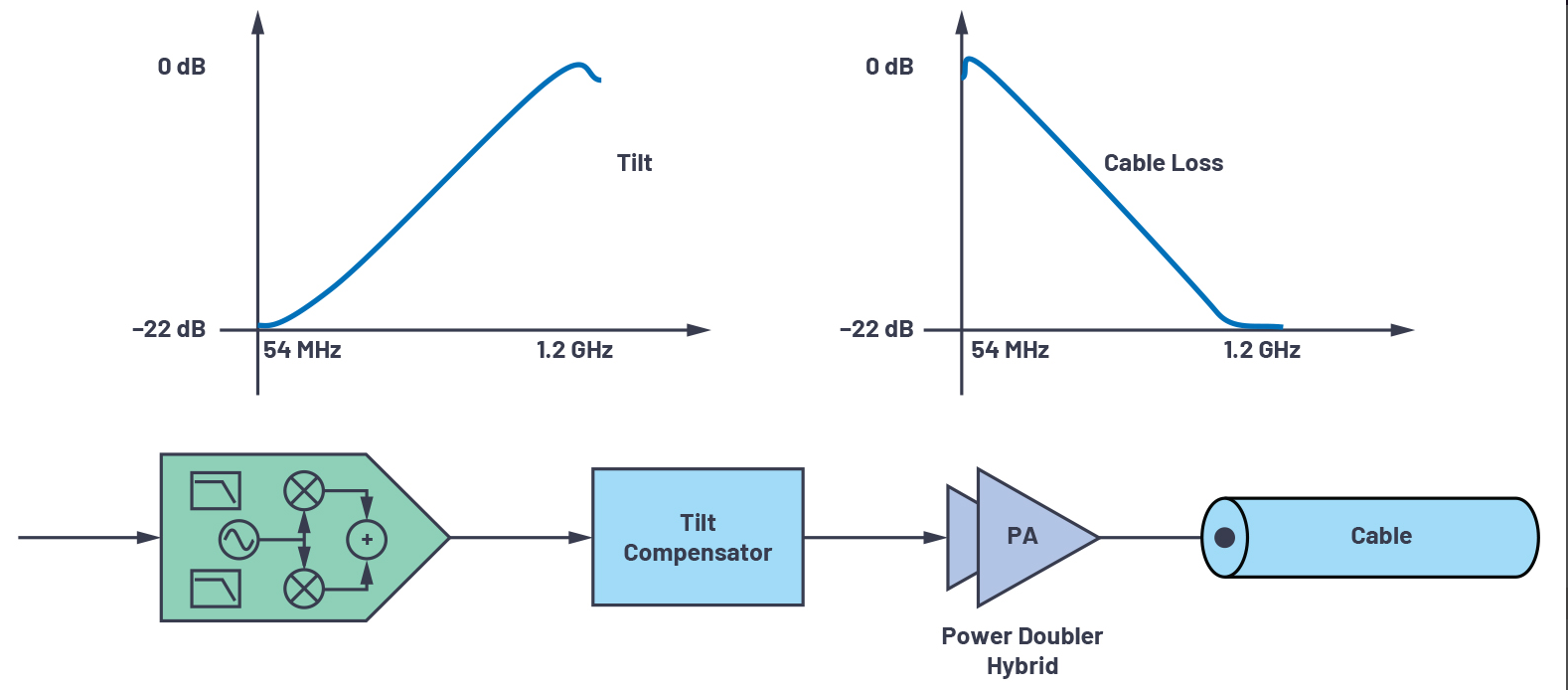

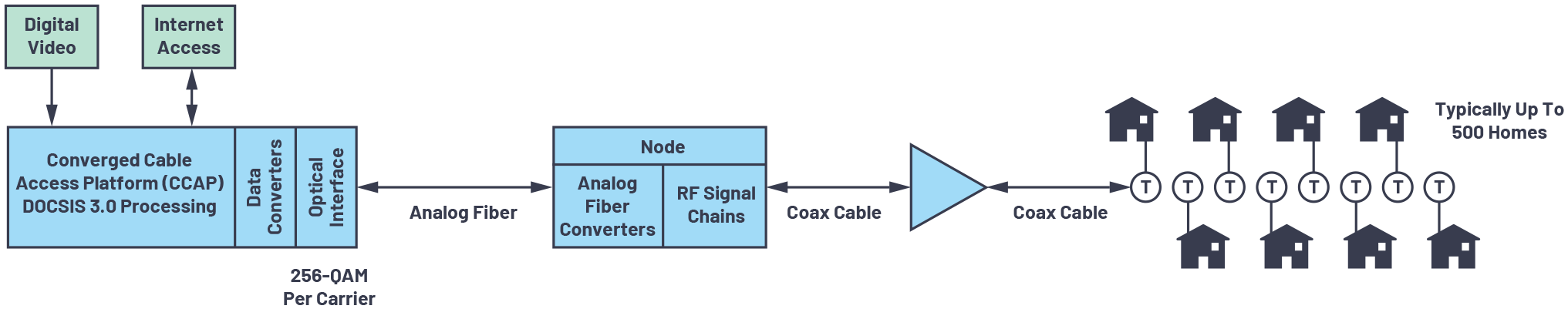

但有一點始終沒有改變,都是使用具有75 Ω阻抗的同軸電纜物理連接到用戶電纜調制解調器。在20世紀90年代之前,系統前端和用戶之間使用100%同軸電纜,但最新部署為混合光纖銅纜(HFC)。在HFC中,模擬電光轉換器連接到前端的同軸輸出;然后信號通過光纖傳輸至靠近服務區的節點,再通過光電轉換器,最終經同軸電纜分配給用戶。通過架空或地下電纜與用戶的這最后一英里連接成為系統瓶頸,但升級到光纖到戶(FTTH)鏈路的成本很高且具有破壞性,因此有線電視MSO決定充分利用現有的同軸電纜資產。與雙絞線電話線相比,同軸電纜提供了一個相對良好的環境,本身能夠屏蔽干擾或串擾,并且因阻抗不匹配產生適度的信號反射。但是,從節點到最遠用戶達1200英尺的典型距離下,頻率相關損耗特征明顯(108 MHz和1002 MHz之間存在近17 dB的斜率),需要插入具有高通響應的RF濾波器進行預加重或傾斜。

在典型的HFC部署中(如圖1所示),從光纖節點連接的一根主干同軸電纜可服務數百個用戶,通過多路RF分路器將信號分配給子組,然后通過分接頭將分接電纜連接到個人用戶。在典型的節點+ n系統中,寬帶升壓放大器以固定的間隔插入網絡中,以放大信號電平,確保電纜調制解調器處具有足夠的信噪比(SNR)。

為用戶提供更大的數據容量

DOCSIS干線電纜上的可用數據帶寬由所有連接用戶共享,并可通過兩種方式為所有用戶提供更多帶寬:

? 提高通過電纜傳輸的數據速率

? 減少連接到電纜的用戶數量

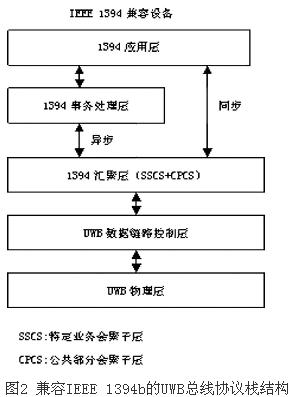

如前所示,通過使用頻道綁定、更高階的調制方案以及擴展頻譜以提供更多的頻道,可提高關鍵信息(headline)數據速率。但是,增加下行容量只是解決方案的一部分,因此,網絡架構也在不斷發展以減少連接到節點的用戶數量,最初是通過節點分割來實現的,將支持的用戶數量從最多2000減少到不足500。這種方法有效但成本很高。節點分割的替代方法是修改網絡架構,通過使用帶數字光纖鏈路的分布式接入架構(DAA)將物理層(PHY)與CCAP分離,如圖2所示。遠程PHY硬件包含下行調制和RF級以及上行RF級和解調。從CCAP中移除體積龐大且耗電的PHY組件,在前端位置放一個邊緣路由器也能實現虛擬CCAP。

數字光纖的性能遠遠高于模擬光纖,且覆蓋范圍更大(能夠更靈活地確定節點位置),并且單根光纖支持大約5倍的波長。DAA方法還消除了傳統HFC網絡中的電光和光電轉換。這些轉換限制了光節點輸出信號的動態范圍:模擬轉換的底噪和線性度都會影響調制誤差率(MER),這將決定是否能夠支持高數據速率所需的高階調制。

挑戰是什么?

光纖深入架構將通過更小的服務組規模、更自由的頻譜分配和更好的線路末端SNR和MER(DOCSIS 3.1中實現高階調制所必需的),來提升每個用戶的容量。由于數字光纖和新硬件的位置相對靠近用戶,因此還有機會提供補充服務節點,如在遠程PHY節點上添加Wi-Fi接入點。但是,這也會給下行模擬傳輸鏈帶來幾個新的設計挑戰。

圖1.使用HFC部署有線電視

圖2.使用遠程PHY部署有線電視

DOCSIS 3.1標準將下行頻率上限從1002 MHz擴展到1218 MHz,意味著必須傳輸相當于35個額外的6 MHz頻率通道,且向上傾斜度從17 dB增加到21 dB,如圖3所示。

任何新系統都需要與現有部署保持兼容,因此最高DOCSIS 3.0頻道中的功率(以999 MHz為中心)必須保持不變(通常為57 dBmV),這意味著最高頻道(以1215 MHz為中心)中所需的RF功率為61 dBmV。由于添加了頻道,增加了傾斜度,并且電纜調制解調器需要高SNR,因此節點輸出端口前的最后一個有源元件,即A類超線性功率放大器(功率倍增器混合)所需的輸出信號電平提高了一倍多,達到76.8 dBmV的復合電平。為了滿足不斷增長的RF功率需求,混合硬件設計人員必須將每端口混合直流偏置功率從10 W左右增加到18 W,并且在某些情況下,必須將直流電源電壓從行業標準值24 V增加到34 V。由于節點通常支持多達4個RF端口,每個端口都有其自己的混合端口,并且通常由通過同軸電纜注入的60 V交流電源供電,這就迫使對設計做出重大更改,并產生了新的散熱管理問題。

為了支持采用DOCSIS 3.1的更高階QAM方案,節點輸出端對MER的苛刻要求已從43 dB增加到48 dB。2在這樣高的MER要求下,DAC時鐘上的相位噪聲和雜散信號會對系統性能產生影響。功率倍增器直接影響MER和帶內帶外失真的主要不利因素是非線性失真,包含諧波和交調失真。在108 MHz至1218 MHz的倍頻程工作范圍內,存在多個帶內奇偶次諧波,而在185個D3.0載波(或等效載波)下,會產生一組非常復雜的IM產物。傾斜也有顯著的影響,因為較高頻道中的功率比最低頻道中的功率大100多倍,所以這里會產生顯著的差頻積。峰均功率比(PAPR)超過12 dB。

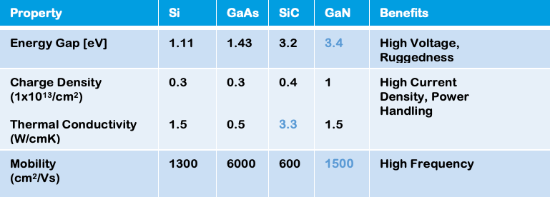

所有這些因素結合起來,為功率倍增器設計人員帶來了巨大的挑戰:更寬的帶寬、更高的峰均功率以及改善線性度。最新的A類GaAs/GaN推挽混合器件(如ADCA3992)可滿足帶寬、RF功率和線性度要求,但RF系統設計人員所面臨的挑戰無疑是降低功耗:650 mW的RF輸出功率的直流輸入約為18 W時(等效于76.8 dBmV復合電平),直流到RF的轉換效率僅為3.6%。

系統解決方案是什么?

一旦混合設備能夠支持所需的帶寬和功率,解決方案的第一部分就是確保輸出端口前的最后一個有源元件,即混合功率倍增器能夠獲得清晰的信號。通過使用高性能寬帶16位RF DAC(如AD9162)和低相位噪聲、低雜散輻射JESD204B兼容時鐘源(如HMC7044),可在DAC輸出端跨整個DOCSIS 3.1頻率范圍實現約52 dB MER。

解決方案的第二部分更復雜。理想情況下,任何解決方案都會既提高功率倍增器的輸出功率能力又提高MER,同時降低功耗,但它們幾乎是相互對立的:在恒定輸出功率下,降低功耗會使MER性能下降,或者需要損失RF功率性能,才能使MER保持不變。雖然可以使用包絡跟蹤(ET)等技術來提高效率,但創建非常寬的帶寬包絡信號并將ET過程產生的顯著失真線性化將帶來額外的挑戰。

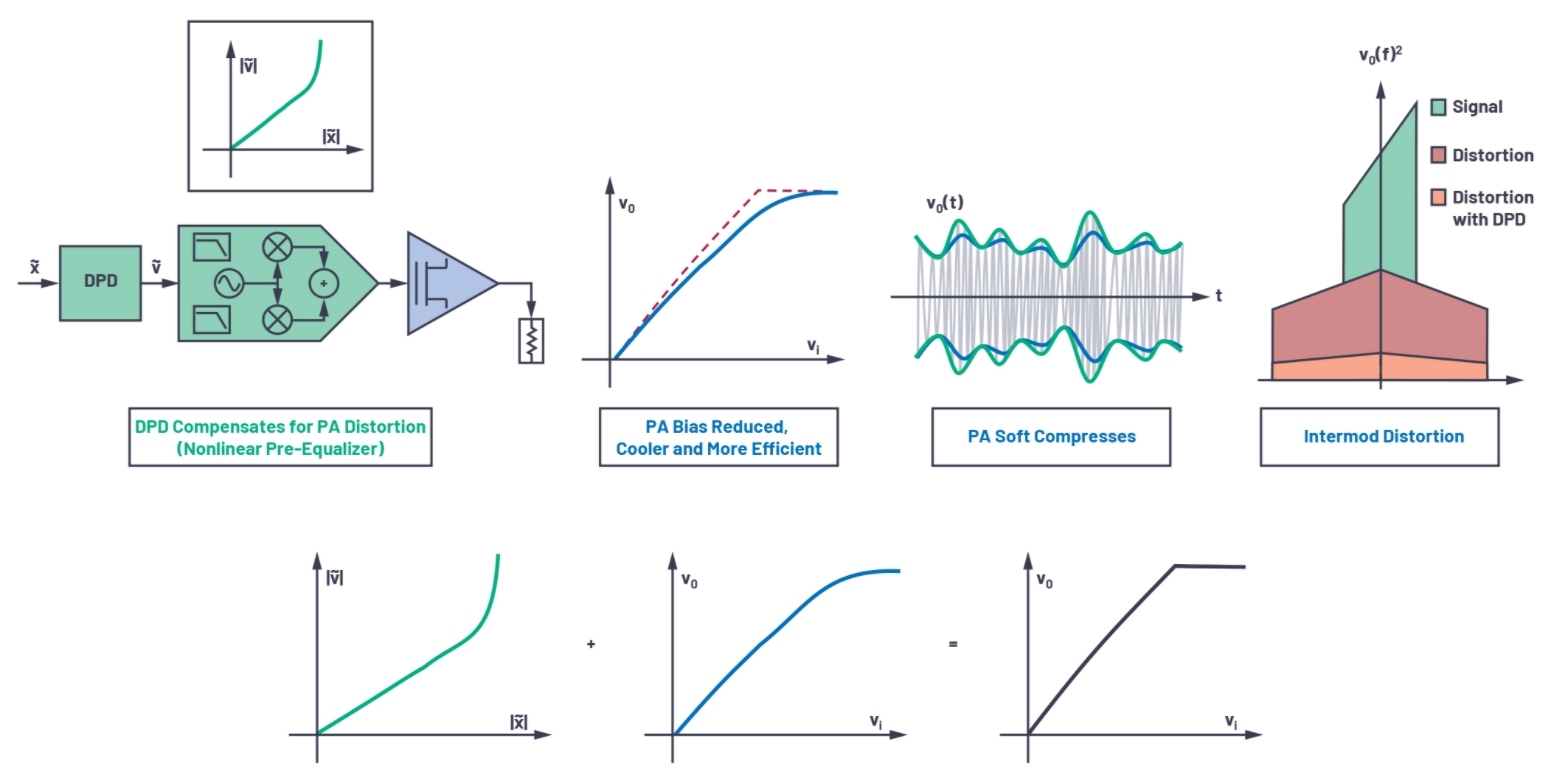

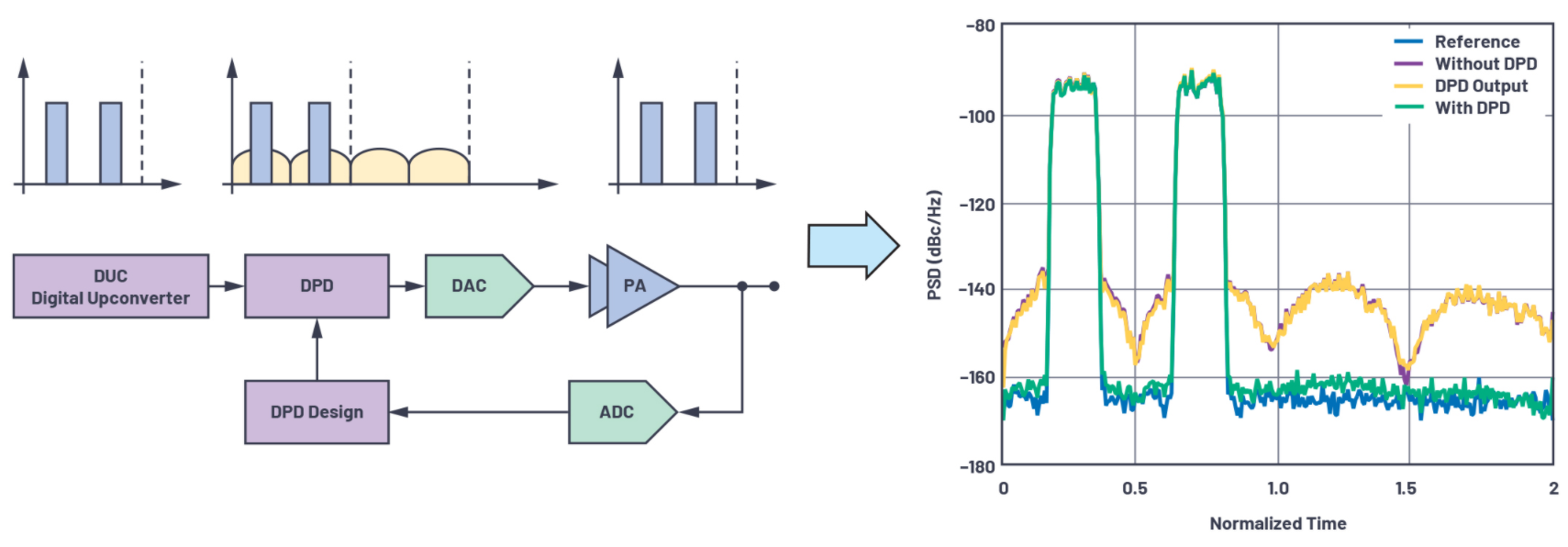

要兼顧效率和MER,具有吸引力的解決方案就是DPD,整個無線蜂窩行業幾乎普遍采用。數字預失真(DPD)允許用戶在更高效但非線性更明顯的區域中運行混合功率倍增器,然后先預先校正數字域中的失真,再將數據發送到放大器。如圖4所示,DPD在數據到達放大器之前對其進行整形,以抵消放大器產生的失真,從而擴大功率倍增器的線性范圍。

圖3.頻率相關電纜損耗的傾斜補償

圖4.數字預失真

在擴大的線性工作范圍中,DPD讓放大器能夠在降低的偏置電流或電源電壓下更自由地運行(從而降低功耗),或提高MER和誤碼率(BER),甚至可能同時兼顧。盡管數字預失真已廣泛應用于無線蜂窩基礎設施,但在電纜環境中實施數字預失真有獨特而又有挑戰性的要求。這包括對超寬帶寬應用線性化,盡量減少實施DPD所需的數字信號處理功耗,以及在高傾斜頻譜下工作。所有這一切只能通過對硬件、FPGA和軟件進行適度的更改(會增加成本)來實現。

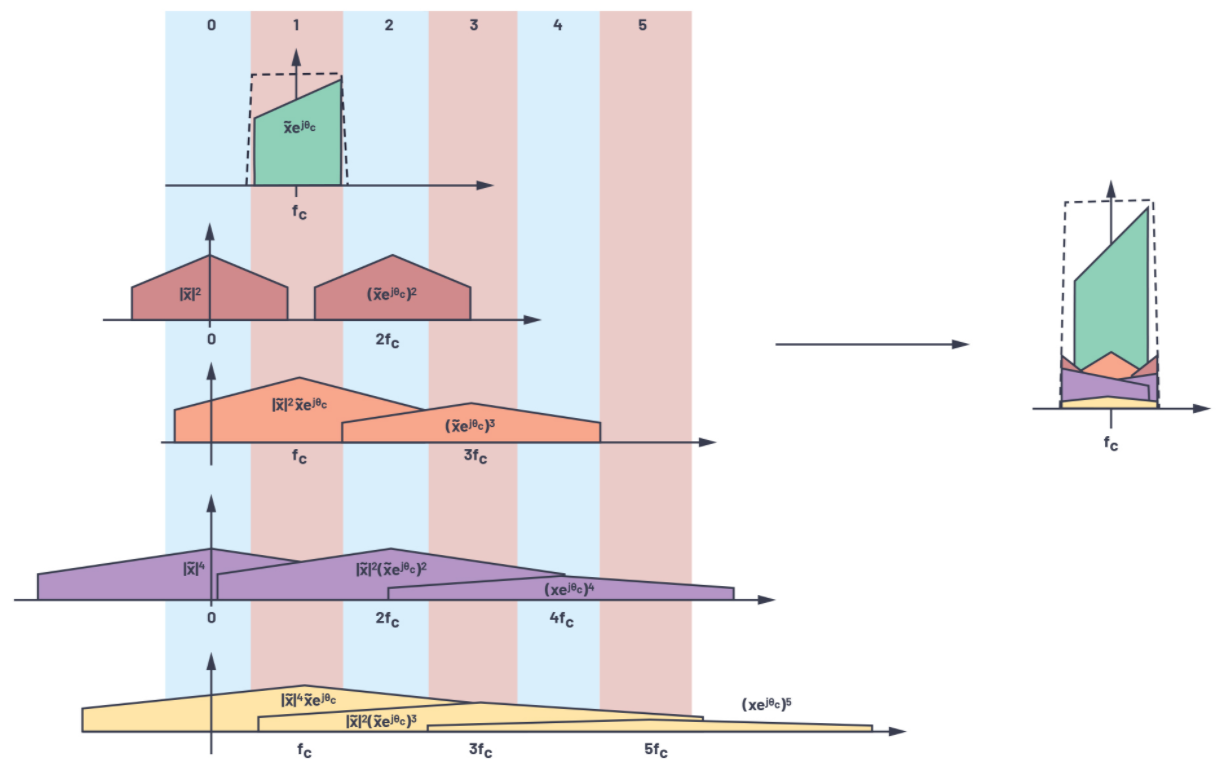

由于通過將放大器驅動到非線性工作區域來提高效率,多個帶內失真產物給DPD帶來了獨特的挑戰。不僅是大信號帶寬,還有它在頻譜(從直流開始僅為108 MHz)上的位置都對DPD構成了挑戰。有線信號的性質與無線截然不同,無線信號其所需信號的帶寬(例如,60 MHz)比RF中心頻率(例如,2140 MHz)小很多。在典型的108 MHz至1218 MHz DOCSIS 3.1下行分配中,所需信號帶寬為1110 MHz,中心頻率為663 MHz。所有非線性系統都會發生諧波失真。電纜數字預失真的重點是帶內諧波失真產物。在典型的無線系統中,三次和五次諧波最重要,因為其他產物在頻帶外,可通過傳統濾波器濾除。在典型的電纜部署中,最低載波的前11個諧波都在頻帶內。

相比只需要考慮奇數次諧波的無線蜂窩應用,電纜應用中的偶數次和奇數次諧波均在頻帶內,可產生多個重疊的失真區域。這在一定程度上會對任何數字預失真解決方案的復雜性和精密性產生嚴重影響,因為算法必須通過簡單的窄帶假設。數字預失真解決方案必須適應所有階次的諧波失真。每個階次k需要[k/2] + 1項(二階:k = 2 → 2項,三階:k = 3 → 2項,四階:k = 4 → 3項等)。在窄帶系統中,偶數階項可以被忽略,奇數階在每個目標頻帶內產生1個項。電纜應用中的數字預失真必須考慮奇數階和偶數階諧波失真,并且還必須考慮到每個階可能有多個重疊的帶內元素。

諧波失真校正定位

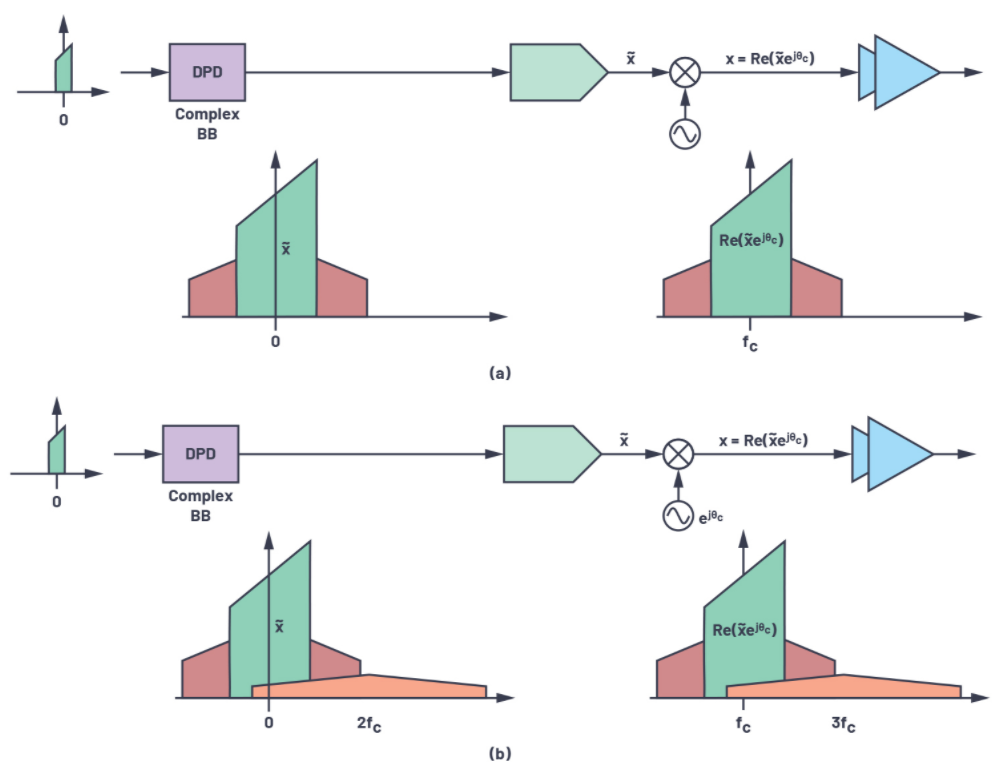

考慮到傳統窄帶數字預失真解決方案的處理在復雜的基帶處完成,我們主要關注對稱位于載波周圍的諧波失真。在寬帶電纜系統中,盡管保持了位于一次諧波周圍的那些項的對稱性,但是這一對稱性不再適用于更高階次的諧波產物。

圖5.寬帶電纜應用中寬帶諧波失真的影響

如圖6a所示,傳統窄帶數字預失真在復雜基帶處完成。在這些實例中,僅一次諧波產物在頻帶范圍內,因此其基帶產物直接轉換為RF。考慮寬帶電纜數字預失真時(圖6b),較高階次的諧波失真必須是頻率偏移,才能使上變頻后的基帶產物正確位于實際RF頻譜中。

圖7概要顯示了一種數字預失真的實現。在理想情況下,從數字上變頻器(DUC)(通過數字預失真)到DAC乃至通過功率倍增器的路徑將沒有帶寬限制。同樣地,觀測路徑上的ADC將對全帶寬進行數字化。請注意,為了進行說明,我們擴展2倍帶寬的信號路徑;在某些無線蜂窩應用中,可擴展到3至5倍的帶寬。理想方案是通過數字預失真產生帶內項和帶外項,從而完全消除功率放大器引入的失真。需要注意的是,為了準確消除失真,需要在目標信號的帶寬之外創建項,這一點非常重要。在實際方案中,信號路徑具有帶寬限制和傾斜特性,數字預失真性能無法達到理想方案要求。

ADI公司開發了一個完全實時、閉環、自適應電纜數字預失真解決方案,由FPGA結構中的執行器和嵌入式處理器中基于軟件的自適應機制組成。該實現方案使用Intel? Arria? 10 660 FPGA和嵌入式ARM? Cortex?處理器。DPD IP內核和ARM的功耗為5.3 W,盡管使用更新一代的FPGA或轉換為ASIC,此功率仍應低于3 W。

圖6.寬帶數字預失真復雜基帶處理中的頻率偏移要求。(a) 傳統窄帶數字預失真在復雜基帶處完成

(b) 寬帶電纜數字預失真、OOB HD必須是頻率偏移以允許RF上變頻

圖7.無帶寬限制的理想化數字預失真方案

結果

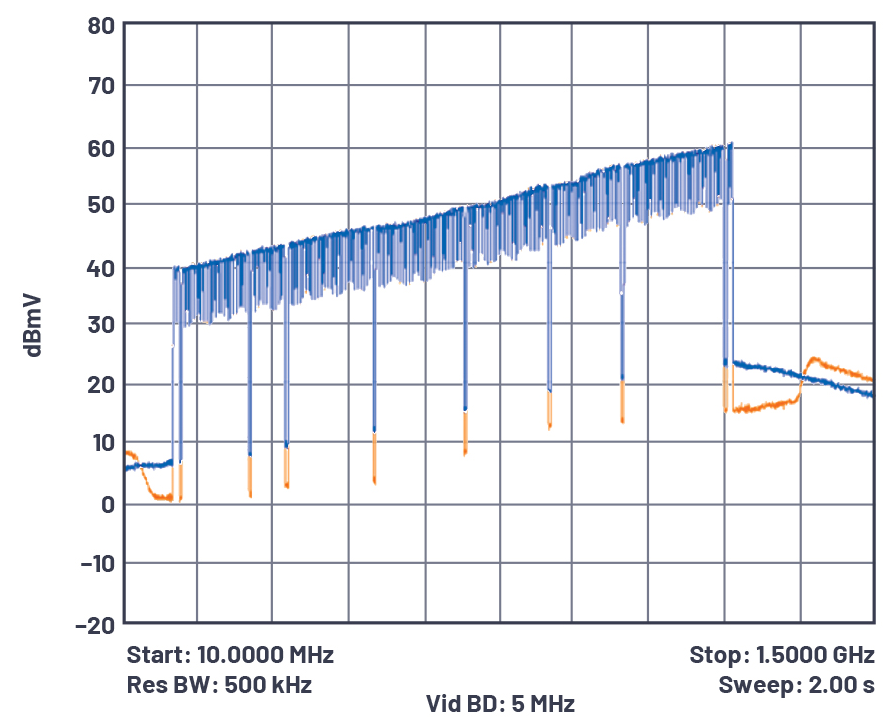

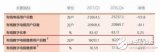

圖8顯示ADCA3992在76.8 dBmV總復合電源、34 V電源電壓、400 mA偏置電流(13.6 W直流電源)下工作的測試結果。

圖8.ADCA3992在76.8 dBmV下沒有數字預失真(藍色)和有數字預失真(橙色)時的性能

測試信號是一串DOCSIS 3.0載波,中心頻率為111 MHz至1215 MHz,傾斜度為21 dB。引入了少量的間隙,以便觀察頻帶失真。可以看到,頻帶底部失真約改善了6 dB,頻帶頂部超過8 dB。

與530 mA標稱非數字預失真功率倍增器電流相比,直流電源節省4.4 W,那么,4端口系統節省的總功率為17.6 W減5.3 W FPGA電源,得到12.3 W。對于72 W至59.7 W的4端口系統,功耗(散熱)顯著降低。每個倍增器的偏置電流很可能進一步回退至350 mA (11.9 W),同時仍達到41 dB的MER目標值,從而系統凈節省19.2 W。

結論

盡管高速移動數據和光纖日益得到廣泛應用,但現有最后一英里網絡的巨大覆蓋范圍及其相對良好的電氣特性,可確保在可預見的未來,它們仍將是向消費者提供語音、視頻和數據服務的重要工具。隨著有線電視網絡過渡到DOCSIS 3.1,并且不斷地發展,滿足更寬的頻率范圍、更高的功率、更好的調制精度以及更高的功效等系統性能要求變得更加困難。

數字預失真提供了一種可解決這些相互沖突需求的方式,但在電纜應用中的實施也構成了非常獨特和極具難度的挑戰。ADI已開發出一套全面的系統解決方案來應對這些挑戰,其中包含混合信號硅(DAC、ADC和時鐘)、RF功率模塊(GaN/GaAs混合)和先進算法。這三種技術的結合為設備制造商提供了一個靈活的高性能解決方案,能夠以最小的妥協在功耗與系統性能之間實現平衡。軟件定義線性化還支持原有電纜技術到新一代電纜技術的輕松過渡,新一代電纜技術中預計將包含全雙工(FD)、擴展帶寬(至1794 MHz)和包絡跟蹤(ET)。

本文借鑒了Patrick Pratt的數字預失真圖,筆者對此表示感謝。

1 Robert L. Howald。“光纖前沿。”春季技術論壇論文集,2016年。

2 有線電纜數據服務接口規范,DOCSIS? 3.1—物理層規范:CM-SP-PHYv3.1-I08-151210。CableLabs,2017年5月。

作者簡介

Simon Whittle是通信業務部門無線系統部的技術項目經理。工作地點在英國巴斯,主要負責有線電視和5G毫米波系統項目。在2012年7月加入ADI之前,Simon曾在蜂窩通信基礎設施行業工作,負責領導團隊開發3G和4G遠程射頻頭技術。在此之前,他從事蜂窩、移動無線電和廣播應用的接收器和高功率發射器開發工作,并擁有多項專利。他于1983年畢業于英國薩里大學,是IEEE成員。

電子發燒友App

電子發燒友App

評論