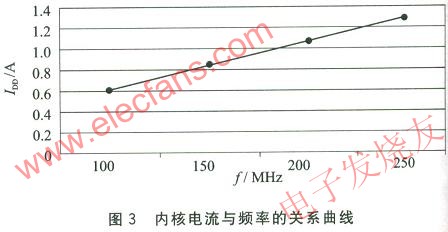

由于本系統是由多片ADSP-TS101組成的系統,所以由40 MHz晶振產生的時鐘信號不能直接接到各DSP和FPGA,而應該通過驅動后再接到各DSP,且時鐘信號到各DSP的距離應該盡可能接近。本系統

2020-11-02 10:36:31 2146

2146

用于多處理TigerSHARC系統的集群總線通信的詳細信號完整性和時序分析。該系統由8個ADSP-TS101S器件,一個主處理器和SDRAM組成,其集群總線運行頻率為100MHz。包括仿真結果和物理

2019-08-30 09:24:28

PCS.預計春節后3月份到貨。ADSP-TS201SAPBZ-060 在途400只+公司庫存285只=685PCS ADSP-TS201SAPBZ050 2404 PCS ADSP-TS201SABP-050 245 PCS ADSP-TS201SYBPZ050873 PCS

2018-12-21 19:48:14

,兼有FPGA和ASIC信號處理性能和指令集處理器的高度可編程性,適用于大存儲量、高性能、高速度的信號處理和圖像處理。如雷達信號處理、無線基站、圖像音頻處理等。2 ADSP-TS201簡介

2019-04-12 07:00:11

{:12:}{:12:}{:12:}{:12:}{:12:}報道:ADSP-TS201誰用過

2012-09-19 14:14:35

)或三個外部中斷(IRQ2,IRQ1,IRQ0)沒有串行端口。 時鐘信號 ADSP-21xx處理器的CLKIN輸入可以由晶體或TTL兼容的外部時鐘信號驅動。在操作過程中,CLKIN輸入不能停止或

2020-07-17 14:23:24

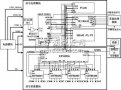

(來自數據存儲器),而互不干擾。這樣可以在1個周期內同時準備好指令和數據,對于數字信號處理中的許多運算,要比一般的單片機速度快得多,這對于實時性要求非常高的噪聲控制來說,是非常必要的。 (2

2011-08-10 15:09:16

高性能32位數字信號處理器在音頻、醫療、軍事、圖形、成像和通信中的應用;超級哈佛體系結構—4條獨立總線,用于雙數據獲取、指令獲取和非侵入、零開銷I/O;向后兼容的程序集源代碼級與ADSP

2020-10-15 17:46:19

的。環境條件ADSP-2126x處理器在第14頁操作條件中規定的TAMB環境條件下的性能。熱特性表38和表39氣流測量符合JEDEC標準JESD51-2和JESD51-6,連接板測量符合JESD51-8

2020-10-14 16:59:05

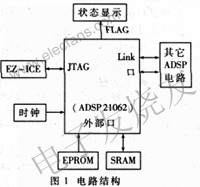

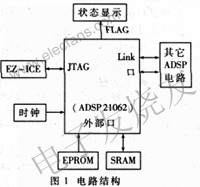

是人們在應用該芯片時必須解決的關鍵問題。本文提出了一種簡單易行的測試方法,并在基于ADSP21062的雷達信號處理系統調試中獲得了成功,驗證了該方法的可行性。

2019-07-19 08:16:35

,用于SAR系統性能的檢驗以及測試,并能評估各種成像算法,分析出建立在不同模型上的算法的有效性。近年來,國內外許多院校和科研機構都投入了大量的人力和物力進行合成孔徑雷達模擬技術的研究。伴隨著SAR的研究

2019-07-22 06:29:35

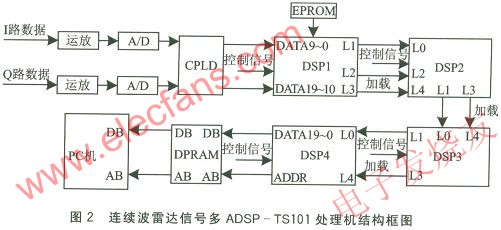

高的應用,可以使用普通串行口作為通訊鏈路。在本系統中,由于采用多片高性能浮點數字信號處理器ADSP-TS101作為處理器,產生了大量的處理結果,并且要求實時傳輸處理結果,傳輸速度必須達到1 MB/s

2019-04-30 07:00:08

本帖最后由 午夜的沉默 于 2015-3-14 22:14 編輯

哪位有ADSP TS101S 芯片的Cadence原理圖封裝啊跪求 ..

2015-03-14 22:13:20

在實際的外場試飛過程中是不可能實現的,這也是雷達信號模擬器對場外試飛的一大優勢。FPGA作為高性能數字信號處理系統中的關鍵部件,在雷達信號模擬和雷達信號采集等方面有著巨大的開發潛能,采用這些技術對雷達

2019-07-15 06:48:33

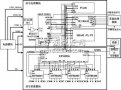

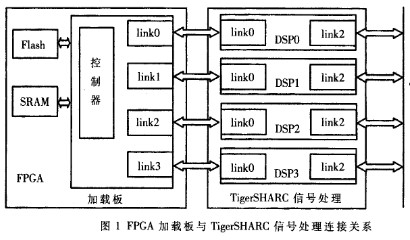

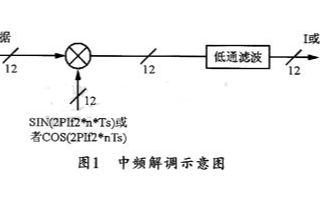

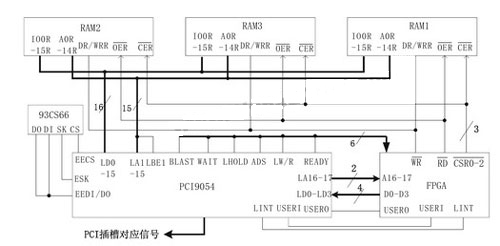

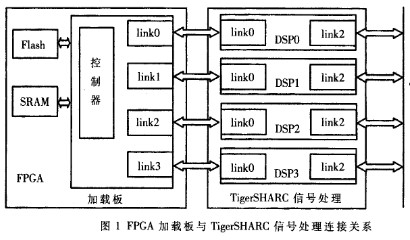

在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統的應用越來越廣泛。那么,我們該怎么利用FPGA與ADSP TS201設計總線接口呢?

2019-08-09 06:56:11

求一個解決系統中主處理器在較高工作頻率300 MHz下穩定工作的問題,以及在兩個主芯片之間和主芯片與數據存儲芯片之間數據高速互聯的問題,提高系統的性能,滿足設計要求的基于ADSP-TS101高速信號處理系統。

2021-04-12 06:39:56

下一代混合信號處理器的標桿產品ADSP-CM40x系列最大的應用之一就是電機控制。這里分享ADSP-CM40x在電機控制中的應用資源供大家學習參考,也歡迎有電機控制應用需求的筒子們跟帖討論、提問

2018-11-05 09:22:46

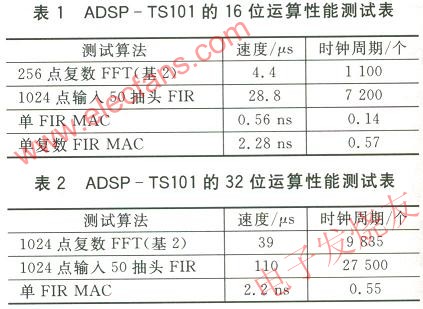

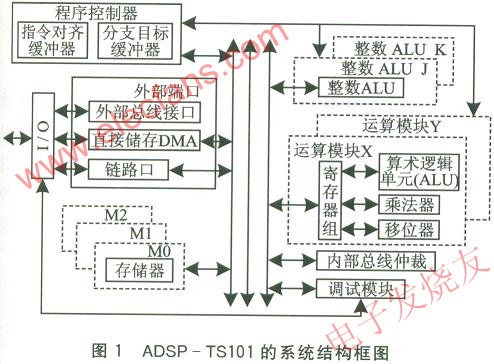

ADSP-TS101S是美國ADI公司推出的一款具有極高性能的數字信號處理器(DSP)芯片,其專為大信號處理任務和通信應用進行了結構上的優化設計,在嵌人式信號處理中得到廣泛應用

2019-08-23 07:59:39

0 引言ADI公司的DSP器件(ADSP-TS101)具有浮點實時處理能力強、并行性好等優點,從而廣泛被彈載信號處理系統選用。其作為彈載主處理器,在導彈的系統試驗中,需要利用上位機對其中的大數

2019-05-31 05:00:04

基于ADSP21161N的PD雷達數據處理機的設計

2009-05-08 17:15:27 11

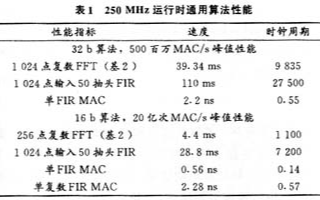

11 ADSP-TS 101 TigerSHARC DSP是一款極高性能的靜態超標量處理器,專為大的信號處理任務和通信結構進行了優化。本文所介紹的雷達模擬器就是針對TS101的優勢利用多片DSP進行設計并實現的

2009-05-09 14:26:57 31

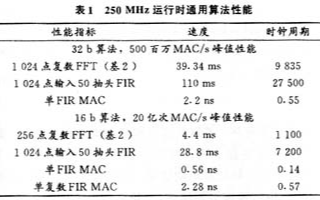

31 對AD 公司的TigerSHARC DSP(ADSP-TS101S) 和摩托羅拉公司的具有AltiVec 矢量處理器核的PowerPC 系列MPC7410 和MPC7455 處理器,在連續實時信號處理領域的應用進行了評估。

2009-05-18 13:25:50 12

12 在機載SAR 的實時成像處理器中,回波信號方位向帶寬以及方位向采樣率不能很好的滿足成像處理的要求,本文選擇ADSP-TS201 處理器芯片對回波信號在成像之前對其進行方位向預處

2009-08-05 09:45:52 18

18 ADSP-TS101 是ADI 公司新一代高性能浮點DSP,開始應用在高速數據采集和處理系統中。TS101 外部總線接口可編程,方便和各種總線外設接口。本文結合TS101 與同步FIFO、SDRAM 和FPGA 的接

2009-08-11 09:49:31 28

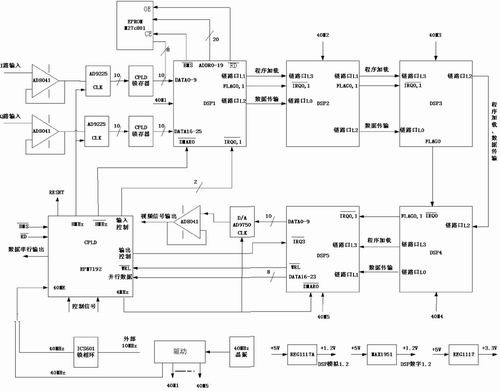

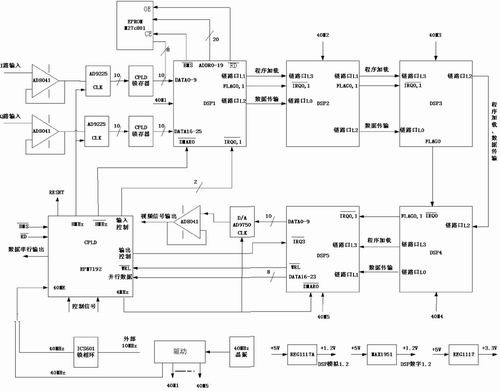

28 針對毫米波跟蹤雷達的特點,在進行理論分析的基礎上,設計了數字信號處理機。采用高性能DSP 芯片TS101 和大規模FPGA 芯片VC4LX40,包含高速多通道ADC 數據采集和DAC 天線伺服單

2009-08-14 11:41:22 44

44 以雷達信號處理領域中的應用為例,介紹了基于ADSP2106X的高速并行數字信號處理系統的設計方法。ADSP2106X本身的特點使其非常適合于高速實時處理的場合,與可編程邏輯器件的組成

2009-11-30 13:22:52 19

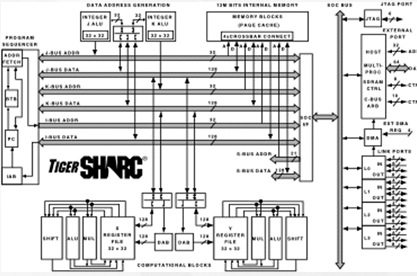

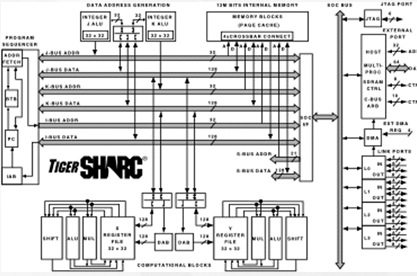

19 總體描述ADSP-TS101S TigerSHARC處理器是一款超高性能、靜態超標量處理器,針對大型信號處理任務和通信基礎設施進行了優化。DSP將非常寬的存儲器寬度與雙計算模塊相結合,支持32/40

2023-03-07 18:24:07

:本文介紹了基于SharcFIN 芯片的數字接收機ICS554 在軟件高頻雷達上與通用信號處理平臺之間的接口實現,給出了ADSP-TS101S 通過該接口實現雷達信號處理系統與ICS554 之間實時通

2009-12-16 12:38:57 16

16 為了滿足干涉超光譜復原處理系統對數據及實時性要求,本文提出了一種基于多ADSP-TS101 的FPGA+DSP[1]的并行圖像處理系統的解決方案,并給出了具體硬件實現。目前,該系統能夠滿

2010-01-06 15:31:32 8

8 本文研究了一種相控陣脈沖多普勒雷達信號處理板的設計及實現。設計基于ADSP21161N組成多處理器系統,具有針對相控陣的多通道處理能力,可實時實現脈沖多普勒雷達信號處理中視

2010-01-12 21:39:44 48

48 總體描述:ADSP-TS201S TigerSHARC處理器是-款超高性能針對大信號優化的靜態超標量處理器性能處理任務和通信基礎設施。數字信號處理器結合了非常寬的內存寬度和雙重計塊一支持浮點

2023-05-10 15:53:12

ADSP-TS101S TigerSHARC?處理器是一款高性能、靜態Superscalar?處理器,針對大型信號處理任務和通信基礎設施進行了優化。DSP集成了非常寬的存儲器寬度和雙通道計算模塊

2023-07-14 16:20:50

微弱地低速運動目標信號,是一個頻率極低,準周期,低信噪比,多諧波組合的信號,如何更加有效準確地檢測目標信號是信號處理領域的難點和熱點。本文提出了基于ADI公司高性能的ADSP-T

2010-08-05 11:37:30 22

22 描述ADSP-TS201S是TigerSHARC處理器系列中的最新款器件之一。ADI公司的TigerSHARC處理器面向眾多依靠多個處理器共同工作來執行計算密集型實時功能的信號處理應用,非常適合

2024-01-26 11:33:09

摘 要:本文是基于ADSP-TS101S的多芯片數字信號處理系統的實現方案。該系統應用于某雷達的信號處理機。文中首先介紹了多片TigerSHARC DSP芯片構成的信號處理系統組成;其次估計系統的運算量,所需計算時間;最后具體說明了CPLD產生復位信號及并-串轉換功能實現的方法。

2006-03-11 13:17:45 856

856

采用ADSP-TS201S芯片的圖像采集處理系統

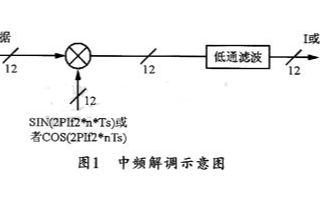

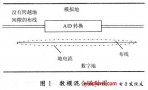

隨著人們對實時信號處理要求的不斷提高和大規模集成電路的迅速發展,作為數字信號處理核心和標志的數字

2009-03-30 12:19:18 1162

1162

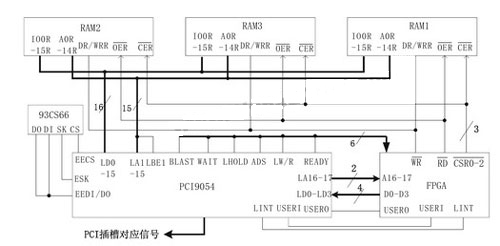

FPGA與ADSP TS201的總線接口設計

在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜

2009-12-11 10:13:29 2356

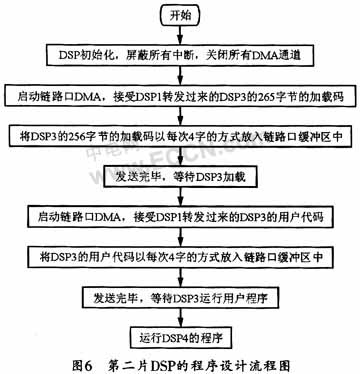

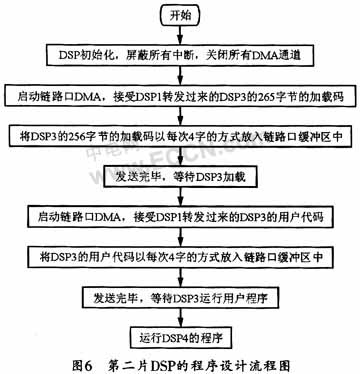

2356 多片TS101S的加載引導設計分析及實現

0 引言ADSP-TS101S數字信號處理器是美國ADI公司推出的TigerSHARC系列中的一款具有極高性能的靜態超標量處理器。該處理器已

2010-03-31 10:20:26 1319

1319

ADSP2106x SHARC是一個適用于語音、通信和圖像處理的高速32位數字信號處理器。該芯片是基于ADSP21000系列DSP芯片發展起來的一個完整的單片系統,增加了一個雙口片內SRAM.

2010-09-26 10:48:22 1259

1259

為了解決 雷達信號處理 中的高速運算, 大容量存儲和高速數據傳輸的問題, 提出采用 TS201 芯片實現雷達信號處理機設計, 利用其超高性能的處理能力和易于構造多處理并行系統的特

2011-07-20 17:20:13 65

65 聲雷達信號采集系統主要由信號采集、信號處理、電源和時鐘四部分組成,本文介紹的基于美國模擬器件公司的DSP ADSP-TS201S和ADC AD7864的信號采集系統。

2011-08-17 11:17:52 1326

1326

本文介紹了一種通用信號處理模塊設計方法,該模塊選用高性能浮點DSP 芯片ADSP-TS101 實現各種信號處理功能,以可靠性高、開放性好、通用性強的VME 總線作為通用信號處理平臺的控制總

2011-09-07 18:56:03 36

36 設計并實現了一種基于ADSP TS201的組網雷達數據融合實時處理系統。主要闡述了雙ADSP TS201并行處理系統的結構、算法量的估計與結果分析。系統可滿足集中式組網融合和分布式組網融合

2011-10-09 10:49:40 30

30 介紹了一種基于DSP芯片ADSP-TS101S的圖像采集和處理系統,應用于復雜條件下目標的檢測,并著重于硬件系統的分析

2011-10-11 15:08:06 75

75 在DSP系統上運行的程序,系統上電復位后需要加載程序到DSP的程序存儲器內。這是使用外部加載模式時的系統開發不可缺少的環節。針對實際需求,提出了一種使用USB對ADSP_TS101S進行鏈

2012-06-08 08:51:08 0

0 本文基于ADSP-TS101高速信號處理系統采用了集成系統設計,硬件部分引入信號完整性分析的設計方法進行高速數字電路的設計,解決系統中主處理器在較高工作頻率300 MHz下穩定工作的問題

2012-09-06 17:15:51 2261

2261

線性調頻信號特征分析及其在現代雷達中的應用。

2016-01-15 15:17:24 7

7 第一章雷達信號分析與處理,有需要的下來看看

2016-08-05 17:32:53 0

0 線性調頻信號特征分析及其在現代雷達中的應用

2017-01-10 21:13:58 18

18 大規模集成電路技術的發展,作為數字信號處理的核心數字信號處理器(DSP)得到了快速的發展和應用。ADSP-TS201DSP是美國模擬器件(ADD公司繼TSl01之后推出的一款高性能處理器。此系列DSP性價比很高,兼有FPGA和ASIC信號處理性能和指令集處理器的高

2017-10-20 15:01:32 0

0 ADSP-TS101S是美國ADI公司推出的一款具有極高性能的數字信號處理器(DSP)芯片,其專為大信號處理任務和通信應用進行了結構上的優化設計,在嵌人式信號處理中得到廣泛應用

2017-10-21 10:26:04 0

0 ADSP-TS101S是美國ADI公司推出的一款具有極高性能的數字信號處理器(DSP)芯片,其專為大信號處理任務和通信應用進行了結構上的優化設計,在嵌人式信號處理中得到廣泛應用

2017-10-21 10:46:43 1

1 作為面向數字信號處理的可編程嵌入式處理器,DSP具有高速、靈活、可靠、可編程、低功耗、接口豐富、處理速度快、實時性好等特點。雷達信號處理系統所涉及的主要技術包括數據重采樣、參數估計、自適應濾波

2017-10-24 14:59:20 3

3 ADI公司的高性能數字信號處理器Tiger-SHARC系歹0包括ADSP-TS101S、ADSP-TS201S、ADSP-TS202S和ADSP-TS203S等芯片。它們被廣泛應用于視頻和通信市場

2017-11-03 15:12:51 1

1 現代雷達信號處理已成為雷達功能實現的關鍵,本文根據某型雷達信號處理機的系統需要,對其硬件結構及軟件設計做了系統優化。設計了1套以4片 TS201和1片FPGA為核心信號處理板,該系統僅用l副板卡

2017-12-11 02:21:07 1881

1881

TigerSHARC系列處理器是ADI公司推出的高性能數字信號處理器,包含ADSP TS101、ADSP TS201、ADSP TS202、ADSP TS203。TigerSHARC系列處理

2019-04-19 08:05:00 1943

1943

電子發燒友網為你提供ADI(ti)ADSP-TS101S相關產品參數、數據手冊,更有ADSP-TS101S的引腳圖、接線圖、封裝手冊、中文資料、英文資料,ADSP-TS101S真值表,ADSP-TS101S管腳等資料,希望可以幫助到廣大的電子工程師們。

2019-02-22 15:01:34

TS201是ADI公司繼ADSP-TS101之后又推出的新一代高性能Tiger-SHARC處理器,它集成了更大容量的存儲器,性價比很高。它兼有ASIC和FPGA的信號處理性能和指令集處理器的高度可編程性與靈活性,適用于高性能、大存儲量的信號處理和圖像應用。其特點如下:

2020-08-27 09:05:59 2254

2254

模擬器件公司(Analog Devices)推出的下一代TigerSHARC處理器ADSP-TS201,ADSP-TS-202和ADSP-TS203。它的每瓦DSP性能是最高的。

2021-01-11 12:01:00 1803

1803

EE-211: ADSP-TS20x TigerSHARC(R)處理器上的16-bit FIR濾波器

2021-03-21 15:22:27 0

0 EE-200: ADSP-TS20x TigerSHARC?處理器的啟動加載內核運行

2021-03-21 15:24:55 1

1 數字信號處理就是用一些數學算法對數字信號進行分析、變換、綜合、估值和識別。作為數字信號處理核心和標志的數字信號處理器(DSP)芯片自問世以來得到了快速的發展,廣泛應用于通信系統、圖形/圖像處理、雷達

2021-03-26 09:21:12 2198

2198

ADSP-TS101S IBIS數據文件BGA包

2021-04-12 16:11:10 4

4 ADSP-TS101S EZ-KIT有限公司設計數據表(1.3版)

2021-04-13 15:14:10 0

0 EE-201:ADSP-TS20x TigerSHARC?處理器片上SDRAM控制器

2021-04-13 18:00:50 6

6 EE-198:ADSP-TS201S TigerSHARC?處理器IBIS文件用戶指南

2021-04-13 18:10:30 8

8 ADSP-TS201S:TigerSHARC嵌入式處理器過時數據表

2021-04-15 18:45:56 6

6 EE-157:解釋ADSP-TS101上的分支目標緩沖區

2021-04-15 21:33:37 13

13 EE-176:ADSP-TS101S老虎SHARC高級Processor硬件設計檢查表

2021-04-16 08:51:20 0

0 EE-205:將代碼從ADSP-TS101S TigerSHARC?處理器移植到ADSP-TS201S TigerSHARC處理器的注意事項

2021-04-16 13:54:51 9

9 EE-283:采用ADSP-TS20x TigerSHARC?處理器的外部總線仲裁

2021-04-16 15:34:05 10

10 EE-217:更新ADSP-TS101S老虎SHARC-ZEZ-KIT有限公司

2021-04-16 18:18:12 5

5 EE-170:評估ADSP-TS201S TigerSHARC?處理器的功耗

2021-04-21 10:41:30 6

6 EE-182:ADSP-TS201S TigerSHARC?處理器的散熱設計

2021-04-22 09:46:01 10

10 EE-143:了解ADSP-TS101上的DMA

2021-04-24 11:29:52 7

7 EE-215:采用ADSP-TS20x TigerSHARC?處理器的16位紅外過濾

2021-04-24 19:31:09 2

2 EE-174:ADSP-TS101S虎-SHARC高級ProcessLuter加載內核手術

2021-04-25 10:17:06 9

9 EE-169:ADSP-TS101S的功耗估算

2021-05-10 09:55:06 8

8 ADSP-TS101 TigerSHARC處理器編程參考

2021-05-13 17:11:14 8

8 ADSP-TS101S TigerSHARC版本0.2、0.4異常列表

2021-05-14 15:46:33 0

0 用于ADSP-TS101S TigerSHARC處理器的EZ套件精簡版產品亮點

2021-05-17 17:33:44 0

0 ADSP-TS101S EZ套件精簡版?SUP_

2021-05-17 20:10:12 0

0 ADSP-TS201 TigerSHARC處理器編程參考

2021-05-18 09:21:19 1

1 ADSP-TS201 TigerSHARC處理器硬件參考

2021-05-18 15:46:19 1

1 ADSP-TS101S EZ-KIT Lite評估系統手冊(1.1版,2004年3月)

2021-05-18 17:38:05 0

0 ADSP-TS202S:TigerSHARC嵌入式處理器過時數據表

2021-05-22 09:28:22 0

0 ADSP-TS101 TigerSHARC處理器硬件參考

2021-05-22 10:59:30 4

4 EE-218:為ADSP-TS201 TigerSHARC?處理器編寫高效浮點FFT

2021-05-26 09:17:20 5

5 EE-178:ADSP-TS101S TigerSHARC?片上SDRAM控制器

2021-05-27 18:03:52 14

14 ADSP-TS201S EZ-KIT Lite為開發人員提供一種經濟有效的方法,可以初步評估ADSP-TS201S TigerSHARC? 處理器和其多處理器能力。 該EZ-KIT Lite包括桌面

2021-06-09 08:59:50 4

4 ADSP-TS101S IBIS數據文件BGA包

2021-06-16 08:36:40 11

11 EE-201 ADSP-TS20x TigerSHARC?處理器片上SDRAM控制器

2021-06-18 10:47:01 4

4 電子發燒友網站提供《基于ADSP-TS201的著陸雷達恒虛警電路實現.pdf》資料免費下載

2023-10-23 09:59:21 0

0 電子發燒友網站提供《TigerSHARC? ADSP-TS201S處理器的散熱設計要點.pdf》資料免費下載

2023-11-29 11:12:01 0

0

電子發燒友App

電子發燒友App

評論