引言

現(xiàn)代通信技術(shù)正走向網(wǎng)絡(luò)核心技術(shù)分組化、窄帶接入技術(shù)無線化。現(xiàn)在無線作為有線的有效補(bǔ)充,得到了越來越廣泛的應(yīng)用,在很多場合,許多多媒體應(yīng)用需要短距離的無線傳輸。無線多媒體系統(tǒng)除了提供多媒體服務(wù)外,具有無線所具有的建設(shè)速度快、安裝靈活方便等優(yōu)點(diǎn),還能在布線困難的地方實現(xiàn)多媒體通信。因此,無線多媒體具有廣闊的應(yīng)用前景。但無線也存在著一系列的問題,如多經(jīng)傳輸、信道衰落和空間射頻干擾等。

1無線多媒體系統(tǒng)概述

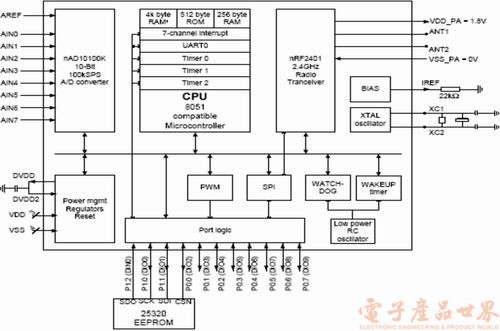

本系統(tǒng)為無線可視系統(tǒng),集圖像、聲音、控制、數(shù)據(jù)等多媒體信息的采集、傳輸和處理為一體,系圖1無線多媒體系統(tǒng)框圖統(tǒng)能傳輸單向視頻信號,雙向語音信號,雙向數(shù)據(jù)信號,并具有數(shù)據(jù)采集等功能。系統(tǒng)框圖如圖1所示,系統(tǒng)分為主機(jī)和從機(jī)。通過對主從機(jī)的參數(shù)設(shè)定可以實現(xiàn)點(diǎn)對點(diǎn)和點(diǎn)對多點(diǎn)通信。主從機(jī)之間可以實現(xiàn)實時的雙向語音通信,同時從機(jī)把視頻信號傳給主機(jī),從機(jī)還可以把傳感器等的數(shù)據(jù)傳給主機(jī)。

圖1無線多媒體系統(tǒng)框圖

2系統(tǒng)設(shè)計

2.1NRF903芯片介紹

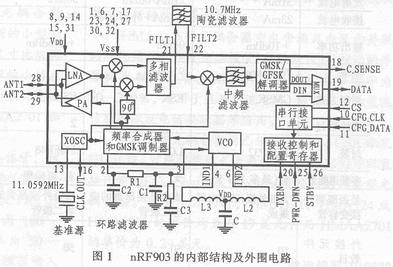

射頻收發(fā)電路采用NordicVLSI公司的單片射頻收發(fā)芯片NRF903。該芯片的工作頻率為國際通用的ISM頻段433/868/915MHz,NRF采用抗干擾能力強(qiáng)的GMSK調(diào)制方式來優(yōu)化信道效率,在GMSK中,在調(diào)制載波前采用了高斯濾波器,這樣可以在同等帶寬下傳輸更高速率的數(shù)據(jù),可在155.6kHz的有效帶寬下傳輸最高76.8kbps的數(shù)據(jù)。最大發(fā)射功率可以調(diào)整到+10dBm,天線接口設(shè)計為差分天線。NRF903的工作電壓范圍為2.7~3.3V,NRF還具有待機(jī)模式,這樣可以更省電和高效。芯片的參數(shù)包括工作頻率和發(fā)射功率都可以通過一個14bit的配置寄存器用SPI串行線進(jìn)行設(shè)置。采用DSS+PLL頻率合成技術(shù),頻率穩(wěn)定性極好;靈敏度高,達(dá)到-100dBm.內(nèi)置獨(dú)有的鏡像頻率抑制電路。

2.2射頻模塊電路設(shè)計

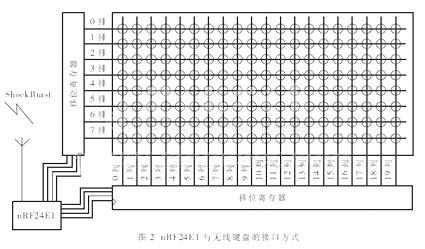

為了提高發(fā)送距離,本系統(tǒng)中的NRF903模塊采用拉桿天線,如圖2所示,有效值的設(shè)定才能保證良好的功能,根據(jù)公式 在不同的PCB板的模塊調(diào)試中,選定CS,CP,LP的參數(shù)值使電路諧振在所工作的頻段,同時使LS,CS1發(fā)生諧振。所選定的電容、電感必須具備良好的性能。PCB的底面有一個連續(xù)的接地面,射頻電路的元件面以NRF903為中心,各元器件緊靠其周圍,盡可能減少分布參數(shù)的影響。射頻部分的電源與數(shù)字電路部分的電源分離,NRF903的VSS端直接連接到接地面。注意不能將數(shù)字信號或控制信號引入到PLL回路濾波器元件上。NRF903的VCO電感位置的最佳設(shè)計是保證產(chǎn)生1.1±0.2V的PLL回路濾波器電壓。

在不同的PCB板的模塊調(diào)試中,選定CS,CP,LP的參數(shù)值使電路諧振在所工作的頻段,同時使LS,CS1發(fā)生諧振。所選定的電容、電感必須具備良好的性能。PCB的底面有一個連續(xù)的接地面,射頻電路的元件面以NRF903為中心,各元器件緊靠其周圍,盡可能減少分布參數(shù)的影響。射頻部分的電源與數(shù)字電路部分的電源分離,NRF903的VSS端直接連接到接地面。注意不能將數(shù)字信號或控制信號引入到PLL回路濾波器元件上。NRF903的VCO電感位置的最佳設(shè)計是保證產(chǎn)生1.1±0.2V的PLL回路濾波器電壓。

元器件值的選定見文獻(xiàn)[1],根據(jù)不同的PCB板以及相關(guān)器件特性,根據(jù)頻譜分析和測定的電壓等值,可以適當(dāng)?shù)恼{(diào)整這些元器件的值,使其性能達(dá)到最佳。模塊如圖2所示CFG-CLK,CFG-DATA,CS為初始化配置線。STBY為待機(jī)模式控制端,“0”為工作模式,“1”為待機(jī)模式。CLK_OUT為分頻時鐘輸出。C_SENSE為載波檢測輸出,當(dāng)沒有接收到載波信號時,C_SENCE輸出電壓為“0”,隨著接收電平的上升,C2SENCE的輸出電壓上升,上升到輸入電平值接近接收靈敏度極限以上10dB點(diǎn)時,C_SENCE為“1”。TXEN為發(fā)射控制端,“0”為接收模式,“1”為發(fā)射模式。DATA端為數(shù)據(jù)輸入?輸出端。PWR_DWN為掉電模式控制端,“0”為工作模式,“1”為掉電模式。其余的引腳為VCC和VSS。

圖2射頻模塊電路框圖

2.3初始化程序設(shè)計

在NRF903模塊正常工作前,需對其內(nèi)部14bit的控制寄存器通過CFG_CLK,CFG_DATA,CS進(jìn)行初始化。CS,CFG_CLK和CFG_DATA組成的串行接口將控制參數(shù)鎖存到內(nèi)部配置單元的移位寄存器中。芯片選擇腳(CS)用來使能芯片的配置模式。配置期間,CS為高,配置字被鎖入(MSB在先)。配置字被鎖入移位寄存器后,CS變低,配置開始啟動。配置時序見文獻(xiàn)[2]。

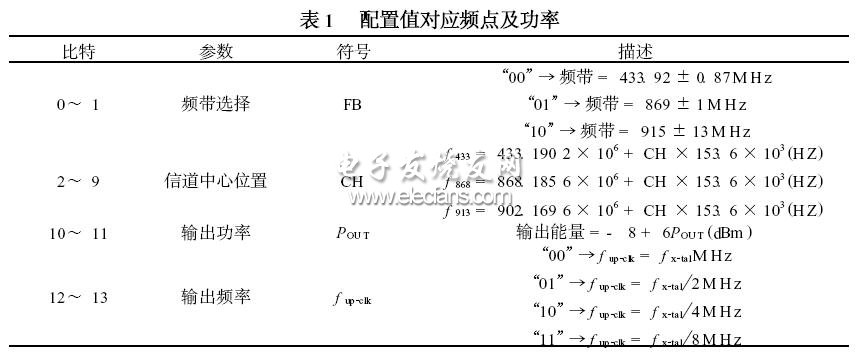

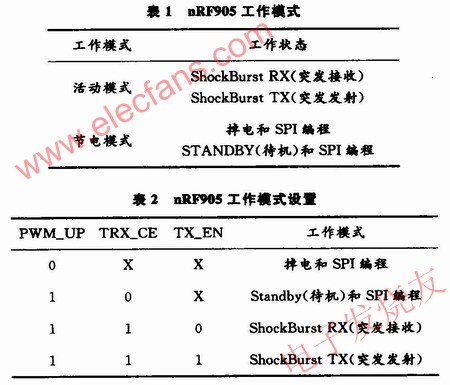

CFG_DATA位速率不能超過1Mbps。一旦配置完,設(shè)備狀態(tài)由外部信號TXEN,PWR_DWN,STBY和DATA(DATA在發(fā)射模式為輸入腳,在接收模式為輸出腳)來設(shè)定。配置可以在除了待機(jī)和掉電以外的所有模式中完成。在掉電和待機(jī)模式工作后,寄存器內(nèi)容仍然有效。配置數(shù)據(jù)只有當(dāng)電源撤除后才會丟失。如果不進(jìn)行配制,模塊在默認(rèn)模式下,工作頻率為868.1856MHz,按最大功率輸出,CLK_OUT為1.3284MHz。該特性使微控制器的軟件調(diào)試變得簡單、方便。配置中的1~2位為頻段選擇,3~10位為頻點(diǎn)選擇,11~12為輸出功率設(shè)置,13~14為時鐘分頻輸出設(shè)置,如表1所示。

在本系統(tǒng)中,工作頻段為927M,選擇的配置字為1000,0010,0100,10。初始化程序如下:

CLRP3.5;PWN-DWN=0,置工作模式

CLRP1.7;STBY=0,置工作模式

MOVR3,#08H

MOVA,#82H

SETBP3.6;配置期間CS拉高

CFG1:RLCA

MOVP3.0,C;

CLRP3.1

SETBP3.1

DJNZR3,CFG1

MOVR3,#06H

MOVA,#48H

CFG2:RLCA

MOVP3.0,C

CLRP3.1

SETBP3.1

DJNZR3,CFG2

CLRP3.6;CS置低,配置結(jié)束。

電子發(fā)燒友App

電子發(fā)燒友App

評論