?

介紹

軟件無線電(SDR)是具有可重配置硬件平臺的無線設備,可以跨多種通信標準。因為具有更低的成本、更大的靈活性和更高的性能,軟件無線電已迅速成為軍事、公共安全和商用無線領域的事實標準。SDR成為商用流行的主要原因之一是它能夠對多種波形進行基帶處理和數字中頻(IF)處理。IF處理將數字信號處理的領域從基帶擴展到RF。支持基帶和中頻處理的能力增加了系統靈活性,同時減小了制造成本。

基帶處理

--- 無線標準不斷地發展,通過先進的基帶處理技術如自適應調制編碼、空時編碼(STC)、波束賦形和多入多出(MIMO)天線技術,支持更高的數據速率。基帶信號處理器件需要巨大的處理帶寬,以支持這些技術中大計算量的算法。例如,美國軍事聯合戰術無線系統(JTRS)定義了軍事無線中20多種

不同的無線波形。一些更復雜的波形所需的計算能力在標準處理器上是每秒數百萬條指令(MIPS),如果在FPGA上實現則是數千個邏輯單元。

協處理器特性

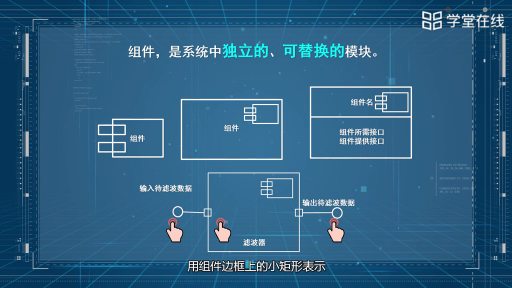

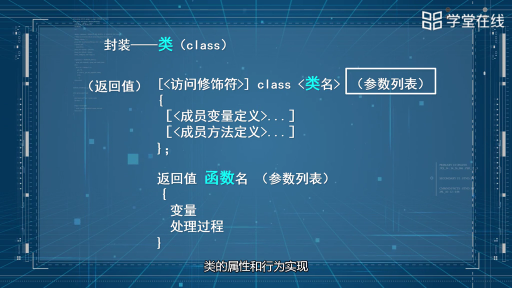

--- SDR基帶處理通常需要處理器和FPGA。在這類應用中,處理器處理系統控制和配置功能,而FPGA實現大計算量的信號處理數據通道和控制,讓系統延遲最小。當需要從一種標準切換至另一種標準時,處理器能夠動態地在軟件的主要部分間切換,而FPGA能夠根據需要完全重新配置,實現特定標準的數據通道。

--- FPGA可以作為協處理器同DSP和通用處理器相連,這樣具有更高的系統性能和更低的系統成本。自由地選擇在哪實現基帶處理算法為實現SDR算法提供了另一種方式的靈活性。

--- 基帶部件也需要足夠靈活讓所需的SDR功能支持在同一種標準增強版本之間的移植,并能夠支持完全不同的標準。可編程邏輯結合軟核處理器和IP,具有了提供在現場遠程升級的能力。圖1 是一個框圖,其中FPGA能夠通過IP功能如Turbo編碼器、Reed-Solomon編碼器、符號交織器、符號映射器和IFFT,很容易地重配置支持WCDMA/HSPDA或802.16a標準的基帶發送功能。

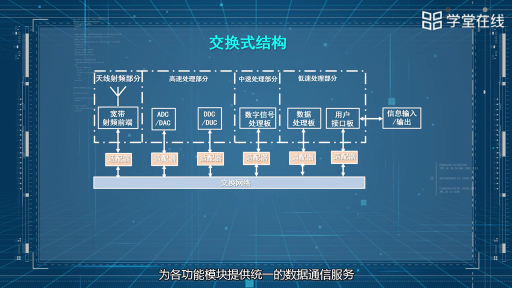

數字IF處理

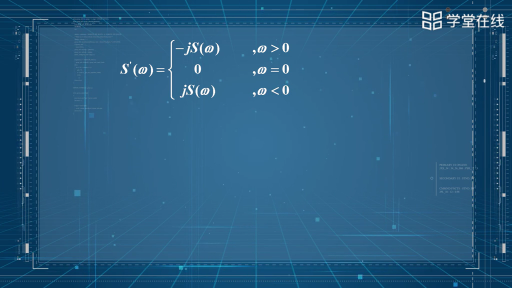

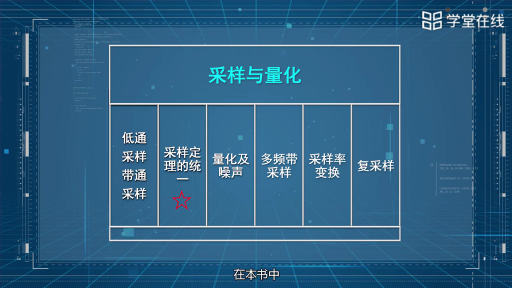

--- 數字頻率變化具有比傳統模擬無線處理方式更高的性能。FPGA提供了一種高度靈活和集成的平臺,在這之上以合理的功率實現大計算量的數字IF功能,這在便攜系統中是一個關鍵的因素。能夠在FPGA上實現的IF功能包括數字上變頻器(DUC)和下變頻器(DDC),以及數字預畸變(DPD)和波峰系數削減(CFR),幫助降低功放的成本和功率(見圖2) --- 注釋:DUC:數字上變頻器;CFR: 波峰系數削減;DPD: 數字預畸變;DDC: 數字下變頻器;PA: 功放;LNA: 低噪放。

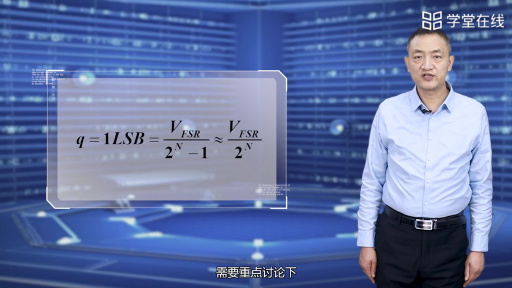

數字上變頻器

--- 數字格式(在基帶處理單元和上變頻器之間一般需要)可以順利地加到上變頻器的前端。這項技術為上變頻器提供了全定制的前端,容許信道化的高帶寬輸入數據。定制邏輯或軟核嵌入式處理器可用來控制上變頻器和FPGA中實現的基帶處理單元之間的接口。 --- 在數字上變頻中,輸入數據在用可調的載波頻率進行正交調制之前經過基帶濾波和插值。為了實現插值基帶有限沖激響應(FIR)濾波器,必須在速度面積之間進行權衡為特定的標準獲得優化的固定或自適應架構。數控振蕩器核也能夠產生多種架構,它們具有超過115db無寄生動態范圍和非常高的性能。根據支持的頻率分配數量,在FPGA中可以很容易地例化多個上變頻器。

波峰系數削減

--- 3G 基于CDMA的系統和多載波系統如正交頻分復用(OFDM)的信號具有很高的峰平比(波峰系數)。這樣的信號會極大地降低基站中功放的效率。對多波形標準,在FPGA中實現的波峰系數削減技術是一種降低功放成本和復雜度的合算的方式。

數字預畸變

--- 高速移動數據傳輸采用非恒包絡調制技術如QPSK和正交幅度調制(QAM)。這對PA的線性度有嚴格的要求。DPD線性化技術,包括查找表和多項式方式都可以有效地在包含DSP塊的FPGA中實現。這些DSP塊中的乘法器可以在很高的時鐘速率下運行,可以有效地分時實現復數乘法。當SDR基站中使用FPGA時,FPGA可以為特定的標準重配置來實現合適的DPD算法,有效地線性化PA。 數字下變頻器

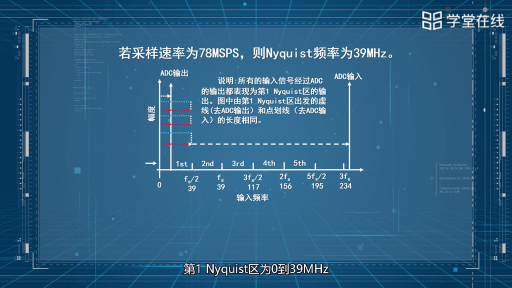

--- 在接收器側,數字IF技術可以對IF信號進行采樣,在數字域執行信道化和采樣率轉換。使用降采樣技術,高頻IF信號(同時100MHz以上)可以被量化。因為不同的標準有不同的碼片/比特速率,對SDR應用需要非整數采樣率,把采樣數轉換為任何標準基本碼片/比特速率的整數倍。

結論

--- FPGA提供了通用的計算結構,非常適合于軟件無線電中基帶和IF數字處理的需要。另外,FPGA作為通用處理器或DSP軟件處理的硬件協處理器,能夠增強功能,改善吞吐量,減小系統成本和降低系統功率。

電子發燒友App

電子發燒友App

評論