隨著現代無線通信系統的發(fā)展,移動通信、雷達、衛(wèi)星通信等通信系統對收發(fā)切換開關的開關速度、功率容量、集成性等方面有了更高的要求, 因此研究VXI總線技術,開發(fā)滿足軍方特殊要求的VXI總線模塊,具有十分重要的意義,我們將利用虛擬儀器思想,將硬件電路以軟件的方式實現,以下設計的射頻開關可以由計算機直接控制,可以很方便地與VXI總線測試系統集成,最大限度的發(fā)揮計算機和微電子技術在當今測試領域中的應用,具有廣闊的發(fā)展前景。

1 VXI總線接口電路的設計與實現

VXIbus是VMEbus在儀器領域的擴展,是計算機操縱的模塊化自動儀器系統。它依靠有效的標準化,采用模塊化的方式,實現了系列化、通用化以及VXIbus儀器的互換性和互操作性,其開放的體系結構和Plug&Play方式完全符合信息產品的要求。它具有高速數據傳輸、結構緊湊、配置靈活、電磁兼容性好等優(yōu)點,,因此系統組建和使用非常方便,應用也越來越廣泛,已逐漸成為高性能測試系統集成的首選總線。

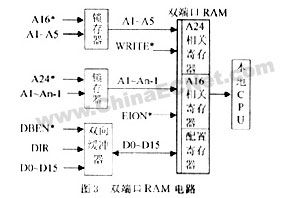

VXI總線是一種完全開放的、適用于各儀器生產廠家的模塊化儀器背板總線規(guī)范。VXI總線器件主要分為:寄存器基器件、消息基器件和存儲器基器件。目前寄存器基器件在應用中所占比例最大(約70%)。VXIbus寄存器基接口電路主要包括:總線緩沖驅動、尋址和譯碼電路、數據傳輸應答狀態(tài)機、配置及操作寄存器組四個部分。四個部分中除總線緩沖驅動采用74ALS245芯片來實現外,其余部分都用FPGA來實現。采用一片FLEX10K 芯片EPF10K10QC208-3和一片EPROM芯片EPC1441P8,利用相應軟件MAX+PLUSⅡ來進行設計與實現。

1.1 總線緩沖驅動

該部分完成對VXI背板總線中的數據線、地址線和控制線的緩沖接收或驅動,以滿足VXI規(guī)范信號的要求。對于A16/D16器件,只要實現背板數據總線D00~D15的緩沖驅動。根據VXI總線規(guī)范的要求,此部分采用兩片74LS245實現,用DBEN*(由數據傳輸應答狀態(tài)機產生)來選通。

1.2 尋址和譯碼電路

尋址線包括地址線A01~A31、數據選通線DS0*和DS1*、長字線LWORD*。控制線包括地址選通線AS*和讀/寫信號線WRITE*。

本電路的設計采用MAX+PLUSⅡ的原理圖設計方式。利用元件庫里的現有元件進行設計,采用了兩片74688和一片74138。

該功能模塊對地址線A15~A01及地址修改線AM5~AM0進行譯碼。當器件被尋址時,接收地址線及地址修改線上的地址信息,并將其與本模塊上硬件地址開關設置的邏輯地址LA7~LA0相比較,如果AM5~AM0上邏輯值為29H或2DH(由于是A16/D16器件),地址線A15、A14均為1,并且A13~A06上的邏輯值與模塊的邏輯地址相等時,該器件被尋址選通(CADDR*為真)。接著其結果被送往下一級譯碼控制,通過對地址A01~A05進行譯碼選中模塊在16位地址空間的寄存器。

1.3 數據傳輸應答狀態(tài)機

數據傳輸總線是一組高速異步并行數據傳輸總線,是VMEbus系統信息交換的主要組成部分。數據傳輸總線的信號線可分為尋址線、數據線、控制線三組。

該部分的設計采用MAX+PLUSⅡ的文本輸入設計方式。由于DTACK*的時序比較復雜,所以采用AHDL語言來進行設計,通過狀態(tài)機實現。

該功能模塊對VXI背板總線中的控制信號進行組態(tài),為標準數據傳輸周期提供時序及控制信號(產生數據傳輸使能信號DBEN*,總線完成數據傳輸所需的應答信號DTACK*等)。在進行數據傳輸時,系統控制者首先對模塊進行尋址,并將相應的地址選通線AS*,數據選通線DS0*、DS1*以及控制數據傳輸方向的WRITE*信號線等設置為有效電平。當模塊檢測到地址匹配及各控制線有效后,驅動DTACK*為低電平,以此向總線控制者確認已經將數據放置在數據總線上(讀周期) 或已經成功地接收到數據(寫周期)。

1.4 配置寄存器

每個VXI總線器件都有一組“配置寄存器”,系統主控制器通過讀取這些寄存器的內容來獲取VXI總線器件的一些基本配置信息,如器件類型、型號、生產廠家、地址空間(A16、A24、A32)以及所要求的存儲空間等。

VXI總線器件的基本配置寄存器有:識別寄存器、器件類型寄存器、狀態(tài)寄存器、控制寄存器。

該部分電路的設計采用MAX+PLUSⅡ的原理圖設計方式,利用74541芯片,其創(chuàng)建的功能模塊。

ID、DT、ST寄存器都是只讀寄存器,控制寄存器為只寫寄存器。本設計中,VXI總線主要用于控制這批開關的通斷,所以,只要向通道寄存器中寫入數據就可以控制繼電器開關的吸和或斷開狀態(tài),查詢繼電器狀態(tài)也是從通道寄存器中讀取數據即可。根據模塊設計需要,在其相應各數據位寫入適當的內容,從而能夠對功能模塊的射頻開關進行有效控制。

2 模塊功能電路PCB板的設計

每個VXI總線器件都有一組“配置寄存器”,系統主控制器通過讀取這些寄存器的內容來獲取VXI總線器件的一些基本配置信息,如器件類型、型號、生產廠家、地址空間(A16、A24、A32)以及所要求的存儲空間等。

射頻電路的頻率范圍約為10kHz到300GHz。隨著頻率的增加,射頻電路表現出不同于低頻電路和直流電路的一些特性。因此,在設計射頻電路的PCB板時就需要特別注意射頻信號給PCB板所帶來的影響。本射頻開關電路是由VXI總線控制的,在設計中為減少干擾,在總線接口電路部分與射頻開關功能電路間采用排線連接,以下主要介紹射頻開關功能電路部分PCB板的設計。

2.1 元器件的布局

電磁兼容性(EMC)是指電子系統在規(guī)定的電磁環(huán)境中按照設計要求能正常工作的能力。對于射頻電路PCB設計而言,電磁兼容性要求每個電路模塊盡量不產生電磁輻射,并且具有一定的抗電磁干擾能力。而元器件的布局直接影響到電路本身的干擾及抗干擾能力。也直接影響到所設計電路的性能。

布局總的原則:元器件應盡可能同一方向排列,通過選擇PCB進入熔錫系統的方向來減少甚至避免焊接不良的現象;元器件間最少要有0.5mm的間距才能滿足元器件的熔錫要求,若PCB板的空間允許,元器件的間距應盡可能寬。

元器件的合理布局也是合理布線的一個前提,因此應該綜合考慮。在本設計中,繼電器是用于轉換射頻信號的通道,故應將繼電器盡量貼近信號輸入端與輸出端,以此來盡量減短射頻信號線的走線長度,為下一步的合理布線做出考慮。

此外,本射頻開關電路是由VXI總線控制,射頻信號對VXI總線控制信號的影響也是布局時必須考慮的問題。

2.2 布線

在基本完成元器件的布局后,就要開始布線,布線的基本原則為:在組裝密度許可情況下,盡量選用低密度布線設計,并且信號走線盡量粗細一致,有利于阻抗匹配。

對于射頻電路,信號線的走向、寬度、線間距的不合理設計,可能造成信號傳輸線之間的交叉干擾;另外,系統電源自身還存在噪聲干擾,所以在設計射頻電路PCB時一定要綜合考慮,合理布線。

布線時,所有走線應遠離PCB板的邊框(2mm左右),以免PCB板制作時造成斷線或有斷線的隱患。電源線要盡可能寬,以減少環(huán)路電阻,同時,使電源線、地線的走向和數據傳遞的方向一致,以提高抗干擾能力。所布信號線應盡可能短,并盡量減少過孔數目;各元器件間的連線越短越好,以減少分布參數和相互間的電磁干擾;對于不相容的信號線應盡量相互遠離,而且盡量避免平行走線,而在正反兩面的信號線應相互垂直:布線時在需要拐角的地方應以135度角為宜,避免拐直角。

以上設計中,PCB板采用四層板,為減小射頻信號對VXI總線控制信號的影響,故將兩種信號走線分別放在中間兩層,且射頻信號線用接地過孔帶屏蔽。

2.3 電源線和地線

在射頻電路PCB設計中的布線需要特別強調的是電源線與地線的正確布線。電源和地線方式的合理選擇是儀器可靠工作的重要保證。射頻電路的PCB板上相當多的干擾源是通過電源和地線產生的,其中地線引起的噪聲干擾最大。根據PCB板電流的大小,電源線、地線線條設計的要盡量粗而短,減少環(huán)路電阻。同時使電源線、地線的走向和數據傳遞的方向一致,這樣有助于增強抗噪聲能力。在條件允許的情況下盡量采用多層板,四層板比雙面板噪聲低20dB,六層板又比四層板噪聲低10dB。

在本文設計的四層PCB板中,頂層和底層兩層均設計為地線層。這樣無論中間層哪一層為電源層,電源層和地線層這兩個層彼此靠近的物理關系,形成了一個很大的去耦電容,減少了地線所帶來的干擾。

地線層采用大面積鋪銅。大面積鋪銅主要有以下幾個作用:

(1)EMC.對于大面積的地或電源鋪銅,會起到屏蔽作用。

(2)PCB工藝要求。一般為了保證電鍍效果,或者層壓不變形,對于布線較少的PCB板層鋪銅。

(3)信號完整性要求,給高頻數字信號一個完整的回流路徑,并減少直流網絡的布線。

(4)散熱,特殊器件安裝要求鋪銅等等。

3 結論

VXI總線系統是一種在世界范圍內完全開放的、適用于多廠商的模塊化儀器總線系統,是目前世界上最新的儀器總線系統。以上主要介紹了基于VXI總線的射頻開關模塊的研制。介紹了總線接口的設計以及射頻開關模塊功能電路部分PCB板的設計。射頻開關由VXI總線控制,增加了開關操作的靈活性,使用方便。

電子發(fā)燒友App

電子發(fā)燒友App

評論