中國北京——Analog Devices, Inc. (NASDAQ:ADI),全球領先的高性能信號處理解決方案供應商,今天推出一款面向軟件定義無線電(SDR)應用的革命性解決方案。新型AD9361

2013-10-23 18:16:25 2633

2633 AD9361是面向3G和4G基站應用的高性能高集成度的射頻(RF)捷變收發器(Agile Transceiver),集成了12位ADC和DAC,支持TDD和FDD.該器件的可編程性和寬帶能力使其成為

2014-04-25 10:43:31 5644

5644 魔鏡魔鏡,AD9371和AD9361嗎,誰更牛?

2017-09-27 09:52:22 36549

36549 在窄帶應用中,零中頻軟件無線電芯片已經非常流行,其代表是ADI公司的AD9361。

2023-05-26 10:17:41 1643

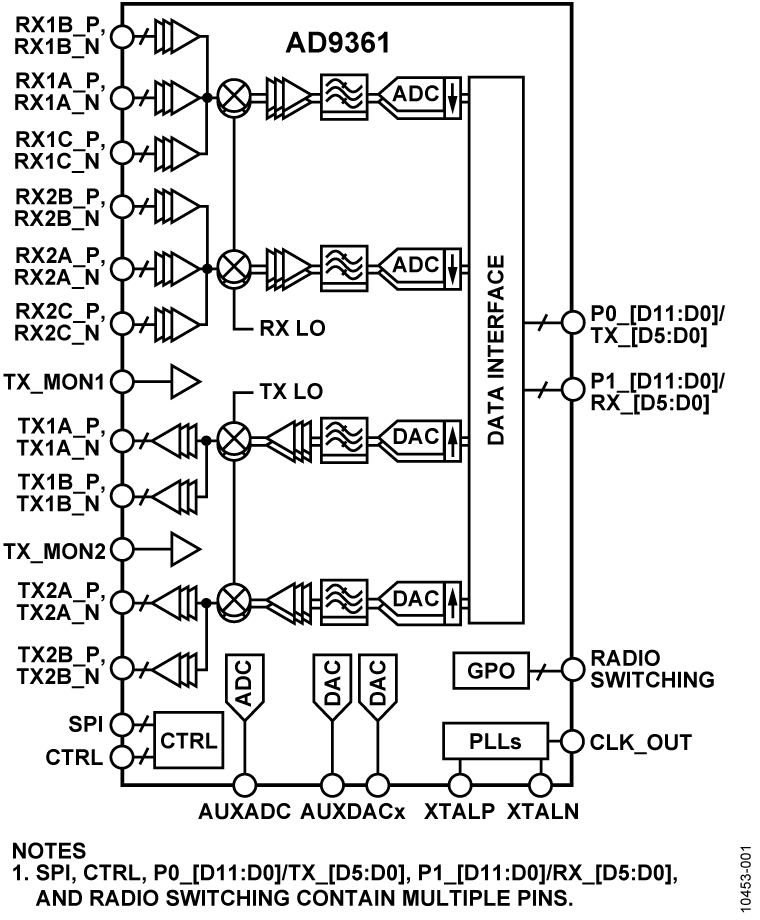

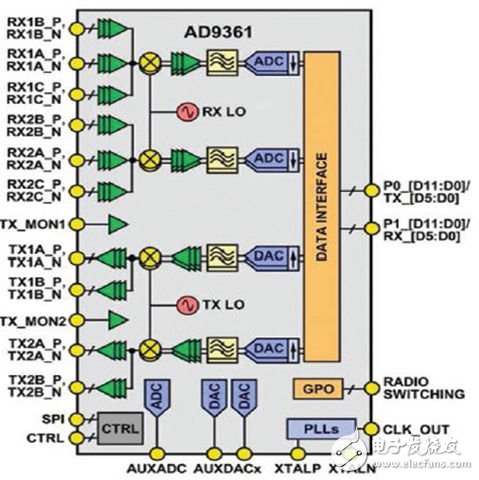

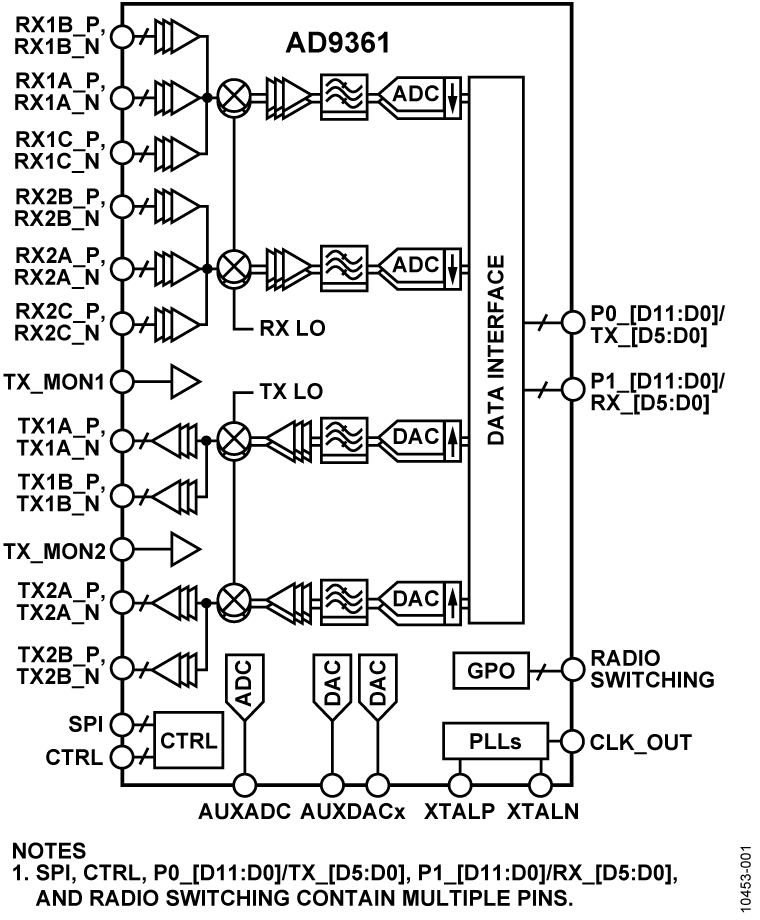

1643 AD9361和AD9371系列均使用零中頻(亦稱為zero-IF或ZIF)架構實現極高的集成度并顯著減少系統中頻率相關組件的數量。如圖1中的AD9371功能框圖所示,主接收信號路徑和主發送信號路徑使用一個復數混頻器級,在以本振 (LO) 頻率為中心的射頻 (RF) 和以直流為中心的基帶之間進行轉換。

2019-09-23 08:13:00 8961

8961

最近調AD9361芯片,同樣的配置,txpll鎖定了,RXpll鎖定不了,一直查不出原因,有沒有遇見過類似問題的同伴,討論一下

2018-12-11 10:02:42

我在使用AD9361的時候遇到一個問題,接收端設置本振頻率為2.4G,使用信號源產生2.4005GHz的正弦波信號輸入給AD9361,輸入信號功率從0下降到-30dBm的時候,AD9361采集的數據

2019-02-26 12:51:23

AD9361 BIST功能驗證相關事項想請問各位大拿,AD9361 BIST功能驗證是用于驗證收發通道的鏈路部分,而數據接口部分是不是驗證不到?當前調試過程中出現的問題是:配置模式FDD 1R1T

2021-09-14 22:29:00

AD9361采用官網zynq7000 no os版本驅動程序進行配置,芯片初始化完成,并且寄存器回讀正確,配置AD9361在FDD模式下工作,ad9361有載頻信號輸出,但是通過FPGA輸出數字正弦波信號至AD9361數字端,AD9361模擬端沒有任何輸出,只有載頻,請問大神們這是什么原因啊?

2019-01-14 09:10:54

用SPI 配置AD9361,不知道SPI是否寫成功?SPI讀回來全是1,用示波器探頭點著SPI_DO,讀回來就變變成了全0,SPI寫時序是正確的。上電后,沒有配置之前有哪些方法可以判斷AD9361是正常的?

2019-02-19 14:14:07

應該有正常的接收信號輸出。但是,從fpga抓到的信號仍為全零。將程序在其他硬件平臺移植,有ad采集信號。測試9361的接收端供電電壓也正常,沒有壓降。結合考慮,定位9361的芯片部分損壞,ad采集功能失效。問下大家,這是ad9361芯片的問題嗎?

2019-07-31 11:05:16

AD9361芯片我想輸出clock out 但是始終是一個高電平 哪位大神幫我解決一下

2022-04-11 16:55:49

大家好,我現在調試AD9361,手寫FPGA程序進行配置,使用AD936x Evaluation Software Version 2.1.1產生初始化腳本。 測試情況如下: 1) 數字接口驗證

2018-08-22 09:19:41

AD9361初始化過程中會做BB DCOFFSET 、RF DC Offset 的校正,發現并不能把直流校干凈,不知道該如何完成殘留的直流校正。我做了測試來看初始化后的DC校正情況:用信號源發單音信號

2018-07-31 12:16:53

您好!最近在用zedboard調試AD9361,已經按照no-os driver知道初始化AD9361; 1.調試AD9361發送通道的時候,沒有在程序里面找到自帶了一個1M正弦波的信號?2.如果我

2019-01-11 13:42:04

端口間的時序關系,但是該文檔上又有明確說明支持TDD lvds。2:我發現在TDD lvds模式下,將常數發送至P0,P1端口,ad9361工作在Tx狀態下,RF port輸出載波產生兩種幅度狀態,并且不定期切換,十分疑惑。請專家協助分析,謝謝。

2018-12-27 09:43:00

、pi/4 DQPSK、 16QAM、64QAM; 2. AD9361在較好的接收強度下(-30dBm上下)接收; 3. FPGA直接實時繪制接收的IQ圖,以此來查看(AD9361出來為零中頻復信號

2018-08-20 07:43:42

大家好!我在使用AD9361做信號接收的過程中第一次RF DC OFFSET 校準可以通過,更改本振后再次進行RF DC OFFSET 校準,校準一直通不過!求助!

2018-10-16 08:34:26

AD9361在1R1T傳輸時,當RX_FRAME和TX_FRAME信號為高電平時(即電平模式),AD9361數據收發并口傳輸時序圖? 數據手冊中并口的timming使用的是pulse mode,電平模式的timing沒有看到,我從哪里可以找到相應的時序圖。 謝謝!

2018-12-19 09:25:01

ad9361無發射信號求助,硬件平臺為ettus公司的軟件無線電開發板USRP B210,配置軟件是通過調用ADI官網提供的配置function來實現。1、ad9361工作于FDD模式,數據端口為

2019-01-08 13:57:12

TX1通道接到頻譜儀上沒有任何的信號輸出 AD9361我配置的是單通道、LVDS輸出,DATA_CLK,FB_CLK也都有輸出,數字接口部分我參照AD9361的IP核編寫的TX_FRAME時序

2018-09-25 14:19:38

,ad9361配置為lvds全雙工模式,fdd模式。請問該查看哪些寄存器? 軟件配置完芯片后我就將芯片的ensm置于fdd(發射)狀態,應該這樣做 么?

2019-02-26 10:32:58

我配置完AD9361后,只用來發送數據。在半雙工 TDD SDR模式下10M采樣率發送QPSK,16QAM,64QAM,256QAM的數據,連接到頻譜儀上,通過VSA 89600看星座圖,能看出大致

2018-12-19 09:30:21

的選項。 我們必須添加定制電源、RF前端、功率檢測、PLL等,但關鍵是,如果我們可以訪問發射和接收兩個數據流的I端和Q端,那么AD9361會處理需求中最困難的部分。 是否有選項可以復用芯片的I端和Q

2019-03-05 14:25:52

在ad9361的demo軟件配置里面設置adc_clk dac_clk必須是相等或者2倍的關系,請問可以設置成其他倍數關系么?我看到datasheet里面描述應該可以任意分頻,難道必須遵守這個原則

2018-08-20 07:25:59

AD9361設置的Rx RF PLL有頻偏,比如設置中心頻率是5770MHz,測出來的中心頻率是對的,但是設置中心頻率為5771MHz,測出來的中心頻率為5741MHz

2019-07-31 18:03:02

目前正在調試AD9361,然后發現在用3f4進入測試模式的時候有波形顯示,然后關閉3f4,輸出和輸入都無波形。并且在下載程序后一瞬間可以看到示波器有正弦出現。然后我用的是12\'fhhh配置的單音信號

2023-12-06 06:38:42

用FPGA控制AD9361,采樣頻率設為30Mhz,但采樣時鐘在FPGA中是60MHz,產生信號頻率諧波大,是啥原因

2019-07-31 19:21:15

說到SDR應用,你想到的是什么?是ADI的AD9361嗎? AD9361被稱為SDR應用的革命性解決方案,自發布以來就受到廣泛的關注。作為中文技術論壇上被網友提及最多的產品,你們可曾提出這樣一個

2018-08-23 14:58:57

各位大佬好,我最近在調試ad9361,試了一下輸出一個480k的頻率,載波頻率是2250.5M,上變頻后頻率應該是2250.5M+-480k,但是在頻譜儀上看到他的載波頻率還是很高,按照

2023-11-01 14:29:46

AD9361BBCZ寬帶收發器產品介紹產品名稱:寬帶收發器產品型號:AD9361BBCZ AD9361BBCZ特征集成12位DAC和ADC的RF 2 × 2收發器TX頻段:47 MHz至6.0 GHzRX頻段:70 MHz至6.0 GHz支持TDD和FDD操作可調諧通道帶寬:

2019-07-26 09:05:51

;

3.通過SDR配置RX_clk=40MHz,工作帶寬為20MHz;

4。enable、txnrx、resetb均置為“1”;

測試結果如下:

1、rx_clk=40MHz正常,AD9361自測通過(相應

2023-12-07 07:35:03

有沒有大神進行FPGA和AD9361的通信配置。現在我看了AD9361的英文手冊,寄存器手冊仍在進行當中。因為不是做通信的,所以比較迷糊,感覺初始化配置如果想自己寫都非常的復雜。手里有AD9361

2016-08-01 09:31:21

,AD9361非常合適作為無線電監測的前端設備,可以監測超寬頻段、不同帶寬的無線電信號。 集成12位DAC和ADC的RF 2×2捷變收發器AD9363AD9363 RF收發器是針對各種低功耗無線應用而設

2018-08-16 00:37:12

的超寬頻率范圍,支持通道帶寬最大可達56MHz。 AD9361是RadioVerse生態系統中的第一款寬帶收發器,結合了射頻前端和混合信號基帶部分,還集成了頻率合成器,并給處理器提供可配置的數字接口

2019-09-17 01:18:57

Wi-Fi和RF捷變收發器在寬帶無線應用方面的優缺點使用FPGA和AD9361/AD9364解決方案實現高清無線視頻傳輸的關鍵參數

2021-03-10 07:13:45

傳統的射頻收發器硬件架構由分立的LNA,Mixer,VGA,ADC/DAC,IQ調制器和射頻頻綜等芯片組成。AD9361是一款面向3G和4G基站應用的高性能、高集成度的射頻RF

2018-04-09 19:41:03

目前我使用兩塊AD9361,兩塊AD9361已經進行了BBPLL同步,采用閉環采集數據。當我第一塊AD9361發送點頻信號時,第二塊AD9361接收的數據PRT長度與第一塊AD9361發送的PRT

2018-08-17 06:06:13

生態系統。AD9361集成式雙通道寬帶收發器IC AD9361是一款用于SDR架構的高性能、高度集成的RF收發器IC,適合無線通信基礎設施、防務電子系統、RF測試設備和儀器,以及通用軟件定義無線電

2018-10-22 10:29:31

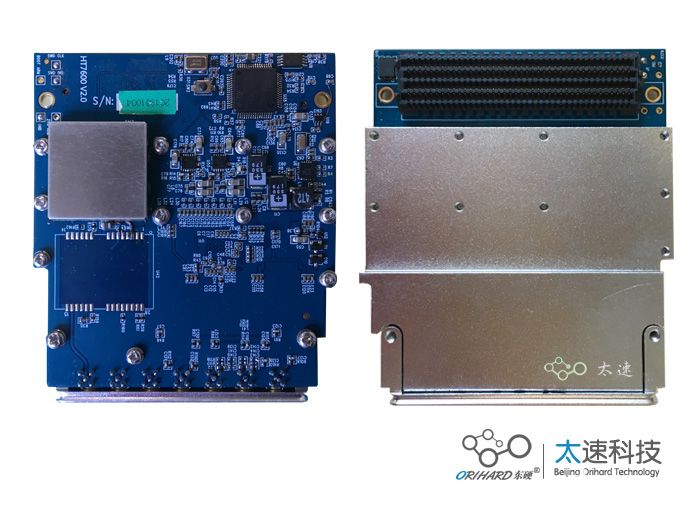

最近自己設計了一套低成本的基于AD9361的SDR商用平臺,調試難度和體積功耗等確實降低了很多。軟硬件開源,算是為社區做貢獻吧。詳情如下文。 AD9361作為ADI主打的RFIC,本人已經在

2018-12-21 11:37:50

傳輸,如無人飛行器 (UAV) 應用。本文將剖析使用AD9361/AD93642,3集成式收發器IC實現寬帶無線視頻信號鏈的過程,以及傳輸的數據量、相應的RF占用信號帶寬、傳輸距離和發射功率。文中還將

2019-07-02 04:20:26

,但在最終電腦板占用空間、重量、功耗和成本方面的代價非常高。 高性能單芯片模擬前端解決方案 捷變收發器是平臺解決方案產品系列的其中一款產品,該系列包括AD9364 RF收發器IC. AD9361

2018-11-12 16:01:37

一種基于混合信號RF IC的寬帶SDR設計方案

2021-05-24 06:40:41

我在使用AD9361的時候遇到一個問題,接收端設置本振頻率為2.2G,使用信號源產生2.201GHz的正弦波信號輸入給AD9361,輸入信號功率從0dBm下降到-30dBm的時候,此時寄存器中

2018-08-17 07:39:54

您好,我現在在配置AD9361,使用的FPGA是Xilinx VC707,主要是完成LTE信號的接收。之前沒有相關配置經驗,麻煩問下配置AD9361是通過什么軟件配置的?在哪里可以下載到?配置的代碼哪里可以找到?或者可以給我提供相關的配置資料嗎?萬分感謝!

2018-09-17 15:26:26

設計一個三通道的信號源,作為類似噪聲源或簡單波形信號源使用,大體思路是用FPGA產生基帶的碼型數據,然后接入AD9361(AD9364)的數據端口(p0/p1),在AD9361(AD9364)內部

2018-09-10 10:08:08

AD9361提供了Fast Attack AGC模式,但是用默認的參數,無法在收到一幀信號后的4us內把增益鎖定住。 因為WiFi信號是以幀為單位突發傳輸的,因此我需要在AD9361接收到WiFi幀

2018-09-03 14:49:01

請問基帶信號只有1路,送至AD9361的i路,q路寫0,發現AD9361接收到的IQ兩路信號有時變的偏置,不知為何?

2018-08-27 11:24:43

@1>根據你們ad9361開發板的參考設計,我想問這個開發板能支持wifi/bt/fm/gps/lte 這些射頻協議開發嗎? 即:我們在在fpga里做基帶,通過配置ad9361來支持不同的rf信號 2> 如果要支持上述協議,還需要添加額外電路嗎?

2018-09-06 11:36:32

我在配置A9361的時候被難在了AD采樣上面。我按照給的寄存器配置順序配置的AD9361,發射已經OK。接收可以接收到信號,但是接收在沒有信號的時候總是有很大的一個干擾信號在里面。我的基帶采樣率為

2019-03-01 10:10:19

請問一下,使用AD9361的fastlock模式,怎么判定、測試信號穩定的時間?常規模式下,可以檢測247[D1]進行檢測,但使用fastlock模式,調用profile實現調頻,我檢測247[D1]始終為1,所以請問在fastlock模式下,我該如何判定信號已經穩定?謝謝@

2018-08-22 10:24:42

想用一片AD9361同時發射2.4GHz和400M兩路信號,可是發現兩個發射通道共用一個LO即共用一個PLL。查看了AD9361RF and BB PLL SynthesizerUser Guide

2018-12-18 09:18:58

你好,我想問一下,AD9361能加到高通的手機芯片平臺上工作嗎?即在Android系統下是否能工作,不帶FPGA,讓AD9361和高通的手機芯片直連。

2018-07-31 08:46:59

ad9361的ensm控制中,芯片設置為FDD模式。我認為只有在ensm狀態機置于fdd狀態時,才能發射信號,而其他狀態都沒有載波信號。但是這樣的我該怎么理解flush狀態呢,flush的作用

2018-09-18 09:56:54

ad9361 接收rf 傳給BB 的信號是中頻還是零頻?

2019-02-27 06:17:49

ad9361接收通道將信號通過正交調制下變頻變為I,Q兩路數據。信號傳播需要時間,這就造成了在接收端信號形式中有一個附加相位問題。就需要本振產生的載波同步。這里我有一個問題,就是本振產生的載波相位同步問題怎么解決?ad9361可以自動實現載波同步嗎,還是我通過FPGA自己處理,實現載波同步?

2018-08-22 09:02:46

如何將多片AD9361芯片進行相位同步,技術文檔有說通過sync管腳進行MCS同步,但是僅僅只針對數據時鐘完成同步。個人理解數據相位主要由RF混頻處理以及后續數字處理決定,通過sync管教能夠完成

2018-12-25 11:42:25

如果我想驗證一下ad9361的電路設計和寄存器配置是否合理正確,需要怎樣測試來驗證其性能達到芯片數據手冊上的指標?

2018-10-01 09:15:51

1,AD9361芯片有沒有上電時序要求,如果有是怎么樣的,哪里可以找到相關說明?2 ,如何知道AD9361狀態轉換時間?比如:在TDD模式下,芯片IDLE->RX,RX->TX

2018-10-09 16:06:25

和寬帶功能使其成為各種收發器應用的理想選擇。該器件將RF前端與靈活的混合信號基帶部分和集成頻率合成器相結合,通過為處理器或FPGA提供可配置的數字接口簡化了設計

2019-07-04 14:15:44

器件集RF前端與靈活的混合信號基帶部分為一體,集成頻率合成器,為處理器提供可配置數字接口,從而簡化設計導入。AD9361接收器LO工作頻率范圍為70 MHz至6.

2023-11-03 10:37:57

AD9361 Datasheet 射頻芯片中的佼佼者 性能很好

2016-06-06 10:29:29 0

0 射頻捷變頻收發器AD9361發布以來,引起業界的持久、廣泛的關注——一流的性能、高集成度、寬帶工作能力和靈活性,設計用于可編程無線電應用、適用于各種調制方案和網絡規格,70 MHz至6 GHz的頻率

2017-02-08 17:47:11 539

539

PicoZed SDR? 開發套件捆綁了啟動軟件定義無線電 ?(SDR)? 設計所需的一切。 ? 該套件包含穩健的低功耗小型 ?PicoZed SDR Z7035/AD9361 SOM

2017-02-08 20:37:00 487

487 AD9361是analog devices公司推出的高度集成化的寬帶零中頻收發調制解調芯片,經過筆者的實踐使用發現,用此芯片完全能滿足產品及的開發設計,由于內置了上下變頻器,和數字濾波器以及模擬

2017-09-13 14:32:44 196

196 Analog Devices, Inc. (NASDAQ:ADI)新推出的面向軟件定義無線電(SDR)應用的革命性解決方案--AD9361,是一款高性能、高度集成的RF Agile

2017-12-05 17:33:01 699

699 Analog Devices, Inc. (NASDAQ:ADI)新推出的面向軟件定義無線電(SDR)應用的革命性解決方案--AD9361,是一款高性能、高度集成的RF Agile Transceiver?捷變收發器。

2018-05-07 15:14:00 5501

5501 AD9361射頻捷變收發器概述,包括從RF到基帶的RX和TX信號路徑、自動增益控制(AGC)、RF PLL和本振(LO)生成。

AD9361射頻捷變收發器概述:http

2018-06-05 13:45:00 8061

8061

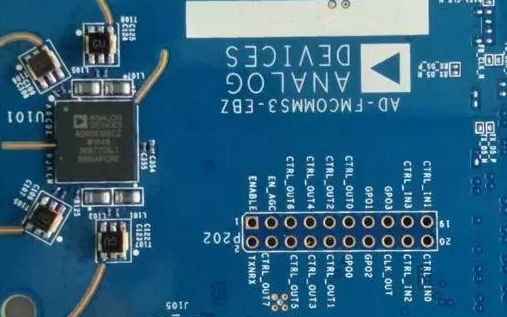

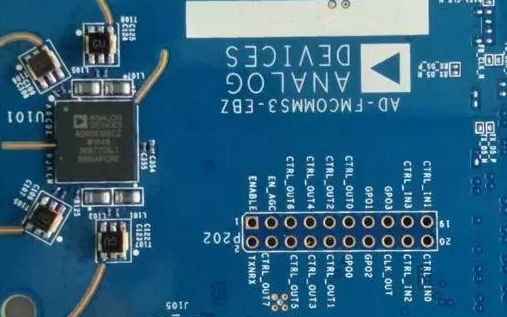

了解革命性的AD9361 RF捷變收發器,一款面向SDR應用的完整無線電設計。該收發器擁有一流的性能,超高的集成度,支持寬帶模式,以及卓越的靈活性,并受到AD-FMCOMMS2-EBZ-FMC板的支持。

2018-06-04 01:47:00 5629

5629

AD9361是一種高性能、高集成度的射頻(RF)收發器,用于3G和4G基站應用。它的可編程性和寬帶能力使它成為廣泛的收發器應用的理想選擇。該裝置將RF前端與靈活的混合信號基帶部分和集成頻率合成器

2018-08-14 08:00:00 24

24 電子發燒友網為你提供ADI(ti)AD9361相關產品參數、數據手冊,更有AD9361的引腳圖、接線圖、封裝手冊、中文資料、英文資料,AD9361真值表,AD9361管腳等資料,希望可以幫助到廣大的電子工程師們。

2019-02-22 15:33:34

本視頻討論無線電設計的一些挑戰,并對照AD9361,介紹第二代寬帶RF集成收發器AD9371。

2019-07-30 06:12:00 2632

2632 發表評論來自AD9361 RF????????????。 AD9361 RF??????????????????,????????????????????AD-FMCOMMS2-EBZ-FMC??????????。

2019-07-30 06:02:00 2589

2589 概要瞭解AD-FMCOMMS2-EBZ-FMC板,一款針對新型AD9361 RF收發器的支援生態系統。該快速原型製作環境支援多種通訊協定,可使上市時間從幾個月縮減到幾天。

2019-07-29 06:07:00 2129

2129 AD-FMCOMMS[234]-EBZ卡是一款高速模擬FMC模塊,旨在展示AD9361或AD9364——一款高性能、高度集成的RF捷變收發器,設計用于RF,如3G和4G基站以及SW軟件定義無線電。

2019-07-29 06:02:00 5811

5811 商用航空器利用ADS-B發射機報告其信息。 本視頻討論如何利用一個基于AD9361的接收機平臺來捕捉ADS-B信號,然后利用MATLAB和Simulink開發一個能夠解碼消息的算法。

2019-07-17 06:19:00 4014

4014 概要了解AD-FMCOMMS2-EBZ-FMC板,一款面向新型AD9361 RF收發器的配套生態系統。該快速原型制作環境支持多種通信協議,可使上市時間從幾個月縮減到幾天。

2019-07-12 06:14:00 2764

2764 了解革命性的AD9361 RF捷變收發器,一款面向SDR應用的完整無線電設計。該收發器擁有一流的性能,超高的集成度,支持寬帶模式,以及卓越的靈活性,并受到AD-FMCOMMS2-EBZ-FMC板的支持。

2019-07-12 06:05:00 2922

2922 AD9361射頻捷變收發器概述,包括從RF到基帶的RX和TX信號路徑、自動增益控制(AGC)、RF PLL和本振(LO)生成。

2019-06-28 06:02:00 3992

3992

AD9361是一款面向3G和4G基站應用的高性能、高集成度的射頻(RF)Agile Transceiver?捷變收發器。該器件的可編程性和寬帶能力使其成為多種收發器應用的理想選擇。該器件集RF前端與靈活的混合信號基帶部分為一體,集成頻率合成器,為處理器提供可配置數字接口,從而簡化設計導入。

2019-06-20 06:15:00 2959

2959 瞭解革命性的AD9361 RF捷變收發器,一款針對SDR應用的完整無線電設計。該收發器擁有一流的性能,超高的整合度,支援寬頻模式,以及卓越的彈性,並受到AD-FMCOMMS2-EBZ-FMC板的支援。

2019-06-05 06:14:00 2485

2485 使其成為多種收發器應用的理想選擇。該器件集RF 前端與靈活的混合信號基帶部分為一體, 集成頻率合成器,為處理器或FPGA 提供可配置數字接口,從而簡化設計導入。AD9361 芯片工作頻率范圍為70 MHz 至6GHz,涵蓋大部分特許執照和免執照頻段,通過對AD9361 IC 編程

2020-08-12 16:03:28 98

98 Lekha Wireless, Venus LTE L3 relay application; Featuring AD9361

2021-01-30 12:05:17 1

1 AD9361芯片工作頻率范圍為70 MHz至6 GHz,涵蓋大部分特許執照和免執照頻段,通過對AD9361自身可編程改變采樣速率、數字濾波器和抽取參數,使該芯片支持的通道帶寬范圍為低于200 kHz到56 MHz。

2021-03-09 11:47:51 5377

5377 AD9361:RF捷變收發器

2021-03-19 10:44:30 32

32 應用的高性能、高集成度的射頻(RF)Agile Transceiver捷變收發器。該器件的可編程性和寬帶能力使其成為多種收發器應用的理想選擇。該器件集RF前端與靈活的混合信號基帶部分為一體,集成頻率合成器

2021-06-07 14:34:43 5409

5409

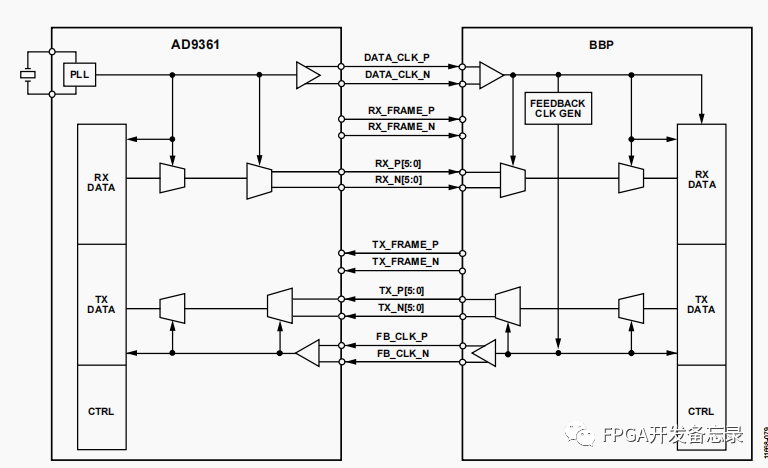

本文通過以高速AD9361芯片為例進行數據接口邏輯代碼的編寫,利用SelectIO IP快速高效完成芯片驅動的生成。

2022-07-01 09:59:15 4166

4166 ,廣泛適合于SDR(無線電軟件),移動基站,WiFi,無線局域網,專用或通用無線電設備等應用。設計者通過使用FMC177,可以有效簡單的使用AD9361芯片。

2023-01-29 10:42:58 583

583

AD9361是一款高性能、高度集成的射頻(RF)捷變收發器?,設計用于 3G 和 4G 應用。AD9361的可編程性和寬帶能力,特別是其通道帶寬范圍從小于200 kHz到56 MHz,功耗低,使其

2023-02-23 15:16:50 2070

2070

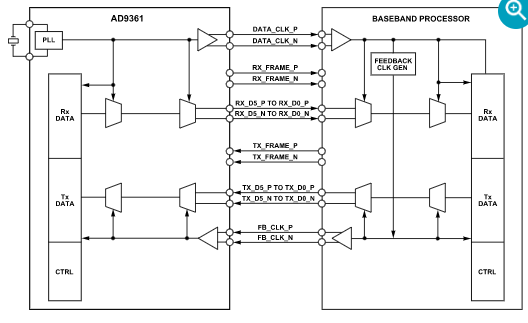

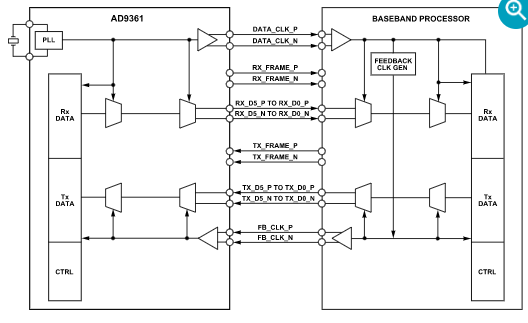

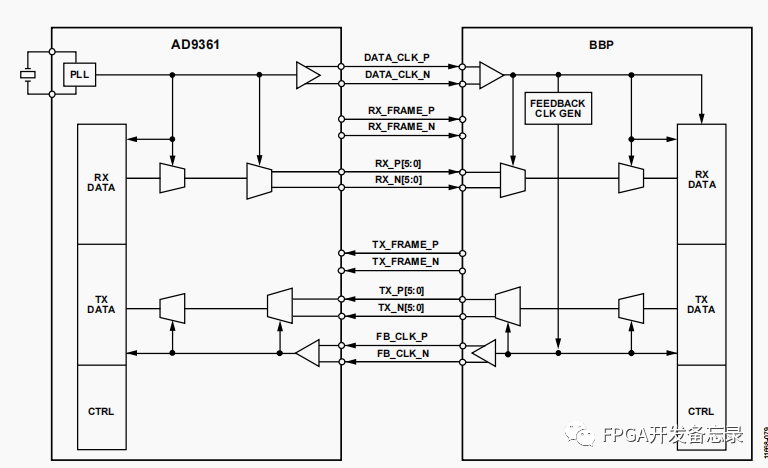

接下來將介紹AD9361數據路徑在低電壓差分信號(LVDS)模式下運行。AD9361數據接口使用并行總線(P0和P1)在AD9361和BBP之間傳輸數據樣本。

2023-04-25 15:51:25 3925

3925

AD9361接收機LO的工作頻率范圍為70 MHz至6.0 GHz,發射機LO工作頻率范圍為47 MHz至6.0 GHz范圍,涵蓋大多數授權和未授權頻段。頻道支持小于200 kHz至56 MHz的帶寬。

2023-05-16 14:28:31 592

592 在4G微基站產品開發中,工程師須選用一SDR收發機,要求:支持TDD、FDD雙網絡制式、兼容AD9361,國產廠牌優先。國芯思辰提到了地芯科技GC0801,在滿足開發雙網絡制式需求的同時可以做到硬件

2022-11-07 10:20:58 563

563

AD9361是一種寬頻帶軟件可定義收發器芯片,由ADI(Analog Devices Inc.)公司研發,可用于各種射頻(RF)應用。它是一種全集成的射頻收發器,實現了收發器功能。在這篇文章中,我們

2023-12-26 15:49:35 770

770 AD9361是一款高性能的射頻前端芯片,廣泛應用于無線通信系統中。其中一個重要特性是其具有靈活可調的ADC采樣率。本文將詳細介紹AD9361的ADC采樣率設置范圍,包括其相關特性、設置方法以及在實際

2024-01-04 09:37:57 904

904

電子發燒友App

電子發燒友App

評論