根據最新資料顯示:將超導和光取樣技術應用于A/D變換器已成為未來的發展趨勢。具有突破性的一項技術是“快速單通量”RSFQ 技術。該技術基于超導基本量子機械特性,說明了離散的量化形式中存在著磁通。在該技術中,單磁通量子脈沖代表二進制值。因為一個完整的單磁通量子代表一個脈沖,所以這種技術的性能受到輸入信號最大轉速率的嚴格限制。因此可以通過對處理速度與分辨率進行折衷的方法來達到最佳技術性能。在一個重復取樣的基于超導A/D變換器中,孔徑抖動的影響會大減少,使超寬頻段工作已切實可行。而且在這樣的A/D變換器中,其輸入端的取樣速率與輸出端不同,其內部的可編程抽取器可根據比特數和帶寬進行折衷來設置。

基于超導技術的A/D變換器另一個重要特性是高靈敏度。驅動單磁通量子電路所需的最小功率是1mW,即比高速半導體A/D變換器所需的1 mW小了三個數量級。這一特性加上高取樣速率最終可使系統無需使用低噪聲放大器LNA ,并可直接在天線端取樣,由此可以得到更高的系統增益。盡管超導A/D變換器與半導體A/D變換器相比,在性能上還沒有顯著的優越性,但主要的技術精華還是非常有前途的。目前工作于19.6Gltz頻段的超導A/D變換器已有演示。

在光取樣A/D變換器中,取樣與量化功能分別是在光域和電子域中完成的。光取樣A/D變換器的主要優點在于模式鎖定激光源的定時抖動小。目前已報道,信噪比SNR 為51dB的光取樣A/D變換器就相當于速率為505Mss,有效分辨率為8.2比特的傳統半導體A/D變換器。在不遠的將來,通過進一步的改進,預計可以實現取樣率達到數GHz且具有12比特分辨率的光取樣A/D變換器。另外,鎖定在10GHz激光模式已實現了光時鐘脈沖的產生,每3ps3皮秒 寬脈沖的定時抖動為16fs0.016% , 幅度抖動為0.058%。這些標準的抖動值可使光取樣率在10Gss時,精度達到11比特。

下面對不同的A/D變換器技術進行了比較:(其中,超導A/D變換器分辨率位數和速率都不是固定的值,可以進行折衷,以達到所期望的性能。)

目前D/A的發展水平是:高精度D/A16bits 5MSPS,高速度D/A14bits 1GSPS,速度和精度兼顧D/A 14bits 300MSPS。D/A技術可用變換器,還需要高速存儲器,現在集成電路技術的發展已有1ns的砷化嫁RAM商品,但將大量砷化嫁RAM用到任意波形發生器上顯然價格過高,而且也消耗大量功率,比較經濟的做法是用多路轉換的方案,允許波形存儲在相對低速的COMSRAM。

DSP是限制軟件無線電發展的瓶頸問題,其數據處理速度和精度直接關系到軟件無線電臺能否實現。目前采用的技術方案主要是數字信號處理技術DSP 、專用集成電路ASIC 、現場可編程門陣列FPGA 以及這幾種技術的結合。高速DSP芯片是軟件無線電的核心部分。隨著微電子技術的發展,數字信號處理器件在速度和性能上有了很大的提高。2003年TI推出了業界速度最快的三款新型720MHzDSP,該速度打破了TI自己保持的600MHz全球最快速度DSP的記錄,打破了性能極限。這些DSP的指令執行速度超過了5700HIPS,適用于下一代無線基礎設施、數字視頻、電信設備和成像應用。TI推出的另一款DSP,其速度達到1GHz。據悉,目前最快的芯片處理速度已達到10GFLOPS,但在性價比、功耗上仍很難滿足要求。為解決這一問題,采用了一種RISC精簡指令集計算 結構,這種結構的優點是尺寸小、功耗低、性能高。各DSP廠商紛紛采用新工藝,改進DSP芯核,并將幾個DSP芯核、MPU芯核、專用處理單元,外圍電路單元、存儲單元統統集成在一個芯片上,成為DSP系統級集成電路。

FPGA是可重編程器件,所實現的功能大大超過今天的DSP微處理器,包括實現軟件的可編程性、高速的硬件,并可實時重構。事實上,FPGA是真正的 “軟”硬件,能在定制硬件和靈活的全軟件方案之間折衷。近年來FPGA無論是在規模、處理速度還是功耗上,都得到了長足的進步。FPGA器件的集成度已達到上千萬門,系統工作頻率達到幾百MHz。高端FPGA的時鐘頻率已高達250MHz,可提供25G次MAC的性能。

由于大規模FPGA既有傳統FPGA運算速度快、功耗低的優點,又具有可動態配置的靈活性,在軟件無線電中將發揮重大的作用,主要表現在:

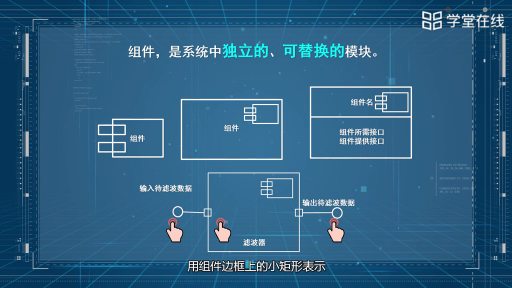

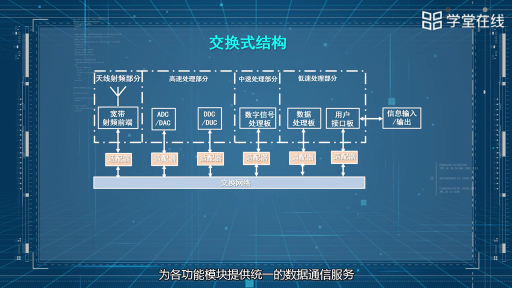

●主要完成軟件無線電臺內部的數據處理、調制解調和編碼解碼等工作 由于電臺內部數據流量大,進行濾波、變頻等處理運算次數多。必須采用高速、實時、并行的數字信號處理器模塊或專用集成電路才能達到要求。要完成這么艱巨的任務,必須要求硬件處理速度很高,芯片容量大,同時要求進行針對處理器算法的優化和改進。只有這樣,才能實現電臺內部軟件的高速運行以及多種功能的靈活切換和控制。對于一些固定功能的模塊如濾波器、下變頻器等,可以用具有可編程能力的專用芯片來實現,而且這種芯片的處理速度要高于通用DSP芯片。

利用FPGA可以同時滿足速度和靈活性兩方面的要求,支持軟件無線電中動態系統配置的功能。通常來說系統的分配方式是:計算密集型的部分在DSP內部完成;功能相對固定的部分,則由FPGA來完成。這樣,既可以滿足高速的數字信號處理器的要求,又可以實現對各種硬件的全方位配置。

●根據不同的標準,對理想的軟件無線電進行配置,并提供數字化終端

理想的軟件無線電是用A/D變換器對天線上的信號或中頻信號進行數字化,但數字化后的數據不只是靠軟件進行處理,而是利用各種靈活的、可重新配置的ASlC和通用數字信號處理器DSP 來縮減系統功耗、體積和成本。這些ASIC是可編程的,可以針對不同頻道的特性和調制方式進行調節。具體的實施方案包括現場可編程門陣列FPGA 或ASIC, 它們比完全靈活的DSP實施方案更為經濟。這些硬件模塊可以通過軟件進行選擇,用作不同系統的公用硬件。

另外,FPGA提供了“芯片上的系統” 特征。它包含了連續的收發技術、RISC處理器和一定數量的可編程存儲器,為軟件配置無線電信號處理提供數字化終端。

●同DSP組合,可以提供較大的可編程能力

可編程門陣列FPGA 在實際中的可編程性比ASIC高,但FPGA要受門的個數和連線多少的限制,當電臺在功能上需要擴展時,受門連接的限制,其可編程性要比DSP小。采用FPGA與DSP混合結構,具有較大的可編程能力。

●在軟件無線電系統中實現轉換、濾波等功能

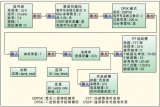

FPGA同DSP、FIR專用芯片、存儲器、I0接口組成可編程DSP模塊,用以實現x.25物理層中數據比特流的透明傳輸。按照不同的數據處理流程,DSP模塊的功能可劃分為:與終端的數據交換、自適應調制解調、信道環境分析和管理、自適應頻率估計選擇和校正、單邊帶SSB 調制解調、頻率交換等。整個DSP模塊在軟件無線電系統中通常用來滿足頻率變換和濾波的需求,實現轉換、濾波、擴頻、調制等功能。

電子發燒友App

電子發燒友App

評論