數(shù)字下變頻是無(wú)線(xiàn)通信鏈路層的重要組成部分,寬帶信號(hào)和窄帶信號(hào)的下變頻由于信號(hào)帶寬不同而抽取因子不同,使得同時(shí)具有寬帶和窄帶信號(hào)的系統(tǒng)采用基于FPGA的系統(tǒng)很難實(shí)現(xiàn)。本文提出采用專(zhuān)用數(shù)字下變頻率芯片GC5016同時(shí)實(shí)現(xiàn)寬帶和窄帶信號(hào)的變頻;采用FPGA實(shí)現(xiàn)對(duì)寬/窄帶數(shù)據(jù)的接收和存儲(chǔ),存儲(chǔ)后數(shù)據(jù)使用高性能DSP芯片C6455實(shí)現(xiàn)對(duì)這些數(shù)據(jù)的處理。文中詳細(xì)介紹了該系統(tǒng)的軟硬件設(shè)計(jì)方法。

引言

隨著電子技術(shù)和信號(hào)處理技術(shù)的發(fā)展,寬帶數(shù)據(jù)的應(yīng)用越來(lái)越多,同時(shí)窄帶數(shù)據(jù)通信也仍然廣泛存在。同時(shí)對(duì)寬帶和窄帶數(shù)據(jù)進(jìn)行處理是目前無(wú)線(xiàn)通信遇到的問(wèn)題。由于數(shù)字接收機(jī)系統(tǒng)中,寬帶和窄帶數(shù)據(jù)的需求不是事先固定的,而是在信號(hào)分析和識(shí)別后,自適應(yīng)地或者由用戶(hù)現(xiàn)場(chǎng)下發(fā)命令,實(shí)現(xiàn)寬帶或者窄帶信號(hào)的監(jiān)測(cè)。 在這種應(yīng)用背景下,基于FPGA的數(shù)字下變頻就面臨現(xiàn)場(chǎng)編程問(wèn)題,一般FPGA解決方法是將各種帶寬的參數(shù)存儲(chǔ)在其FLASH芯片中,隨時(shí)根據(jù)命令來(lái)調(diào)用 不同帶寬下的工作參數(shù),但需要的存儲(chǔ)空間較大,占用FPGA的資源也較多,基于此方法設(shè)計(jì)的系統(tǒng)需要大容量的FPGA芯片,系統(tǒng)的功耗較大,價(jià)格較高。

為此,本文提出一種基于專(zhuān)用數(shù)字下變頻芯片GC5016的寬/窄帶數(shù)據(jù)下變頻解決方案,使用小規(guī)模FPGA實(shí)現(xiàn)對(duì)GC5016輸出數(shù)據(jù)的讀取和存儲(chǔ),應(yīng)用高性能DSP芯片C6455實(shí)現(xiàn)對(duì)下變頻后數(shù)據(jù)的分析和解調(diào)。

1 GC5016及其結(jié)構(gòu)

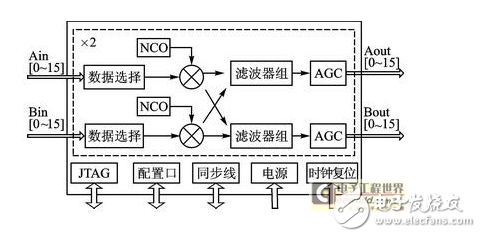

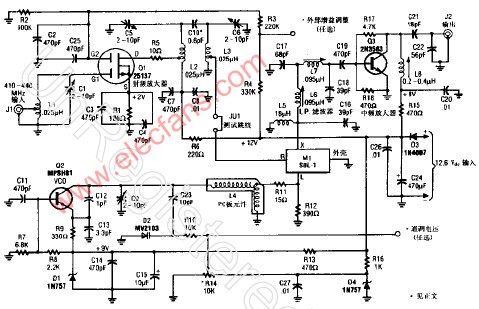

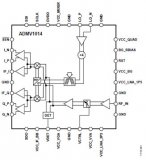

GC5016是TI公司推出的寬帶4通道的可編程數(shù)字上下變頻器,提供160 Msps輸入速率,可以采用雙通道聯(lián)合處理最高320 Msps的輸入速率,滿(mǎn)足目前絕大部分A/D器件的速率要求。4個(gè)完全相同的通道可以獨(dú)立配置成上變頻、下變頻或兩個(gè)上變頻、兩個(gè)下變頻的組合通道。本文 主要介紹其下變頻功能。GC5016的內(nèi)部結(jié)構(gòu)如圖1所示。圖中給出了GC5016在接收工作模式下的結(jié)構(gòu)圖,其內(nèi)部有4個(gè)通道,圖中給出了A和B兩個(gè)通 道的結(jié)構(gòu)圖,通道C和D具有和這兩個(gè)通道完全一致的結(jié)構(gòu)。

圖1 GC5016內(nèi)部結(jié)構(gòu)圖

輸入數(shù)據(jù)經(jīng)過(guò)數(shù)據(jù)選擇單元進(jìn)入混頻器,數(shù)據(jù)選擇格式有定點(diǎn)16位、浮點(diǎn)16位以及AB雙路合成數(shù)據(jù)3種格式。數(shù)字混頻器將按照軟件配置對(duì)信號(hào)進(jìn)行混頻,為了便于后面的濾波,一般轉(zhuǎn)換到零頻為中心的基帶數(shù)據(jù)。基帶數(shù)據(jù)可以?xún)陕泛铣煞謩e經(jīng)過(guò)濾波器, 也可以每路單獨(dú)進(jìn)行濾波。濾波器組包括CIC濾波器和可編程濾波器:CIC濾波器可以實(shí)現(xiàn)1~256的整數(shù)抽取,降低了數(shù)據(jù)速率;可編程濾波器一般使用 FIR濾波器,對(duì)信號(hào)進(jìn)一步抽取和整形,這里抽取可以為1~16,可見(jiàn)GC5016可以實(shí)現(xiàn)最大的抽取為4 096(16 256)。FIR濾波后的數(shù)據(jù)經(jīng)過(guò)AGC功率檢測(cè)和控制模塊,數(shù)據(jù)最后經(jīng)過(guò)輸出格式化后輸出。

圖中配置口是一個(gè)并行數(shù)據(jù)接口,必須經(jīng)過(guò)這個(gè)接口配置GC5016的寄存器,也可以通過(guò)配置口來(lái)讀取芯片的寄存器,查看芯片工作是否正常、初始化是 否正確等;GC5016具有一個(gè)同步輸入和同步輸出口,可以用于多個(gè)GC5016的同步,也可以用于單個(gè)芯片內(nèi)幾個(gè)通道的同步;JTAG口用于芯片的測(cè)試,用戶(hù)一般不需要連接;電源和時(shí)鐘復(fù)位接口是芯片正常工作的基本配置。

2 硬件系統(tǒng)設(shè)計(jì)

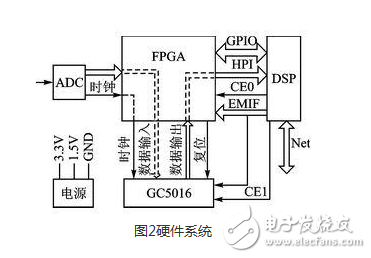

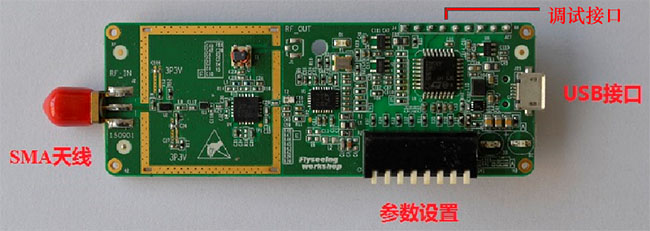

硬件系統(tǒng)主要由ADC、GC5016、FPGA和DSP組成,如圖2所示。

圖2 硬件系統(tǒng)

模/數(shù)轉(zhuǎn)換芯片ADC采用ADI公 司的16位芯片AD9467,其采樣頻率高達(dá)200 MHz,具有75 dB的SNR和90 dB的SFDR,是一款性能較高的高速ADC。其對(duì)外接口是差分LVDS數(shù)據(jù)和時(shí)鐘總線(xiàn),差分輸出不能直接連接到GC5016,需要采用FPGA將差分信 號(hào)轉(zhuǎn)換成單端信號(hào)。FPGA以ADC輸出的差分時(shí)鐘為基準(zhǔn)時(shí)鐘對(duì)差分?jǐn)?shù)據(jù)進(jìn)行讀取和轉(zhuǎn)換,將處理好的單端信號(hào)數(shù)據(jù)仍然在該時(shí)鐘基準(zhǔn)下輸出給GC5016。 由于FPGA的差分端口是相對(duì)應(yīng)的,因此連接ADC的差分?jǐn)?shù)據(jù)線(xiàn)和差分時(shí)鐘線(xiàn)要注意不能隨便連接,盡量安排在FPGA的同一Bank中,否則可能導(dǎo)致傳輸 路徑不一致,在高速數(shù)據(jù)讀寫(xiě)下容易產(chǎn)生相位畸變,使得輸入和傳輸數(shù)據(jù)錯(cuò)誤。

DSP和FPGA之間的數(shù)據(jù)通過(guò)HPI接口,由FPGA寫(xiě)入DSP,節(jié)省DSP的數(shù)據(jù)讀寫(xiě)時(shí)間。DSP和FPGA之間還有EMIF接口,用于DSP 對(duì)FPGA的控制,DSP和FPGA之間的控制狀態(tài)由GPIO總線(xiàn)傳輸。同時(shí),DSP還連接一個(gè)EMIF接口到GC5016,用于DSP對(duì)GC5016的 控制和狀態(tài)讀取。

3 軟件設(shè)計(jì)

3.1 GC5016的控制寄存器設(shè)置

GC5016的控制寄存器被劃分為兩部分:8個(gè)全局寄存器和總共88頁(yè)的寄存器,每個(gè)頁(yè)包含了16個(gè)寄存器。全局寄存器的訪(fǎng)問(wèn)地址是 0x00~0x0F。頁(yè)寄存器的訪(fǎng)問(wèn)地址需先在全局寄存器的地址2寫(xiě)入頁(yè)地址,然后再訪(fǎng)問(wèn)0x10~0x1F,就可以訪(fǎng)問(wèn)該頁(yè)下的寄存器。每一個(gè)控制寄存 器在芯片內(nèi)被分配唯一的地址。這樣接口的設(shè)計(jì)就可以將GC5016作為處理器的一個(gè)外部存儲(chǔ)器來(lái)訪(fǎng)問(wèn)。

3.2 GC5016的初始化

GC5016的初始化根據(jù)電路的不同可以分為三種情況:第一種是單個(gè)GC5016芯片,第二種是多個(gè)GC5016芯片配置由主GC5016芯片同 步,第三種是多個(gè)GC5016芯片配置由外部源同步。而此次設(shè)計(jì)中只用一塊GC5016進(jìn)行寬帶下變頻的驗(yàn)證,所以屬于獨(dú)立GC5016芯片的配置。其配 置步驟如下:

① 寫(xiě)0xFF00到地址0,復(fù)位芯片。

② 寫(xiě)0x0000到地址3,禁止所有輸出。

③ 寫(xiě)0x0004到地址1,產(chǎn)生單觸發(fā)脈沖。

④ 裝載所有的配置寄存器。

⑤ 如果幾個(gè)通道需要同步控制,需要選擇一個(gè)同步源,可以通過(guò)在輸入文件中加入如下程序來(lái)實(shí)現(xiàn)同步控制:

soB_sync 4; fir_sync 4; sck_sync 4; nco_sync4; cic_sync 4;

⑥ 寫(xiě)0x0100到地址0,清除復(fù)位。

⑦ 寫(xiě)0x0004到地址1,產(chǎn)生同步脈沖,完成GC5016的設(shè)置。

3.3 GC5016的cmd5016軟件應(yīng)用

可以使用專(zhuān)門(mén)提供的GC5016的配置軟件實(shí)現(xiàn)對(duì)其寄存器的設(shè)置。這些配置包括以下內(nèi)容。

(1) 關(guān)鍵字的類(lèi)型

關(guān)鍵字的類(lèi)型,共5種,分別是mandatory(M)、defaulted(D)、computed(C)、unused(X)、 expert(E)。其中M是需要用戶(hù)進(jìn)行選擇的變量,D是初始化默認(rèn)值,C是軟件控制的變量,X是不用的變量,E一般是一個(gè)計(jì)算變量,不需要人為設(shè)置。

(2) 偽指令

在配置文件中,偽指令mode AB receive 和mode CD receive 可以使GC5016工作在4通道DDC模式。在此模式下需要設(shè)置的偽指令有:

◆ mode AB(CD) receive(定義DDC收發(fā)模式);

◆ rin_rate(全局變量,接收輸入數(shù)據(jù)速率,0代表半速率,1代表全速率,2代表雙速率);

◆ rin_cmplx(全局變量,接收輸入數(shù)據(jù),0為接收的為實(shí)數(shù)數(shù)據(jù),1為接收的為復(fù)數(shù)數(shù)據(jù));

◆ splitiq,splitiqAB,splitipCD(兩通道或者4通道模式變量);

◆ freq,fck,bypass_mix(復(fù)數(shù)混頻器freq_msb,freq_mid,freq_lsb的設(shè)置);

◆ bypass_cic,cic_dec(雙CIC濾波器的抽取因子);

◆ bypass_fir,fir_dec,fir_diff,fir_nchan,fir_coef(PFIR模式和濾波器抽頭);

◆ gain,overall_gain(手動(dòng)增益設(shè)置);

◆ agc_cf,agc_mode,agc_tc(AGC增益設(shè)置);

◆ pwr_mtr_on(接收功率計(jì)設(shè)置);

◆ routf_tdm(接收輸出格式控制通道D的TDM模式)。

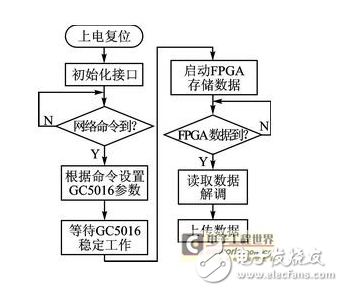

3.4 DSP軟件流程

系統(tǒng)的DSP軟件流程如圖3所示。

DSP上電復(fù)位后,初始化相關(guān)接口,這些接口包括EMIF接口、HPI接口以及網(wǎng)絡(luò)和 GPIO接口。初始化接口后,DSP等待從網(wǎng)口下發(fā)的控制命令,控制命令一般包括解調(diào)頻率、解調(diào)帶寬和解調(diào)方式等各種信息。DSP根據(jù)這些信息設(shè)置 GC5016的寄存器,并將這些寄存器值寫(xiě)入GC5016,使得GC5016可以正常工作,然后啟動(dòng)FPGA采集GC5016輸出的數(shù)據(jù),F(xiàn)PGA按照 1024個(gè)數(shù)據(jù)一幀進(jìn)行存儲(chǔ),滿(mǎn)一幀后通知DSP讀取這些數(shù)據(jù),DSP對(duì)這些數(shù)據(jù)解調(diào)后輸出到上位機(jī)顯示或者存儲(chǔ)。

圖3 DSP軟件流程

結(jié)語(yǔ)

GC5016是一種理想的可編程4通道數(shù)字上下變頻器,根據(jù)需要可配置為兩路作為上變頻、兩路作為下變頻。當(dāng)接收或發(fā)射的數(shù)據(jù)量龐大時(shí),還可以使用 多塊GC5016并行處理。再加上它的高速率、寬帶寬、高無(wú)雜散動(dòng)態(tài)范圍、低功耗和靈活配置等各種優(yōu)點(diǎn),使得GC5016的應(yīng)用非常廣泛,在CDMA/WCDMA、雷達(dá)及軟件無(wú)線(xiàn)電中都有強(qiáng)大的生命力和很好的發(fā)展前景。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論