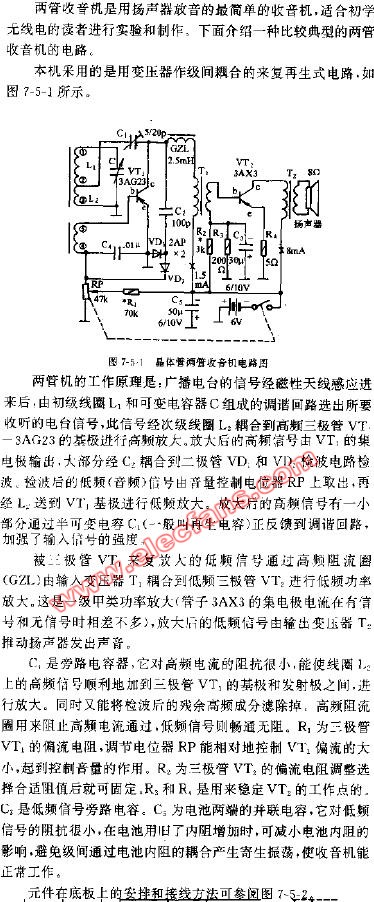

?本系統采用430單片機,FPGA。通過天線收到不同頻率的電磁波,通過單片機控制本振頻率的產生,從而選定不同頻率的電臺,經過混頻得到的信號由FPGA解調,最后通過功放由喇叭放出聲音。本系統在設計中注意低功耗處理和力求高性價比等細節。

本設計主要特點:

1. MB1504控制產生本振,具有高效,穩定,簡單特點。

2.FPGA穩定性好,處理速度快。

3. 數字式收音機接收數據更精確,收到的電臺更多更精確。

1.方案設計與論證

1.1主控系統選擇

方案一:采用高性能嵌入式系統,比如ARM。如果采用此方案,可以很好的解決數據處理和控制功能,但是ARM價格昂貴且本科階段很少接觸,在短時間內完成困難比較大。

方案二:采用一般單片機,如51單片機。但是51單片機內部資源不夠,很多功能無法實現。

方案三:采用430高性能單片機來實現,用來處理控制本振頻率。

考慮到方案的可實行性和性價比,我們采用M430F1611單片機,此款單片機可實現高速運算,存儲空間大,價格低廉,性價比極高。

1.2本振選擇

方案一:選擇分立元件搭配出,但是此方法難度太高,并且誤差干擾都很大。

方案二:完全選擇專用芯片有單片機控制。此方法簡單,但價格昂貴。

方案三:使用數字鎖相環芯片和分立元件組合的vco電路。

考慮到價格,工作頻率以及靈敏度等因素。本系統采用MB1504 鎖相環芯片和分立元件搭VCO。

1.3變頻選擇

方案一:采用一次變頻。此種方法方案簡單,容易實現,但對后端AD要求較高。

方案二:采用多次變頻。整體設計更加復雜,誤差也將各大,實現有難度。

考慮到收音機對數據要求較高,和整體性能。本系統采用一次變頻,芯片使用NE602。

1.4數據處理模塊選擇

方案一:采用專用解調芯片,此方法方案簡單,但擴展和開發性都很差。

方案二:采用FPGA芯片解調,此方案結構清楚簡單,穩定性好,但價格昂貴。

本系統選用了FPGA芯片作為解調,確保系統的開發性和準確性。

1.5音頻處理

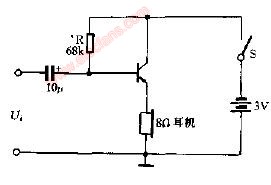

方案一: 使用三極管進行放大,效果不好并且復雜。

方案二: 使用專用功放芯片。

綜合考慮,本系統選用功放芯片LM386。

小結:

經過幾番仔細的論證和比較,我們決定了本系統主要模塊方案如下:

音頻處理方案:LM386。

主控制器:MSP430單片機。

本振電路方案:MB1504+分立元件的VCO。

變頻模塊:NE602。

數據處理模塊:FPGA最小系統板。

2.電路設計

2.1系統組成原理

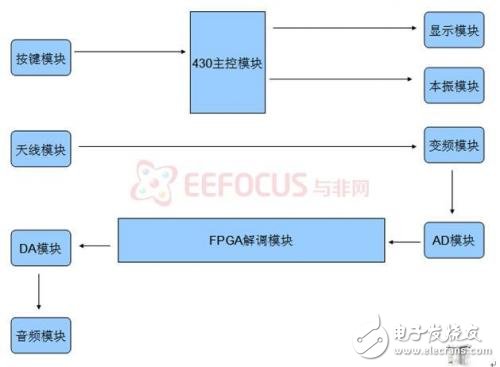

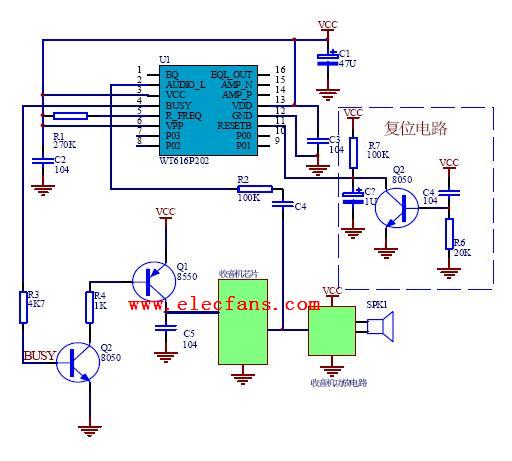

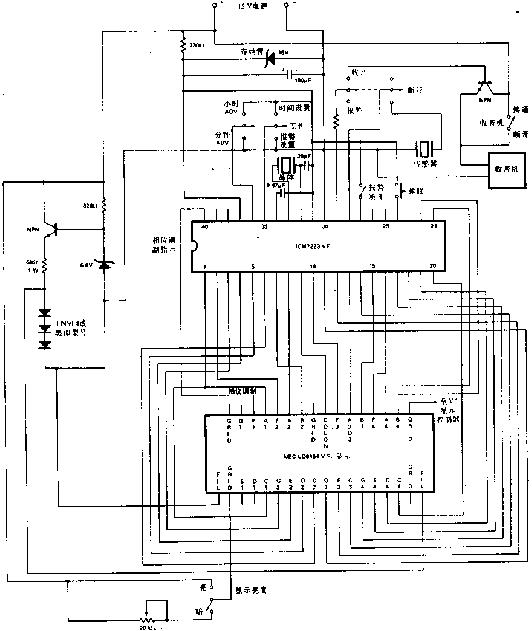

本系統由本振模塊,變頻模塊,主控單片機,FPGA解調模塊,音頻模塊,AD模塊,DA模塊等組成。

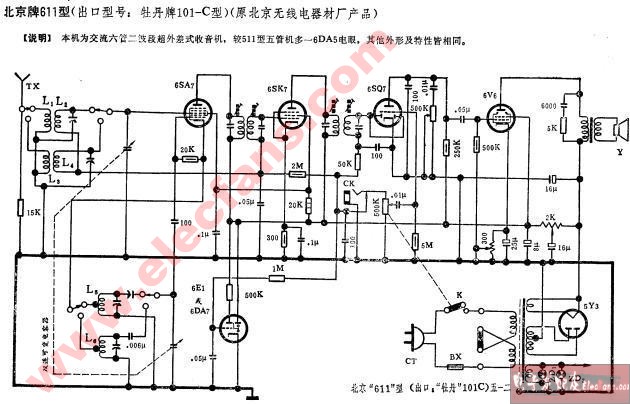

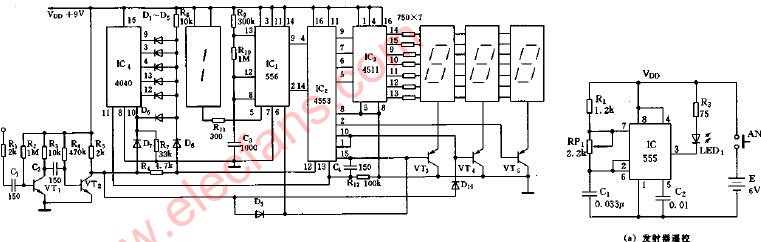

圖2.1系統組成原理圖

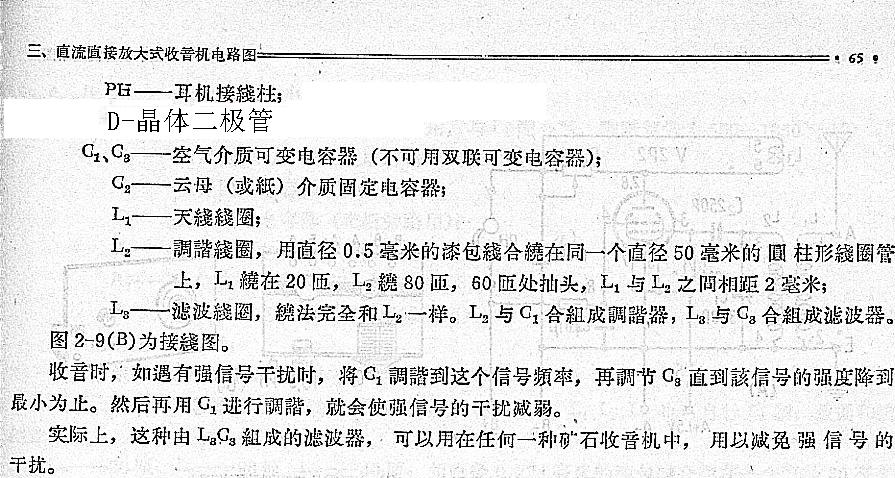

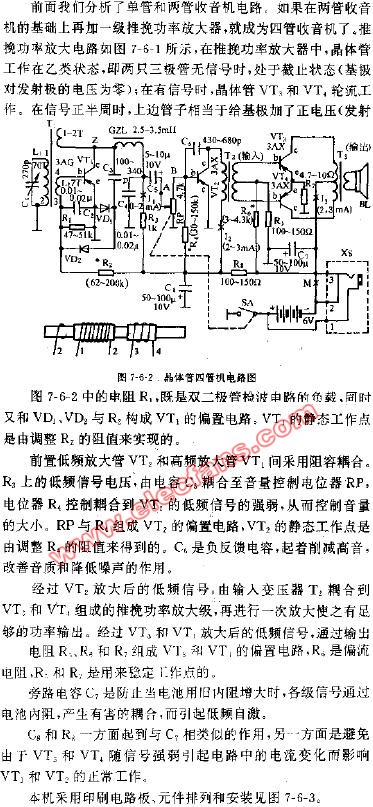

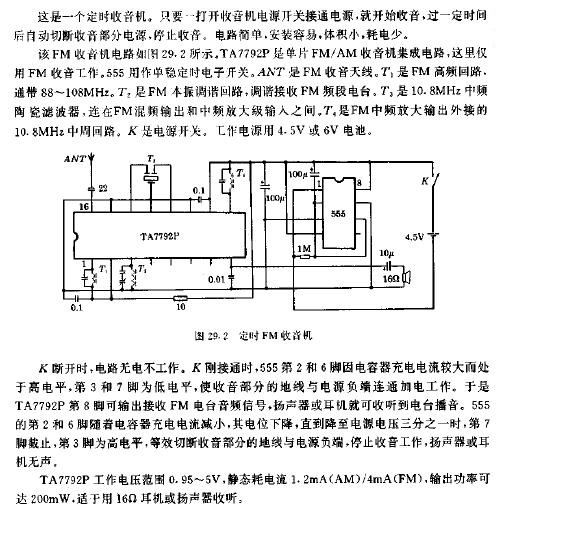

2.2本振電路

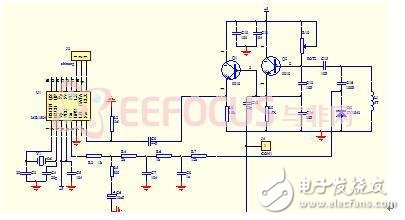

通過單片機控制MB1504鎖相環和壓控振蕩器產生所需要的頻率。

圖2.2本振電路原理圖

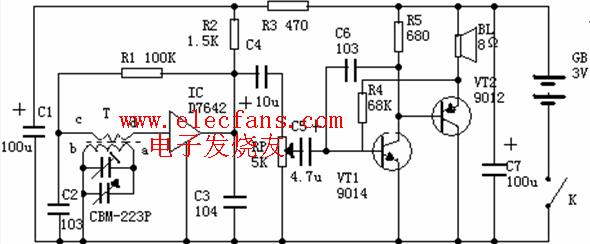

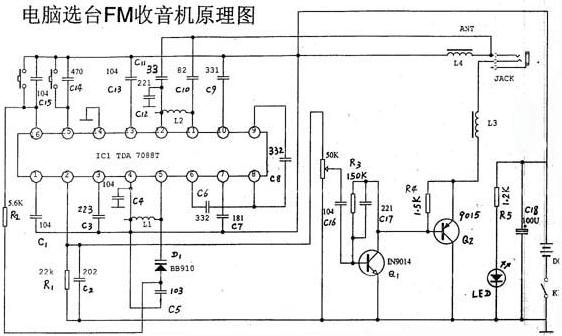

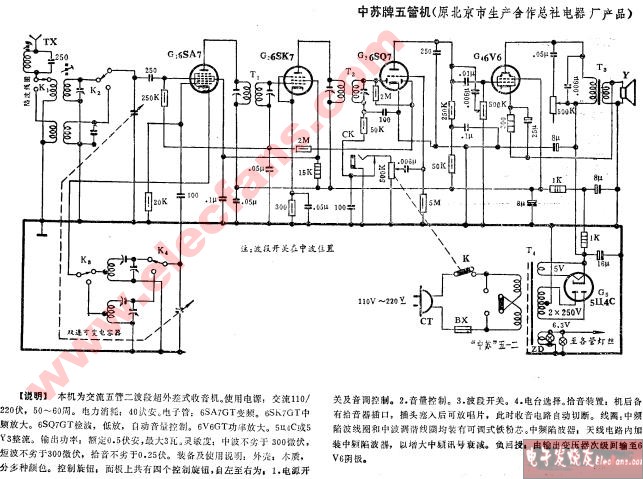

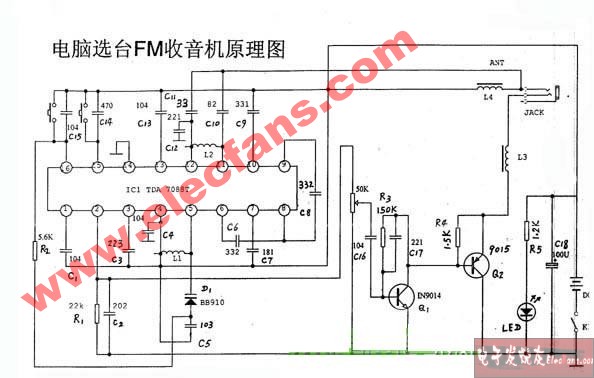

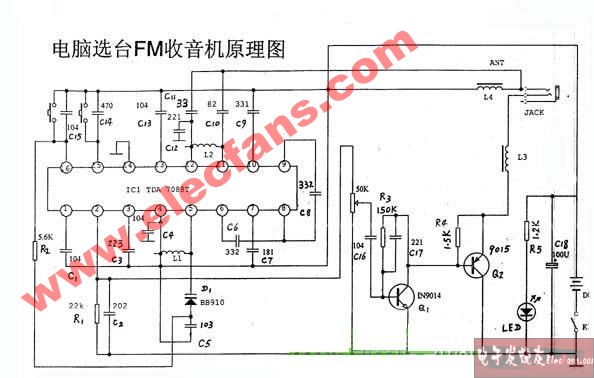

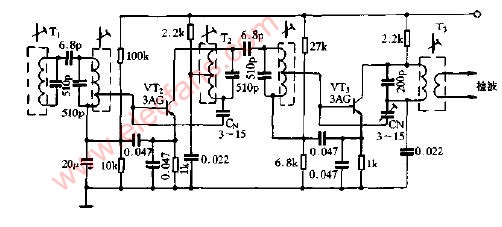

2.3變頻模塊

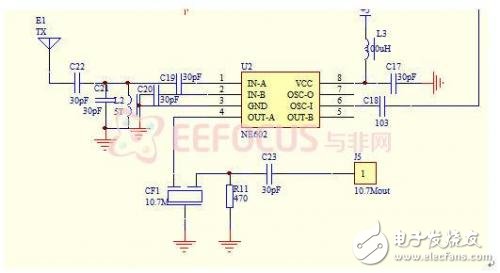

本振產生的頻率與天線接收進來的頻率經過NE602混頻放大。

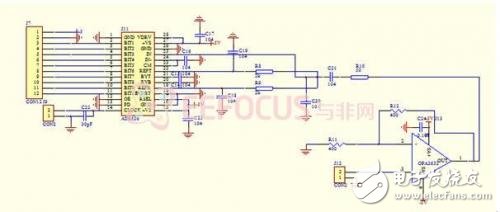

圖2.3變頻模塊原理圖

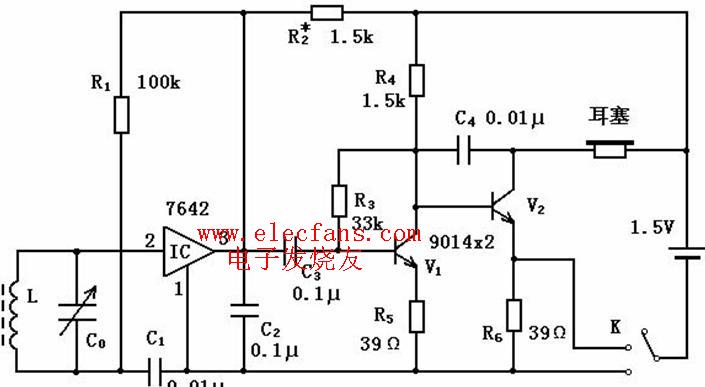

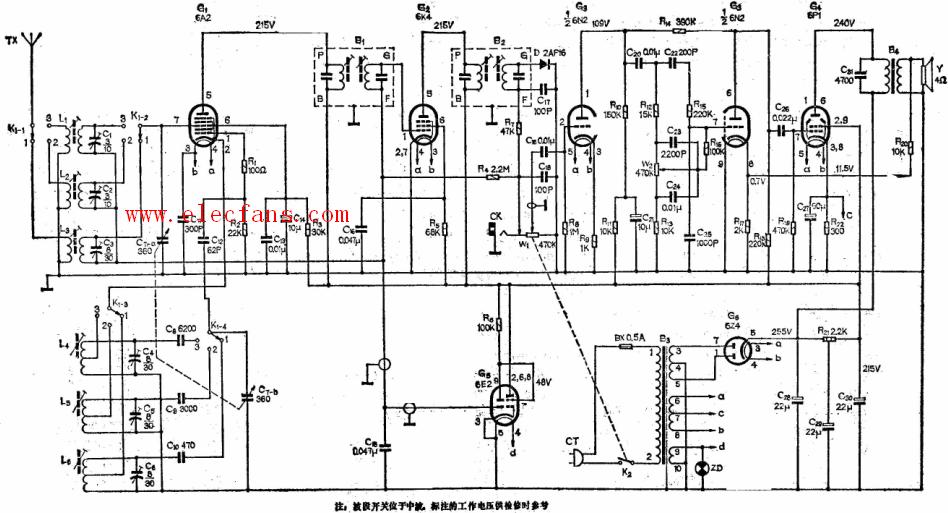

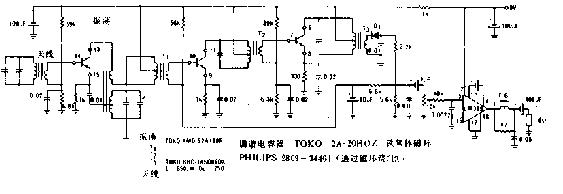

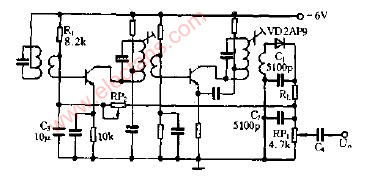

2.4AD,DA模塊

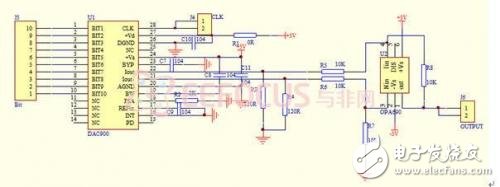

變頻之后的模擬信號經過AD采入FPGA解調,解調之后再用DA轉換為模擬信號

圖2.4.1 DA模塊

圖2.4.2 AD模塊

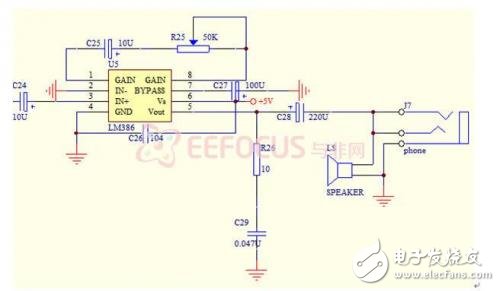

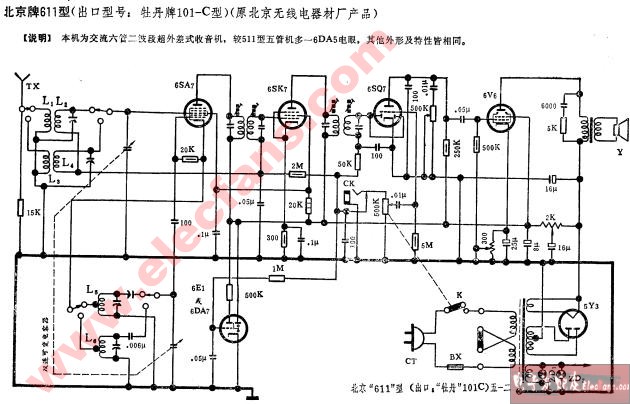

2.5聲音模塊

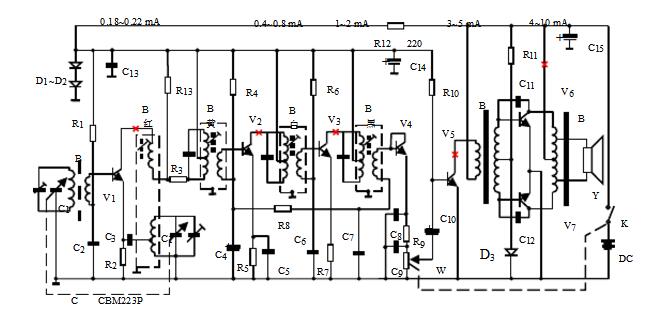

模擬信號經過功放放大后送入喇叭,還原成聲音信號。

圖2.5功放電路

3.軟件設計

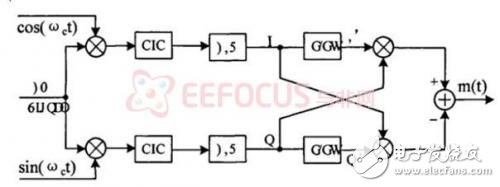

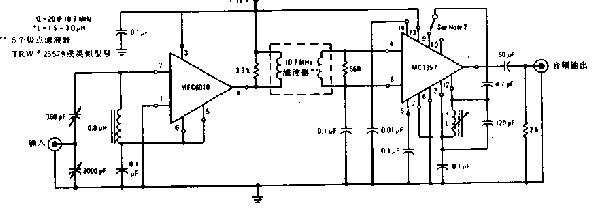

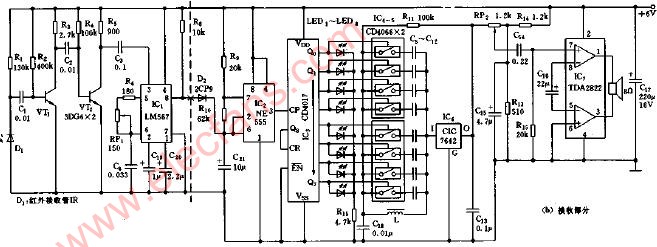

3.1FPGA解調

、

、 為正交信號,cM Signal為ADC采樣到的數字cM中頻數據,經過兩路正交相乘后進行CIC抽取,cIo低通濾波器用來濾除正交相乘后產生的和頻分量,包含語音信息中的零中頻信號分量被保留。正交零中頻分量再經過求導交叉相乘,求差,即為有用的語音信息。

為正交信號,cM Signal為ADC采樣到的數字cM中頻數據,經過兩路正交相乘后進行CIC抽取,cIo低通濾波器用來濾除正交相乘后產生的和頻分量,包含語音信息中的零中頻信號分量被保留。正交零中頻分量再經過求導交叉相乘,求差,即為有用的語音信息。

圖3.1 FPGA中頻解調

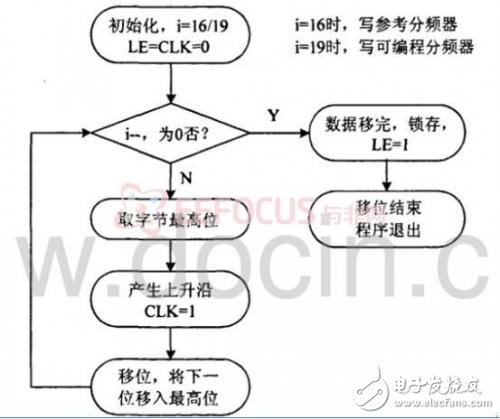

3.2單片機控制

圖3.2單片機發送流程圖

4.系統測試

1.整體測試。

測試功能收到7個電臺,基本實現所要求功能。

2.誤差分析

有些電臺接受不了,或者聲音不清晰經分析原因有兩個:

1)AD由于是欠采樣對對信息完整度有影響。

2)天線接受信號攜帶的干擾信號并沒有完全濾除造成干擾。

5.設計總結

本作品FPGA和430為核心部件,通過控制本振頻率,從而選定不同的電臺信號,經過混頻產生10.7M頻率信號,再經過FPGA解調,功放放大還原成聲音。在設計中,我們盡量采用低功耗器件,力求硬件電路的經濟性和精簡性,充分發揮軟件控制靈活方便的特點,來滿足設計要求。

電子發燒友App

電子發燒友App

評論