項目背景及可行性分析

1.. 項目名稱: HF/VHF數字調制多功能發射機

2.. 項目的主要內容及目前的進展情況:

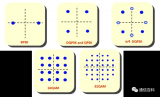

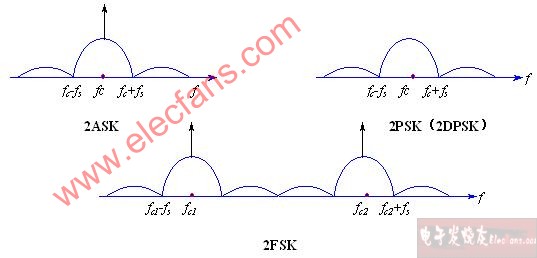

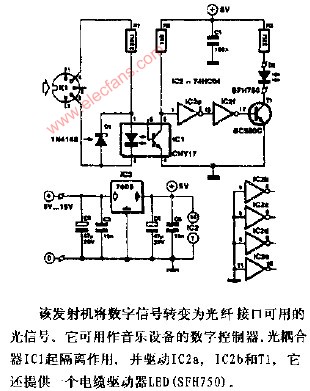

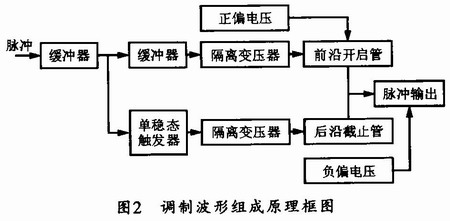

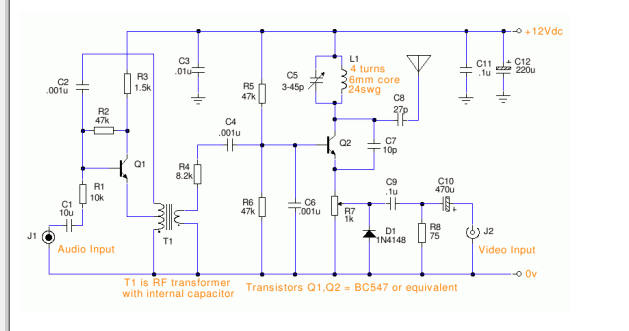

本項目主要的內容是:設計制作一臺能工作在HF及VHF波段的數字調制發射機,能提供AM, FM,DSB,SSB等語音通信調制模式,及ASK,FSK,PSK等數據通信調制模式. 話筒輸入的語音信號經 AC97 Audio CODEC 編碼后輸入FPGA進行數字調制, 電鍵和RS—232接口輸入的數字信號經FPGA進行數字調制,各種調制模式能在瞬間互相切換.

目前的進展情況:本項目已通過可行性論證,證實方案可行.現在正在進行子模塊的功能劃分,以及子模塊性能參數的初步確定.

3.. 項目關鍵技術及創新點的論述:

本項目的關鍵技術是:數字實時調制;FPGA乘法器的復用;雙路DAC正交輸出;DDS和FPGA的綜合運用.

數字實時調制,要求對FPGA的邏輯資源有深入的了解.通過合理設計邏輯電路,運用流水線技術,提高FPGA的信號處理速度,以滿足數字實時調制對FPGA處理速度的嚴苛要求.

由于FPGA的乘法器數量有限,通過邏輯單元構成乘法器則會消耗大量的邏輯單元,不但不符合對成本效益的要求,而且這樣往往也不能滿足多調制模式數字調制器對乘法器的龐大需求.在設計多調制模式數字調制器時必須考慮如何把有限的乘法器通過復用來減少對乘法器的需求,盡可能利用FPGA內部的乘法器,而不利用邏輯單元來構成乘法器.若用DSP芯片來實現多調制模式數字調制器, DSP芯片內部的乘法器在程序運行時就能得到復用,因此在實現多調制模式數字調制器的時候往往采用DSP芯片的方案而不采用FPGA的方案.

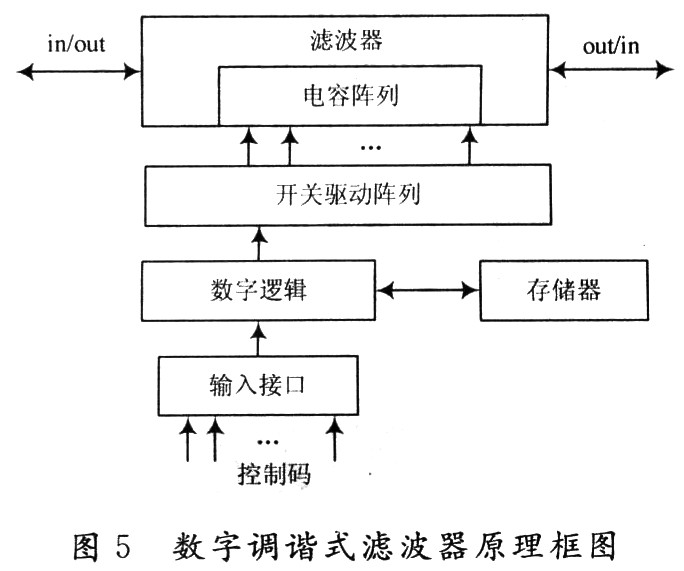

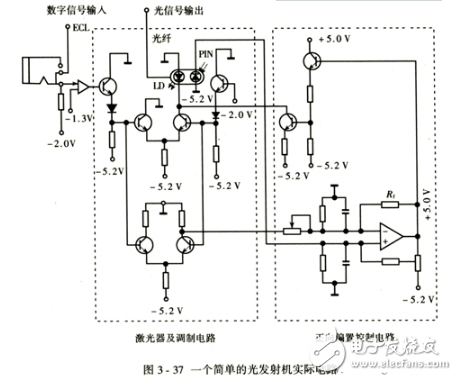

雙路DAC正交輸出與后面的DDS,兩路混頻器和加發器共同構成鏡像抑制混頻器,用于把DAC輸出的信號進行頻率的搬移,以滿足輸出信號覆蓋HF和VHF頻段的設計要求.由于兩路DAC后接的LPF的相頻特性不可能完全一致,因此在FPGA中必須考慮增加補償算法.

本項目的創新點在于:通過對各種調制模式Verilog實現的改進,在保證滿足實時調制的情況下,復用乘法器,把邏輯單元的消耗減少到最低,從而減少系統的功耗.空余的邏輯單元為后繼的系統升級留下足夠的邏輯單元資源.并且可以提供比多DSP芯片方案更高的可靠性和集成度,符合現代消費電子產品對體積的嚴苛要求.

利用DDS+FPGA數字調制方案,相對于市面上消費通訊產品大量采用的模擬調制方案,具有可靠性高,抗干擾能力強,體積小,調試容易,設備升級容易等優點.

4.. 技術成熟性和可靠性論述:

技術成熟性:

以DAC+FPGA的基本方案為基礎.配合DDS專用芯片產生正交本地振蕩信號,利用AC97 Audio CODEC進行音頻信號的采樣與編碼,采用RS-232接口與PC機進行通訊,以MCU,LCD,鍵盤作為人機交互界面.以上這些是本系統的主要組成模塊,它們都具有高成熟性的特點,采用這些模塊構成的設備現正被大量生產和銷售,因此本系統所采用的基本技術是十分成熟的.

技術可靠性:

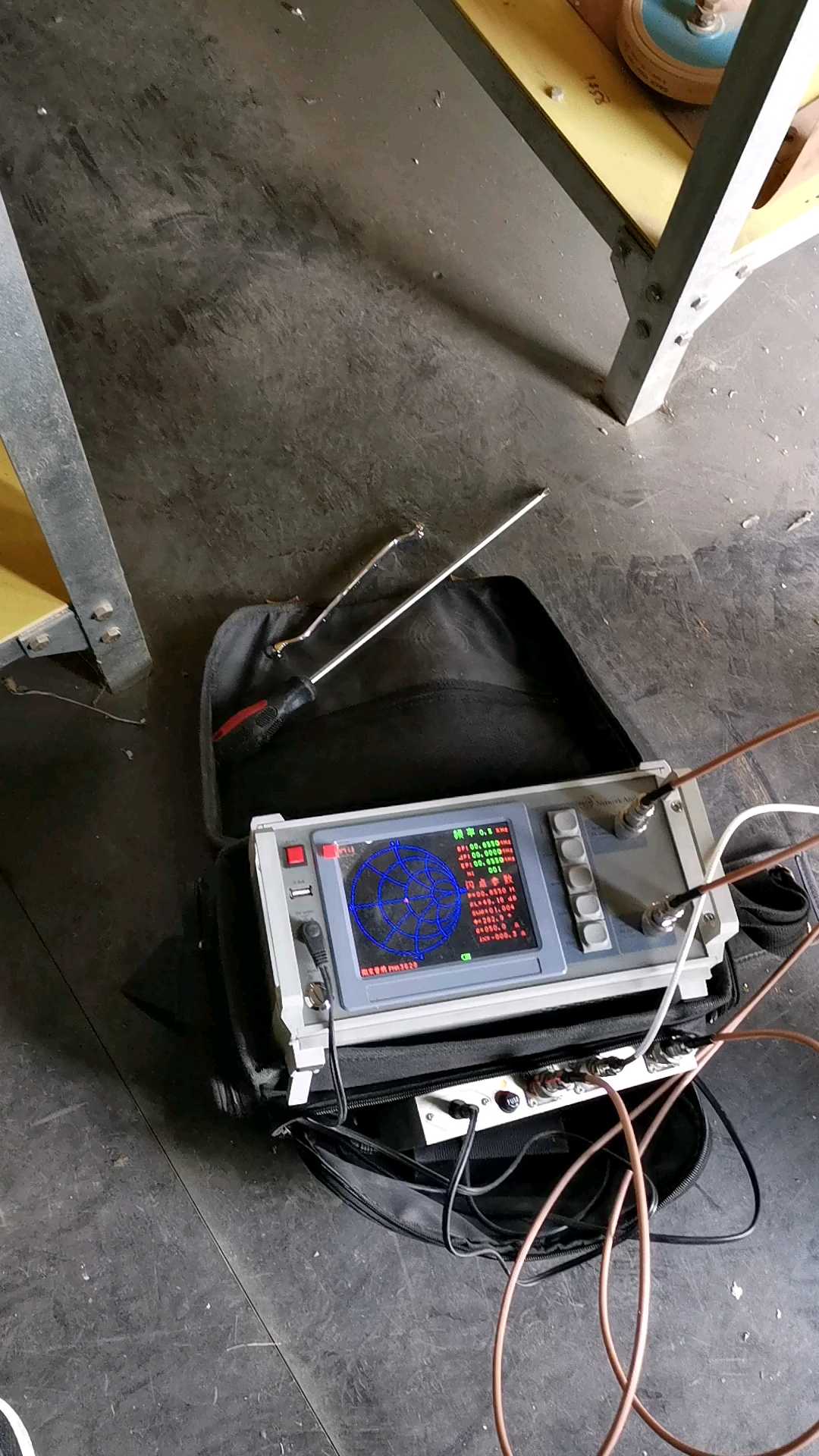

本設計項目以V2PRO硬件開發平臺為基礎,配合雙路DAC,DDS信號發生,混頻電路,以及寬帶放大器,人機交互模塊構成. V2PRO硬件開發平臺具有集成度高,擴展容易的特點,還集成有AC97 Audio CODEC和穩壓供電電路,因而V2PRO硬件開發平臺具有高可靠性的特點.

雙路DAC,DDS信號發生器,寬帶放大器均采用專用芯片構成,混頻電路則采用混頻器模塊, 人機交互模塊沒有采用FPGA內部的PowerPC來完成,主要是基于EMI/EMC的考慮,避免把外部的干擾引入FPGA影響系統輸出信號的質量. 人機交互模塊采用工業級的具有相當抗干擾能力的單片機,程序采用代碼陷阱等方法提高抗干擾能力, 人機交互模塊的電路嚴格按照EMI/EMC的要求設計,增加各種抗干擾電路,并且在經過充分測試后才接入系統.上述電路由于大量采用專用芯片和模塊來代替分立元件電路以及以嚴謹的精神進行設計,因此具有可靠性高,調試容易,體積小巧等優點.

電子發燒友App

電子發燒友App

評論