不斷發展的通信標準(如LTE-A和5G)正在推動RF架構創新,因此,在小型化、性能和對通過提高頻譜效率來提高數據吞吐量的技術支持方面,給RF前端模塊設計帶來了挑戰。

為了滿足多模和多頻手機對更高性能和更小元件尺寸的需求,業界正在將模塊集成策略從單一封裝中的類似構建模塊轉換為采用基于多種技術的多功能前端。這些開發工作針對每個頻率范圍的、基于單個完全集成的RF模塊產品,包括多模/多頻功率放大器(PA)、雙工器和RF開關等。

通常情況下,模塊和子系統設計人員在設計中會使用多種技術。這些技術包括砷化鎵(GaAs)和氮化鎵(GaN)單片微波集成電路(MMIC),硅RFIC和多層層壓板。每種技術都封裝在一個特定的工藝設計套件(PDK)中,并會詳細說明制造工藝和前端構建模塊(組件庫)的電氣和物理屬性。

支持多個PDK和電路/電磁(EM)協同仿真的多技術設計流程用于分析體聲波(BAW)和表面聲波(SAW)濾波器之間的電相互作用(基于等效電路模型)和多層層壓封裝。它可提供全面的模塊分析和優化。但是,開發硅RFIC開關、低噪聲放大器(LNA)和PA時,情況會有所不同,需要采用針對性更強的開發工具。

本文介紹了一種現代設計流程,它將PDK轉換為可在NI AWR設計平臺中進行仿真的流程,以支持芯片封裝協同設計和EM驗證。通過將設計導入到可與PDK一起使用的動態庫中,設計人員能夠使用最初在完全不同的環境中創建的復雜設計,基于不同的技術有效地開發產品。

為特定需求設計的EDA工具

設計人員根據個人喜好和特定工具的功能,使用不同的射頻EDA工具來處理單個或一組設計任務。一些工具專注于高頻MMIC、PCB和模塊設計,如Microwave Office電路設計軟件。其他廠商,如Cadence的應用目標是基于硅的RFIC和模塊設計。由于這些工具中的每一個都有各自的優勢,因此最好采用那些支持互操作性和信息交換的設計流程,以便設計人員可以為每個設計任務選擇最佳工具。

為了支持不同環境之間的數據交換,已經開發了幾種行業標準文件格式,例如touchstone(SNP)和測量數據交換格式(MDIF)文件。touchstone文件提供S參數,即網絡的小信號模擬或測量頻率響應。MDIF文件允許通過無限數量的獨立變量(如頻率或柵極電壓)對S參數或噪聲等數據進行排序。這些格式允許設計人員在其仿真中對器件(例如RFIC或開關)的線性響應進行建模,并輕松地在設計工具之間來回傳遞該模型。

多諧波模型(有時也稱為Keysight X參數)類似于S參數,增加了模擬大信號工作條件下的非線性行為的能力。在不同設計工具之間使用的其他數據格式包括用于電路塊的Spice網表,用于原理圖信息的交換文件格式(IFF),以及諸如GDSII和DXF的布局格式。

這些標準格式可以充分發揮作用,但它們各有其局限性。例如,S參數用于線性模擬,它們不適用于非線性模擬。一些RF模擬器只能使用雙端口MDIF文件。大信號多諧波模型可能需要很長時間才能生成和模擬,文件往往很大,難以共享。而對于X參數來說,文件可以是千兆字節。

模塊和子系統設計人員面臨的挑戰

對于集成了使用各種工具開發的多種技術的RF模塊,由于整體設計任務的復雜性,對工具之間更大互操作性的需求往往超出簡單的數據格式兼容性。前端模塊和其他多技術設備可在單個層壓模塊上包含多達25個集成電路,包括BAW和SAW濾波器、III-V RF MMIC PA,以及具有多個天線的硅開關和硅LNA。在本文的設計實例中,硅開關和LNA是在Cadence工具中設計的,聲學/層壓濾波器是在Microwave Office軟件中完成的。圖1所示為典型的多芯片模塊設計。

圖1:Microwave Office軟件環境下的典型模塊設計

為交換機設計人員創建所有所需開關狀態所需的文件非常耗時。該過程可能容易出錯,因為需要支持RFIC涵蓋的250多個狀態。對于touchstone文件,僅捕獲線性行為。對于開關甚至聲學濾波器而言,至關重要的非線性行為需要由較大的多諧波文件捕獲。隨著RFIC分析和S參數文件生成,每個狀態需要7分鐘,而一個開關操作有68個狀態,另一個有25個狀態,這時,需要投入大量的時間,一般情況下,一個操作過程會花費數小時甚至數天。

Cadence?Virtuoso和NI AWR軟件協同仿真流程

本文介紹的解決方案利用了直接在Microwave Office軟件中支持Cadence設計的新功能。圖2所示即為此流程。在這里,基于Microwave Office的Spectre網表轉換的設計流程可以使Virtuoso和NI AWR軟件協同仿真。

圖2:NI AWR設計平臺中用于協同仿真的Cadence Spectre轉換流程

通過采用硅工藝PDK并通過Spectre設計網表將其傳輸到Microwave Office軟件中,設計人員可以訪問所有NI AWR設計環境工具,從而實現該流程。這些工具包括Visual System Simulator(VSS)系統設計軟件,Microwave Office線性和非線性仿真,APLAC諧波平衡和瞬態仿真,NI AWR布局工具,以及AXIEM 3D平面和Analyst 3D finite-element method (FEM)EM仿真器。

圖3所示為具有片上濾波器的雙極/八擲(DP8T)硅開關的Virtuoso原理圖,其關鍵部件是天線開關模塊(ASM),它有6種不同的開關狀態。

圖3:Cadence Virtuoso開關原理圖

網表和運行

使用“Netlist and Run”命令將創建NI AWR軟件轉換所需的文件。由于此命令是在測試平臺運行的,因此要轉換的實際上是一個子電路。創建的最關鍵文件是input.scs,其中包含所有相關的Cadence原理圖信息。

運行“Import Spectre Netlist Design”腳本將打開一個簡單的用戶界面對話框。這種開關設計(大約2,000行網表)的翻譯大約需要一秒鐘。翻譯完成后,可以在任何設計中使用兩個組件:一個用于流程,另一個用于實際設計。

還要生成一個日志文件,為設計人員和設計支持團隊提供有關已翻譯的單元格,使用的庫以及測試平臺模擬的更詳細信息。該轉換包括原始設計中的微帶線(MLIN)元素,它提供了設計中傳輸線中色散和損耗的精確建模。此外,還會捕獲Cadence側包含S參數塊的任何文件的目錄路徑。

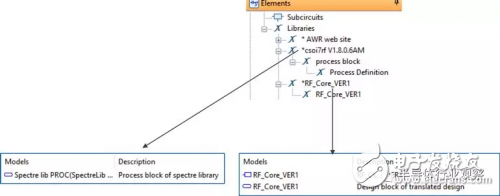

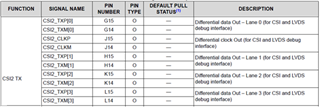

轉換開關設計完成后,用戶將兩個新的PDK加載到Microwave Office軟件中的新項目或現有項目中:翻譯的Cadence代工廠PDK(csoi7rf Global foundries PDK,見圖4左側)和設計PDK(RF-Core,見圖4右側)。RF Core文件提供了原理圖元素和設計塊。這些PDK將提供模擬所需的三個簡單的NI AWR軟件庫元素。

圖4:翻譯的Cadence代工廠PDK(左)和設計PDK(右)出現在元素樹庫中,可以插入任何NI AWR軟件設計中

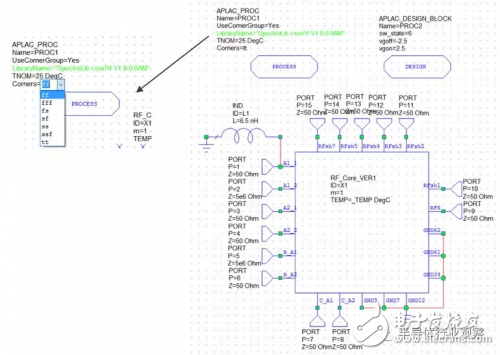

新的庫元素可通過標準“拖放”放置到Microwave Office電路設計軟件原理圖中,就像任何其他原理圖元素一樣。如圖5中的原理圖所示,PROCESS塊用于引用代工廠PDK制程,并允許用戶更改process corners。使用DESIGN塊,用戶可以訪問Cadence設計中的任何設計變量。

圖5:在此Microwave Office原理圖中可以看到PROCESS塊(代工廠PDK制程)和Cadence設計的設計變量的DESIGN塊

在圖中右側,翻譯的組件有大約20個端口。DESIGN模塊用來控制開關狀態的位置(在本例中設置為6),以及控制開關狀態的兩個電壓。左上角的PROCESS塊(在圖的左側突出顯示)為設計人員提供了指定process corners的能力,這對于IC設計非常重要。

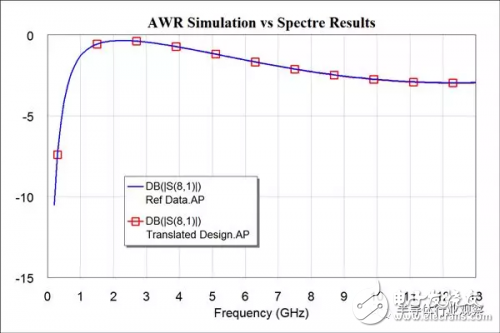

為了驗證在Microwave Office中模擬的網表轉換與原始Spectre結果的頻率響應,將測試用例Spectre模擬的S參數導入Microwave Office進行比較。驗證設置實際上與包含已翻譯網表的原理圖測試臺相同。對于此仿真,子電路包含直接從Cadence導出的touchstone S參數塊。

比較小信號結果

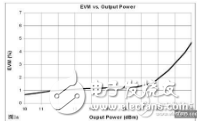

圖6所示為NI AWR軟件模擬的小信號結果與Spectre結果的比較情況,這由整個頻帶上的S參數表示。正如所料,結果顯示兩個結果確切一致。

圖6:將NI AWR軟件模擬的小信號結果與Spectre結果進行比較

補充分析

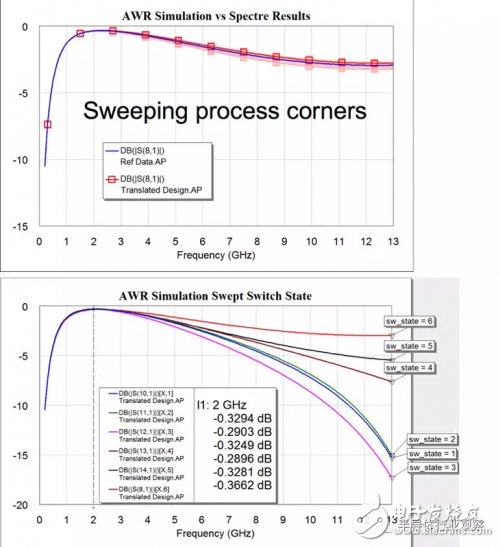

現在已經驗證了設計轉換,可以使用開關執行許多其他仿真,包括掃描process corners,調整/掃描開關狀態,以及調整/掃描控制電壓。導入的RFIC就像常規的Microwave Office元素一樣。在圖7的左側,已將掃描process corners與直接從Cadence獲取的參考數據進行比較,顯示出了process corners的影響和模擬器之間的重疊。

圖7:現在可以使用開關運行其他模擬,因為它的行為類似于常規的Microwave Office元素

圖7的右側顯示了在該示例中針對不同開關狀態(通過路徑)的模擬插入損耗。RFIC通過6種不同的開關狀態進行控制,顯示了取決于開關狀態的不同響應。設計人員現在可以根據精確的RFIC模型開發層壓板設計細節,通過參數設置輕松改變狀態,可以實現調整或掃描。

此外,由于開關設計是常規的Microwave Office子電路,它可以與任何其他Microwave Office元件,EM結構,數據文件等組合。可以將多種技術組合到一個Microwave Office項目中,實現跨技術的協同仿真以及布局集成。單個疊層模塊可以包含并組合硅開關、III-V PA RFIC、聲學濾波器等。最終的集成設計布局包括聲學濾波器、硅器件、GaAs-PA和模塊。

分配布局

開關布局也可以以GDSII等標準格式從Virtuoso導出并導入NI AWR軟件,然后可以與原理圖子電路關聯或鏈接,以確保正確的布局連接(見圖8)。布局幾何形狀是相同的,顏色根據偏好而不同。

圖8:開關布局可以從Cadence Virtuoso導出并導入到NI AWR軟件中,然后可以與原理圖子電路關聯或鏈接,以確保正確的布局連接

結論

本文介紹了一種集成設計流程,用于將源自不同軟件工具的多種技術組合到一個項目中,實現仿真和布局設計工具之間的協同仿真。該流程不僅可以使設計人員集成不同的半導體和封裝(層壓)技術,還可以利用最初在RFIC設計環境中創建的復雜設計,并將其集成到專門用于MMIC、RF PCB和模塊開發的設計環境中。最終的集成設計布局包括4種不同的技術:聲學濾波器,硅器件,GaAs PA和模塊。

電子發燒友App

電子發燒友App

評論