引言

射頻識別(Radio Frequency Identification,RFID)技術是一種以射頻信號為通信載體非接觸的自動識別技術,能夠實現無線信息交流。RFID技術采用射頻信號傳輸數據,具有非接觸和在惡劣環境下工作等優點。此外,相比于其他識別技術,RFID標簽能夠通過上位機操作讀卡器進行讀寫,更加方便和高效。因此,目前該技術已被廣泛應用于交通運輸、身份驗證、門禁安全等領域。根據供電方式,RFID標簽可以分為有源、無源和半有源標簽。

本文首先介紹了典型的嵌入式RFID系統,之后以意法半導體公司STM32F103VET6為核心與CR95HF射頻芯片組成一個便攜式讀卡器。同時,針對現有RFID標簽存在存儲容量小、數據傳輸方式單一等問題,基于意法半導體提供的M24LR64芯片,研究設計了一款應用于嵌入式RFID系統的大容量無源RFID標簽。該讀卡器和標簽無線工作頻率為13.56 MHz,符合ISO/IEC 15693標準,并支持符合I2C總線標準的有線通信;標簽存儲容量可達24 KB,可以滿足方便攜帶和大容量存儲的要求。

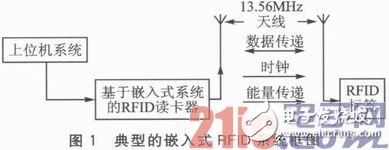

1 嵌入式RFID系統介紹

典型的嵌入式RFID系統通常包括以下部分:上位機系統、讀卡器、射頻標簽。讀卡器由嵌入式微處理器和射頻芯片組成。上位機工作的流程大致分為讀寫兩個部分:讀取標簽和向標簽中寫信息。讀取標簽信息時,上位機發出指令信號存入微處理器,軟件控制射頻芯片發送讀數據命令給標簽,標簽根據接收到的讀數據命令將存儲單元中指定的數據通過天線發送到讀卡器,讀卡器再將數據發送到上位機系統。向標簽中寫信息時,過程類似,上位機通過射頻讀卡器發送寫指令,并將數據寫到所設計標簽的相應存儲單元。典型的嵌入式RFID系統框圖如圖1所示。

2 基于嵌入式系統的讀卡器和標簽的設計

2.1 嵌入式RFID讀卡器的設計

2.1.1 讀卡器主控芯片及外圍電路的設計

本設計主控芯片采用STM32F103VET6微處理器。該處理器基于ARM Cortex—M3內核,支持多種通信總線,工作頻率為72 MHz,包括5個USART串行接口、2個I2C總線接口、3個SPI總線接口、CAN總線和USB總線。同時,該處理器還具有80個通用I/O口、A/D轉換器、16位定時器、實時時鐘等功能,具有功能強大、功耗低等優點,可以滿足本系統讀卡器的設計要求。

讀卡器采用標準USB 5 V供電,通過穩壓芯片KF33BDT提供3.3 V電壓供微處理器使用。為了抗干擾,微處理器的每個電源引腳都并聯了0.1μF的去耦電容。微處理器的外部時鐘源選用兩個,分別為高速外部時鐘源和低速外部時鐘源。高速外部時鐘源的晶振頻率為8 MHz,用于為系統提供精準的主時鐘;低速時鐘源的晶振頻率為32.768 kHz,用于為時鐘或日歷等提供時鐘源。負載電容的選擇需要根據晶振的大小進行匹配,本讀卡器中高速外部時鐘源的負載電容為20pF,低速外部時鐘源負載電容為10pF。sTM32F103 VET6微處理器通過串口與CR95HF射頻芯片進行通信,采用標準JTAG接口實現程序的燒寫與調試,并通過USB總線與上位機高速通信。

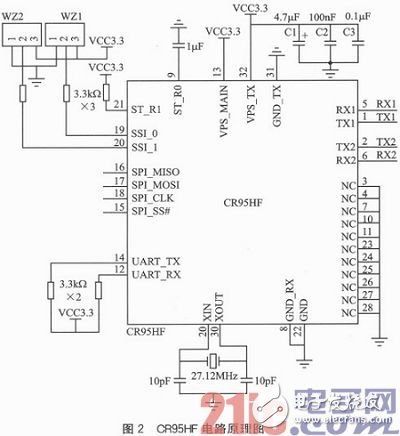

2.1.2 讀卡器射頻電路設計

本文設計的RFID讀卡器使用意法公司的CR95HF射頻芯片。CR95HF是具有SPI和UART串行接入的多協議非接觸13.56 MHz射頻芯片,支持ISO/IEC14443 A和B、ISO/IEC 15693以及ISO/IEC 18092等協議,能管理讀卡器模式的幀編碼和譯碼,可以廣泛應用于RFID等近場通信。以CR95HF作為射頻芯片,支持高頻頻段的無源RFID,可以與本文所設計的基于M24LR64的新型大容量標簽進行無線通信。CR95HF電路原理圖如圖2所示。

本設計中的CR95HF使用串口方式與STM32F103VET6微處理器通信,CR95HF提供與串口標準兼容的通信接口(14和12引腳),可與微處理器進行雙向通信。CR95HF射頻芯片供電電壓為3.3V,可以使用STM32F103VET6所用電壓。同時,電容C1、C2、C3用來去耦,減少干擾。RX1、TX1、RX2、TX2引腳用來連接匹配電路和天線。CR95HF工作在高頻頻段,在天線設計上,通過匹配電路電容和電阻值的選取,得到匹配電路的等效電容,由于會和天線電感組成頻率為13.56 MHz LC振蕩回路,因而可以計算出所需的天線電感,從而得到天線參數,進行匹配設計。

2.1.3 數據通信部分的設計

本文設計的RFID讀卡器通過使用STM32F103VET6芯片內部集成的標準USB接口與PC上位機實現有線通信。USB接口支持設備的即插即用和熱插拔功能,從而可以方便地實現讀卡器設備的移動。同時,USB2.0高速總線傳輸速率可達480 Mbps,可以快速地將讀卡器與PC上位機進行數據交換。由于本文所設計標簽具有容量較大等特點,因而讀卡器需要能夠快速地將讀取到標簽內的大容量數據傳輸給上位機,而USB總線傳輸速率極高的優點使得本讀卡器可以滿足實時需求。

2.2 基于M24LR64的大容量無源RFID標簽設計

2.2.1 大容量RFID標簽電路設計

M24LR64是意法半導體公司推出的一款新型無線存儲器芯片,其內部具有口令保護的64 Kb EEPROM,支持工作頻率為13.56 MHz,符合ISO/IEC 15693協議標準的無線通信接口數據,傳輸頻率為400kHz,符合I2C串行總線標準的有線通信接口。其工作電壓為1.8~5.5 V,在I2C總線接口模式下,芯片工作電源由VCC引腳提供,存儲器結構為8 192×8位;在無線射頻接口模式下,以接收到的射頻載波信號為工作電能,存儲器結構為2 048×32位。M24LR64引腳配置圖如圖3所示。

由于該芯片價格比較昂貴,應根據不同的需求選擇標簽存儲容量;根據項目需要,本文設計了采用3個M24LR64芯片的標簽,即實現了24 KB的大存儲容量標簽。另外對三個芯片采用并聯方式,從而實現三個芯片共用一條I2C總線和一根天線,減少標簽的成本和功耗。

設計中,通過讓3個M24LR64的E1、E0引腳依次賦值00、01、10來區分是第幾個M24LR64存儲器。SCL、SDA為引出的I2C總線接口。同理,當標簽采用RFID讀卡器對標簽進行無線數據讀寫時,根據3個M24LR64引腳E1、E0的不同來區分和選擇所需的M24LR64。其中,AC0和AC1是存儲器天線的收發端,將其并聯實現了共用一個天線。標簽電路原理示意圖如圖4所示。

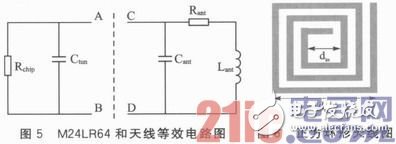

2.2.2 天線研究與設計

M24LR64在進行無線方式的信息讀寫時,采用頻率為13.56 MHz的高頻(HF)載波進行通信。通過電磁耦合,標簽利用外部電感天線從嵌入式RFID讀卡器的電磁場中獲取所需電能。M24LR64等效電路和天線等效電路圖如圖5所示。其中,Ctun是M24LR64的內部調諧電容,其值為28.5 pF,并聯電阻Rchip以模擬芯片的電流消耗;天線是一條導線,Rant表示等效電阻,Lant表示天線電感,Cant表示天線寄生電容。

由于在一階微分方程式中,Rchip、Cant、Rant可以忽略不計。因此,M24LR64存儲芯片和天線等效于諧振頻率為13.56 MHz的LC振蕩回路,滿足:

其中f=13.56 MHz,Ctun=28.5 pF,可以計算出一個M24LR64時所需天線電感。由于采用3個M24LR64并聯,總電容為單個M24LR64的3倍。求得設計標簽所需的天線電感:

代入數據,可得所設計標簽的理想天線電感Lant=1 611.22 nH。

設計天線形狀為正方環形天線,如圖6所示。

正方環形天線的電感滿足以下經驗公式:

其中,μ0=4π×10-7H/m,K1=2.34,K2=2.75,dout和din分別表示外徑和內徑,N為匝數。采用Grover算法,計算所設計天線實際電感Lant‘,即:

其中,L是每條線段的自感,s是線段數量為24,M是天線每段之間的互感。可得所設計標簽天線的電感實際值:Lant’=1 611.39 nH和理想天線電感Lant=1 611.22 nH誤差:

可見誤差極小,精確度極高,可以滿足需求。

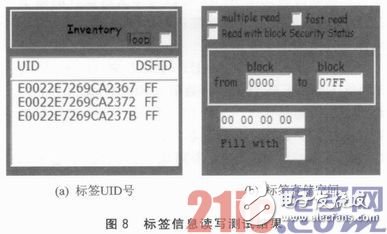

3 系統測試

本文設計標簽實物圖如圖7所示,右上方為3個M24LR64,右下方為I2C總線接口。在上位機對嵌入式RFID讀卡器進行標簽信息讀寫,結果測試圖如圖8(a)所示,其中顯示的為每個M24LR64的唯一標識號,即UID號;如圖8(b)所示,可以向標簽中任意存儲空間寫入數據并讀出。由此可見,能夠成功地對3個M24LR64進行讀寫操作,沒有遮擋物的讀寫距離為6.8 cm,實現了大容量標簽的設計。同時,I2C總線接口的測試顯示,本文設計的嵌入式RFID讀卡器能夠對其進行有線讀寫。

實驗室環境下,標簽和讀卡器之間相隔玻璃瓶、木桌、塑料制品,標簽能夠穩定讀取三個芯片的概率約為99%,穩定讀取距離至少為5 cm。由此可見,該讀卡器和標簽在有一般遮擋物時,在穩定讀取和讀寫距離方面均滿足一般需要。

結語

本文詳細介紹了基于STM32103VET6微處理器,配合CR95HF射頻芯片的嵌入式RFID讀卡器設計。同時,設計了一款與讀卡器匹配,存儲容量可達24 KB的無源RFID標簽。經實際測試,設計的標簽能與讀卡器進行準確的無線讀寫,并能通過I2C總線接口連接到微處理器實現有線通信,具有功耗低、便攜等特點。本設計應用范圍廣,尤其適用于數據量大、傳輸速度相對較高的移動應用的場合。

電子發燒友App

電子發燒友App

評論