引言

射頻識別(Radio Frequency Identification,RFID)是利用微波進行雙向數據傳輸的一種非接觸式射頻自動識別技術。RFID系統具有使用壽命長、低功耗、數據傳輸快速、穩定、安全、可靠,適應性和抗干擾性強等優點,已廣泛用于工業控制、消費類電子、醫療電子、現代物流和校園一卡通等方面。RFID技術是現代物聯網的核心技術。我國研究RFID技術起步比較晚,受軟件和硬件等條件限制RFID技術還未真正實現大規模應用,大多數屬于中、低頻數據傳輸,距國外先進技術還有一段距離。本文重點介紹基于Altera公司Cyclone系列FPGA和ISO1800 0-6C標準超高頻RFID讀寫器的軟硬件實現方法。

1 系統原理和結構

1.1 RFID系統原理

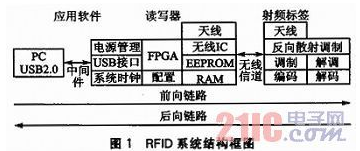

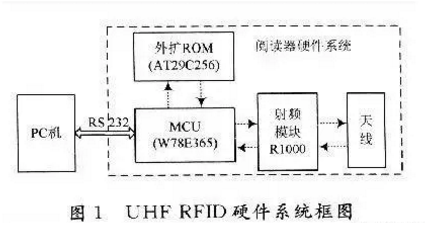

典型RFID系統由讀寫器(Reader)、射頻標簽(RFIDTag)、天線(Antenna)、中間件(Middle Ware)和應用程序(Application Ware)5部分組成。RFID系統結構框圖如圖1所示。讀寫器安裝在固定位置,通過USB與PC連接,實現數據通信與讀寫,讀寫器對射頻標簽操作實現用戶數據更新與存儲。由于系統基于ISO18000-6C標準,射頻標簽要符合該標準,實現用戶數據存儲;讀寫器由編解碼電路、數據存儲電路、射頻前端收發電路、天線、電源電路等構成;天線接收和發送超高頻微波信號;中間件、中間信息和數據處理軟件,對射頻讀寫器和中間件事件過濾、聚合和計算,抽象出對應用軟件有邏輯意義的算法;應用程序直接面對用戶人機交互界面。由應用軟件操作讀寫器,讀寫器收發微波信號修改用戶射頻標簽,應用軟件是用戶體驗和判斷RFID系統成功的一個重要因素。

1.2 RFID讀寫器原理

基于FPGA RFID讀寫器可分為3個模塊:FPGA最小系統、USB串行總線接口電路、RF信號收發電路。FPGA最小系統包含FPGA現場可編程邏輯陣列、JTAG配置電路、系統時鐘電路、數據存儲電路、顯示電路、電源電路。RFID讀寫器控制核心用Altera公司Cyclone系列的EP1C3T144芯片。由于FPGA基于SRAM技術,下載配置芯片用Altera公司配套的EPCS1,下載模式采用JTAG模式,20 MHz有源時鐘晶振,0.3寸共陰數碼管,外接5 V直流電源,經兩級LM1085轉換為3.3 V和1.5 V電壓,為FPGA內核和引腳供電。數據存儲芯片選用Catalyst公司CMOS技術芯片EEPROMCAT24WC02,通過I2C總線與FPGA連接。USB串行總線接口芯片采用南京沁恒公司的USB通用接口芯片。RF信號收發模塊選用Chipcon公司的SmartRF03技術和0.18μm CMOS工藝的CC1100芯片作為微波信號收發前端,通過SPI總線與FPGA連接。

在RFID系統中,讀寫器是連接射頻標簽和PC機客戶端的核心,通過對讀寫器命令操作,實現用戶數據修改、存儲等操作。RFID讀寫器與標簽數據傳輸可以分為從讀寫器到標簽前向鏈路和標簽到讀寫器后向鏈路,前向鏈路與后向鏈路采用半雙工方式通信,數據傳輸采用ASK調制,前向鏈路采用PIE碼,后向鏈路采用Miller碼,系統采用CRC-16校驗碼和特殊防沖突算法保證讀寫正確。RFID通信可分為2步:閱讀器首先獲得在輻射范圍內標簽ID號,然后對ID號符合要求的標簽進行讀寫相應操作。讀寫器與上位機USB數據通信,通過USB設備枚舉完成HID人機接口設備識別和數據讀寫。

2 系統硬件電路設計

2.1 Cyclone EP1C3T144 FPGA最小系統

FPGA最小系統包含可編程門陣列、電源電路、時鐘電路、復位電路、配置電路、濾波電路。現場可編程門陣列采用EP1C3T144。它基于1.5 V,0.13μm全銅SRAM工藝、TQFP144封裝;104個I/O口,支持各種I/O標準;支持LVDS,數據傳輸率為311 Mbps;2910LE邏輯單元、

288 Kb RAM、1個PLL鎖相環,支持66 MHz 32位PCI標準,支持外接133 MHz DDR SDROM;單獨有源時鐘接口,外接20 MHz頻率的有源晶振;專用配置電路接口,3.3 V LVTTL供電。FPGA基于SRAM技術,掉電數據易失,采用Altera公司配套的EPCS1JTAG下載模式。系統采用硬件和軟件復位:硬件復位接FPGA nconfig引腳,按下此鍵FPGA代碼從EEPROM重新配置;軟件復位是編寫代碼時設置reset引腳,按照代碼運行。

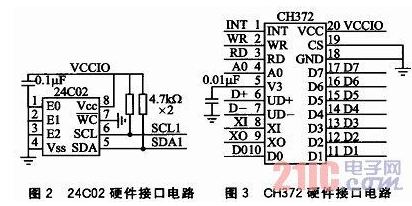

由于FPGA芯片內部EEPROM空間有限,FPGA芯片外掛一個2KB EEPROM 24C02,24C02與400kHz I2C接口兼容。供電電壓為1.8~6.0V,供電電流為3mA,具有頁寫緩沖器和寫保護功能,SOP8封裝。它還具有讀寫次數多、保存時間長、功耗低的特點。24C02硬件接口電路如圖2所示。

2.2 USB串行總線接口電路

CH372簡易USB通用串行總線接口集成電路,兼容+5 V和+3.3 V供電,最大工作電流為30 mA,外接12 MHz頻率晶振,20引腳SOP封裝;兼容USB2.0數據傳輸協議,支持HID設備熱插熱拔,內置USB底層通信協議,自動完成標準USB事件枚舉;支持數據控制傳輸、批量傳輸、終端傳輸;默認鏈接端點0所有事件,FPGA負責數據傳輸與處理,使用方便,CH372硬件接口電路如圖3所示。

2.3 CC1100 RF收發電路

CC1100是一款極低功耗UHF收發集成電路。其通信效果好、抗干擾性能強、穿透力強、靈敏度高;可自由設置收發頻率,可設置范圍為300~348 MHz、400~464MHz、800~928 MHz,可編程控制數據傳輸速率最高可達500 kbps,4線SPI(SI、SO、SCLK、CSn)接口。CC1100正常工作電壓為3.3 V,最高輸入電壓3.6 V,每個引腳輸入電壓應相同。868~915 MHz發送模式輸出功率為+10 dBm,電流為30 mA,接收最大功率為+10 dBm,硬件自動CRC校驗,支持ASK調制解調,調整外圍元件可方便調整收發頻率。CC1100采用數據緩沖技術,具有2個64字節FIFO,緩沖發送和接收數據。CC1100可軟件設置RF發送功率、收發模式、調制格式、信道選擇和帶寬、數據傳輸速率、整機工作模式等。

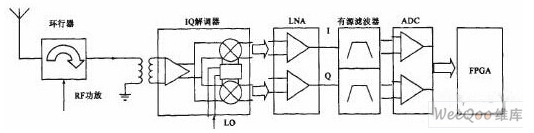

CC1100屬于半雙工通信,接收和發送在射頻控制模塊RF CONTRON控制下分時進行,解調由積分器向下積分完成,AGC電路控制回路增益;調制基于直接頻率合成,載波信號由晶振與內部PLL電路產生,發送模塊和接收模塊稍有區別。接收模塊包括:低噪聲放大器LAN、積分器INTEGRATION、模數轉換ADC、解調器DEMODU-LATOR、向前數據誤差處理器FEC/INTERLEAVER、包處理PACKET HANDLER、接收數據緩沖器RXFI FO、數字接口電路DIGITAL INTERFACE TO MCU;發送端與接收端不同的模塊有:壓控振蕩器VCO、混頻器MIXER、發送數據緩沖器TXFIFO,數據收發由不同模塊分時完成。

CC1100具有2種工作狀態——空閑狀態和工作狀態,每種狀態對應電流不同。空閑狀態可分為等待WAIT狀態,內部電流1.9 mA;睡眠SLEEP狀態,內部電流400~900 nA;晶振的停振狀態僅維持寄存器值不變,內部電流160 nA;工作狀態可分為接收(RX)和發送(TX)狀態,接收狀態根據接收信號強弱內部電流在14.2~15.4 mA范圍變化。發送狀態下,發送信號功率大小隨工作電流變化。14 mA時發射功率為-10 dBm,29 mA時發射功率為+20 dBm。根據工作狀態調整工作電流,可實現整機最低功耗。

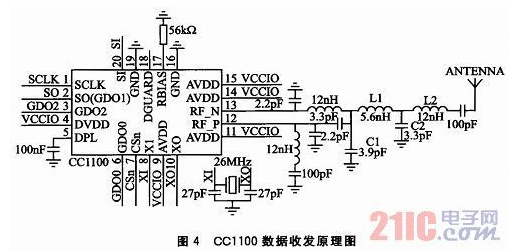

由于采用ISO18000-6C標準射頻空中接口協議,系統采用889 MHz發射和接收頻率,改變CC1100第12、13引腳外接電容C1、C2,電感L1、L2的參數可調整射頻收發頻率,發射天線采用50 Ω偶極子天線。12、13引腳LC網絡器件參數可由軟件SmartRF studio仿真得到,參考CC1100官方DATASHEET,根據實際情況微調。CC1100數據收發原理圖如圖4所示。

3 系統軟件設計

3.1 RF收發芯片CC1100軟件設計

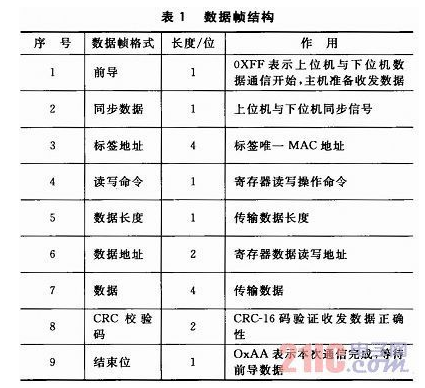

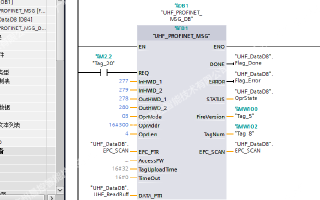

CC1100操作包括芯片數據讀寫、寄存器與命令濾波器設置訪問、數據包與數據傳輸速率設置、FIFO訪問、低功耗策略等。RFID讀寫器中CC1100數據傳輸采用同步連續方式,支持硬件數據包處理、FIFO緩沖、數據白化、交錯和前向處理。CC1100數據幀包含前導、同步數據、標簽地址、數據長度、讀寫命令、數據地址、數據、CRC校驗碼、結束位。其中前導數據、同步數據通過CC1100寄存器設置硬件自動完成、CRC校驗碼硬件自動完成,其他數據需軟件設置或配置寄存器。數據幀結構如表1所列。

CC1100通過4線SPI接口與FPGA連接,對內部不同寄存器和不同命令濾波器操作完成數據收發。當SO引腳讀數據時SCLK必須在第一個上升沿前被拉低,一個周期內SCLK下降沿完成1位數據建立,上升沿數據保持;CSn=0片選信號有效,數據正常傳輸;在SCLK控制下SI為同步數據輸入,SO為同步數據輸出。數據通信完成后SCLK保持低電平,等待下次數據通信。CSn=1時CC1100為降低功耗處于睡眠或晶振停振狀態。CC 1100采用電磁波激活WOR低功耗技術,CPU處于深度睡眠等待接收狀態,數據到來后,無須喚醒CPU而直接存儲到RX FIFO。

CC1100內部可分為配置寄存器地址(0x00~0x2F)和命令濾波器地址(0x30~0x3F)。配置寄存器設置SPI引腳狀態、數據調制方式、編碼方式、校驗方式、數據傳輸速率、信道帶寬等;寄存器狀態字STATE第6位到第4位查詢當前工作狀態,000為空閑狀態,001為接收狀態,010為發送狀態;命令濾波器設置當前工作狀態,SRX 0x34=0xFF時啟用接收模式,STX 0x35=0xFF時啟用發送模式。CC1100分別具有一個64位RX FIFO和TX FIFO,STATE狀態字監測FIFO是否溢出。讀RX FIFO前必須保證FIFO不為空,寫TX FIFO前必須保證FIFO為空,否則讀寫數據將出錯。CC1100寄存器與濾波器設置可以通過軟件SmartRF Studio得到最佳配置。

CC1100數據傳輸速率通過MDMCFG3.DRATE_M和MDMCFG4.DRATE_E配置寄存器和晶振頻率設置,先設定數據傳輸速率和晶振頻率,計算出MDMCFG3.DRATE_M和MDMCFG4.DRATE_E配置寄存器值。

3.2 ISO18000-6C空中接口協議

傳輸頻率范圍:860~960MHz。

調制方式:ASK,每個信道500kHz,可設置52個信道,標簽采用反向散射調制。

最大發射功率:4W。

編碼方式:PIE,Miller,FM0。

校驗方式:CRC-16。

數據傳輸速率:40~640kbps。

4 系統實驗結果和結論

RFID系統測試包括軟件測試、硬件測試、穩定性和EMI測試。軟件測試包括用戶軟件、中間件、標簽軟件、編解碼信號測試;硬件測試包括發射功率、收發距離、收發夾角、標簽數量;EMI和穩定性測試包括復雜電磁干擾測試等。用到的儀器有數字存儲示波器、矢量分析儀、邏輯測試儀、頻譜分析儀、NRT功率計測試儀。它們對讀寫次數與數據正確率、讀寫器一標簽距離與數據正確率、天線發射功率與數據傳輸距離、天線對信號放大倍數與信號頻率關系進行相關測試與數據分析。

經測試,RF放大器對889 MHz信號放大倍數最大,讀寫器與標簽最大數據傳輸速率為240 kbps;傳輸距離在1 m內天線發射功率為1.1 dBm,調整發射功率,最大傳輸距離可達3 m。基于IS018000-6C標準射頻標簽協議RFID便攜式系統工作穩定可靠,只需USB與PC機連接便可實現讀寫器與PC機數據通信,簡單、方便、可靠,可用于工業控制、消費類電子、食品安全追蹤、現代物流、校園一卡通等場所。

責任編輯:ct

電子發燒友App

電子發燒友App

評論