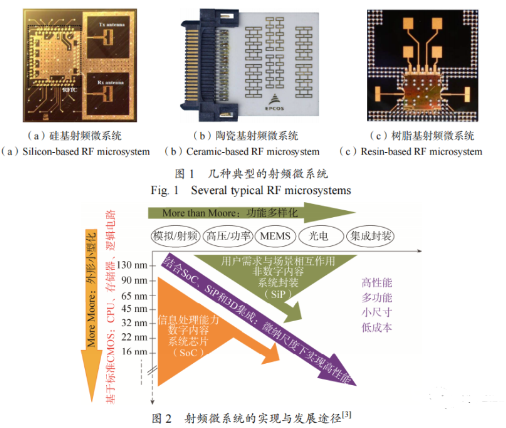

傳統的封裝技術已難以滿足飛速發展的電子信息系統的高密度集成需求,隨著先進封裝技術的發展,射頻微系統成為小型化電子產品的重要組成部分,可以在微納尺度下實現高性能電子系統,為電子信息設備多方面的技術變革提供了重要技術路徑[1],典型射頻微系統如圖1所示。自射頻微系統技術問世以來,美國、日本等發達國家就將其列為現代前沿核心技術,并相繼實施了“超越微縮(Beyond Scaling)”、“電子復興ERI計劃(Electronic Renaissance Initiative)”、“E-CUBES計劃”等項目計劃。另外,臺積電、Intel、IBM等公司也紛紛對射頻微系統的新技術、新工藝展開研究并取得不菲成果。掌握射頻微系統技術對于國家實現核心技術自主可控具有重要意義,因此,我國近年來對射頻微系統技術高度重視并進行深入研究[2],先后大力支持了遙感信息處理微系統集成、彈載多模通信等方向的課題研究工作。

本文首先對射頻微系統的發展與應用進行分析,接著梳理總結了射頻微系統幾種典型技術的內涵及研究現狀,最后針對國內射頻微系統的發展現狀,探討了現階段主要存在的問題,并對射頻微系統未來發展策略提出了一些建議。

1 射頻微系統技術概述

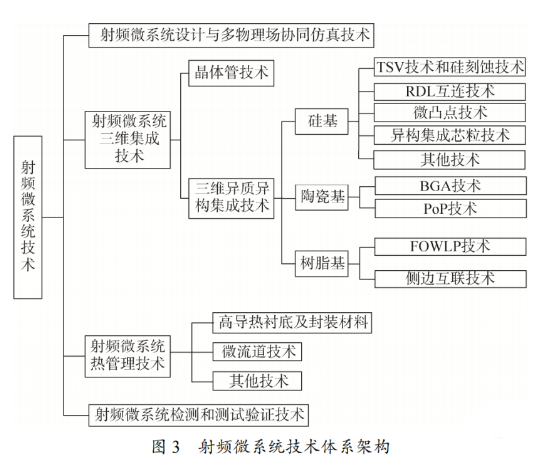

摩爾定律已經逼近極限,目前集成電路主要沿三個方向發展:延續摩爾定律(More Moore)、拓展摩爾定律(Morethan Moore)以及超越CMOS(Beyond CMOS)。而射頻微系統技術融合了三維異質異構集成、微納工藝等技術,可將延續摩爾定律和拓展摩爾定律的技術優勢結合起來,實現高性能、多功能、小尺寸、低成本的電子封裝。射頻微系統的實現與發展途徑如圖2所示。

1.1 射頻微系統技術在軍民領域的應用

射頻微系統主要針對雷達、通信、電子對抗、物聯網等產品的低成本、小型化、多功能化等需求,在航空航天、船舶、武器等軍事領域,以及5G移動通信、WiFi、生物醫療、工業控制、汽車電子等民用領域都有著巨大的生命力。

在軍事領域,射頻微系統作為支撐航天工程和武器裝備戰略發展的核心技術之一,能夠在大幅減小武器系統的體積與功耗的同時兼顧多功能集成和智能化,從而增強武器裝備在作戰時的機動性、可靠性和隱蔽性[4]。美國、德國、日本等發達國家已取得較多成果,研制出了采用射頻微系統技術的新一代雷達、通信、電子戰等先進武器裝備。2013年,美國NASA成功發射的4顆采用微系統技術開發的手機衛星尺寸與馬克杯大小相當,可以滿足多種系統需求[5]。2015年9月,日本電報與電話公司(NTT)、富士通和美國NIST研究所采用微納制造工藝,將聚酰亞胺作為印制電路板,結合太赫茲高靈敏放大器芯片集成技術,合作研發出世界首個內置天線的緊湊型300GHz接收器,體積僅為0.75cm3。2016年4月,德國Fraunhofer研究所采用InGaAs器件技術和特制印刷電路板研發出了一款高頻微系統模塊,體積僅為78mm×42mm×28mm,可使雷達模塊體積縮減至煙盒大小。2018年,美國DARPA與佐治亞理工學院等機構合作啟動了三維單芯片系統3DSoC(3DSystemonChip)項目,實現了存儲、邏輯和收發組件等單元小型化、一體化、高性能三維射頻微系統封裝芯片,并于2020年6月的“2020 VLSI技術與電路研討會”上首次對單片集成3D SoC技術與SRAM和RISC-V計算核進行了硬件演示,并宣稱已為3D SoC技術平臺開發了工業級代工工藝設計套件PDK(Process Design Kit)。

在民用領域,射頻微系統已經廣泛應用于短距離無線通信、物聯網、5G通信、智能駕駛等領域。通過TSV技術、晶圓鍵合技術等先進射頻微加工技術,可以大大提高微波收發組件、數據處理器件、高頻存儲器件、高效電源等的集成度,優化產品性能。2015年,英特爾公司[6]通過將收發組件集成于包含天線元件的液晶聚合物LCP(Liquid Crystal Polymer)封裝中,實現了一款集成了18個收發組件的60GHz相控陣射頻微系統,主要用于60GHzWiGig領域,封裝薄至0.41mm。2017年,IBM公司為毫米波5G通信系統開發了一款基于高密度互連HDI(High Density Interconnector)工藝的Ka頻段16通道相控陣射頻微系統[7],尺寸僅為6.85mm×6.85mm×1.61mm。2020年,新加坡A*STAR研究所針對5G應用設計了一款封裝尺寸為10mm×10mm×0.8mm的雙層模壓扇出式晶圓級封裝FOWLP(Fan-out Wafer Level Packaging)射頻微系統[8],散熱能力高達5W。2020年,大陸集團宣布,通過賽靈思公司的Zynq?UltraScale+?MPSoC平臺,開發出了新型高分辨率遠程4D成像雷達傳感器ARS540,可在智能駕駛中實現復雜駕駛場景的多目標跟蹤、快速識別相應道路潛在的危險物體等功能。

1.2 射頻微系統典型技術

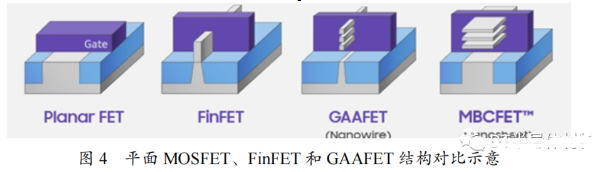

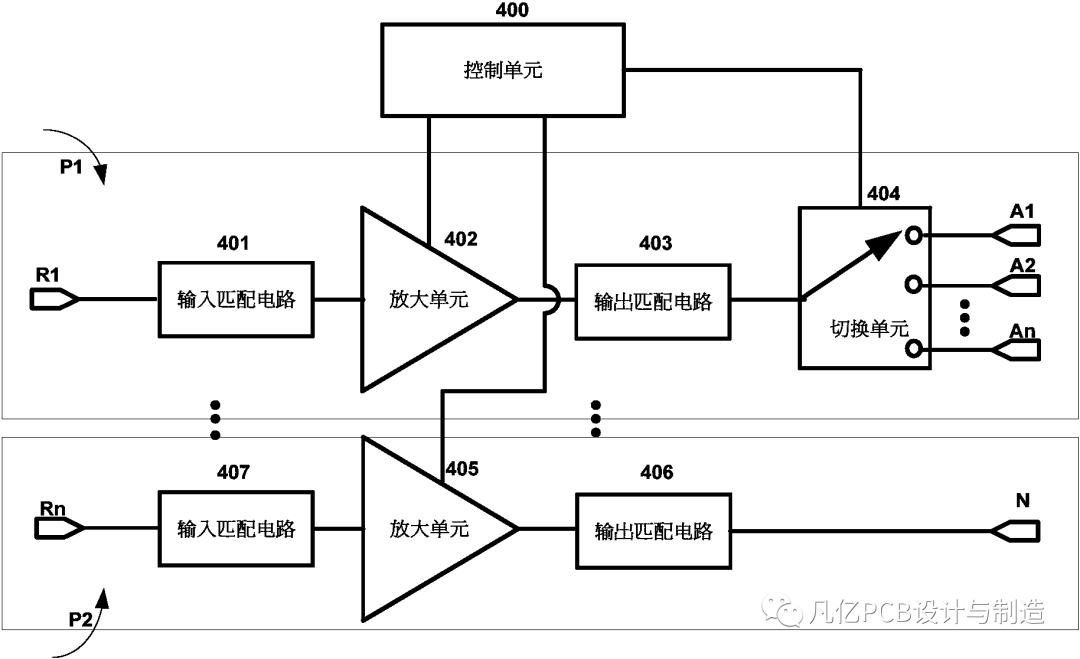

射頻微系統典型技術主要包括射頻微系統設計與仿真、射頻微系統三維集成技術、熱管理技術以及檢測和測試驗證技術。射頻微系統技術體系架構細分圖如圖3所示。

2 射頻微系統設計與多物理場協同仿真技術

射頻微系統設計主要是根據微系統的應用需求對各功能模塊進行合理設計及布局,以實現三維射頻微系統封裝中電路信號的完整性要求,避免信號串擾問題和垂直互連結構信號過渡不連續問題。

在射頻微系統技術實現的產品工作過程中,電、磁、熱、力等物理場并不是單獨存在和作用的,各物理場間往往會相互耦合、相互影響[9],因此,在射頻微系統封裝的設計中需要進行多物理場協同仿真研究。通過對射頻微系統中光、機、電、磁、熱、流體、應力應變等多維度物理場在微小尺度下的耦合與互擾進行研究,以解決多元參量間相互約束和平衡問題,進而采用一些特殊的設計來提高射頻多芯片的電氣性能,并減少多物理場對產品可靠性的影響。2016年,美國伊利諾伊大學香檳分校針對集成微流道冷卻的三維射頻微系統,提出了一種包括全波電磁、流體、瞬態共軛熱交換的多物理場協同仿真技術[10],其通過對流體流動的控制方程與溫度解耦解析出流體的速度場,全波電磁和瞬態共軛傳熱分析通過溫控材料來進行耦合迭代分析,實現了精確、高效的多物理場協同仿真,并驗證了微流道散熱的有效性以及對3D射頻微系統高頻特性的熱影響。

3 射頻微系統三維集成技術

結合延續摩爾定律與拓展摩爾定律的射頻微系統三維集成技術,可以分為晶體管技術、高密度封裝功能基板制造技術、三維異質異構集成技術。其中,晶體管技術主要在延續摩爾定律方面進行技術研究和突破,以獲得按比例微縮的高性能芯片;三維異質異構集成技術主要用于拓展摩爾定律,通過先進封裝技術,在成本相對低廉的情況下實現系統小型化、多功能和高性能。

3.1 晶體管技術

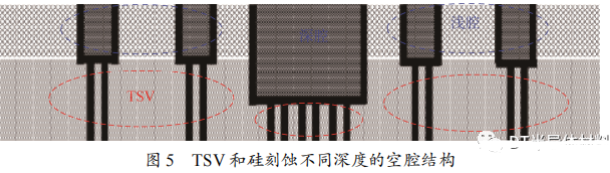

隨著摩爾定律的發展,傳統平面MOSFET結構的限制使得半導體工藝逐漸難以滿足“等比例微縮”的尺寸發展需求。為繼續向微型化發展,一種新結構——三維結構的鰭式晶體管FinFET(FinField-EffectTransistor)——應運而生。英特爾、三星、臺積電陸續在其工藝制程節點上推出了各自的FinFET技術。FinFET技術最主要的特點是柵極(Gate)三面環繞源極(Source)和漏極(Drain)之間的溝道,由于增加了柵極對溝道的控制面積,因此能有效減小漏電流,增強溝道控制能力,進一步縮短柵極長度,減小晶體管面積。

為應對芯片采用FinFET技術微縮到7nm后的瓶頸,三星、英特爾等突破性地提出了環繞柵極場效應晶體管GAAFET(GateAllAroundFieldEffectTransistors)技術。GAAFET技術在給定的區域內封裝了更多的高性能晶體管,其與FinFET技術相比,減小了標準單元的寬度。GAAFET技術可以分為兩種,一是常規GAAFET,使用三層納米線(nanowire)替代FinFET的鰭;二是多橋通道場效應晶體管MBCFET(Multi-Bridge-ChannelMOSFET),其使用更厚更寬的納米片(nanosheet)作為晶體管的鰭,增加了溝道和柵極間接觸面積,從而增大了電流通過量[11,12]。各結構對比如圖4所示。

3.2 三維異質異構集成技術

射頻微系統采用三維異質異構集成技術,可將不同工藝、材料甚至生產廠家的芯片或功能模塊立體集成在同一封裝內,實現產品小型化、高集成和多功能的目標。其中,常用的高密度封裝基板主要有硅基板、陶瓷基板以及樹脂基板等。

3.2.1 硅基

硅基射頻微系統在三維集成時通常采用硅通孔TSV(ThroughSiliconVia)、再布線RDL(RedistributionLayer)等工藝技術實現多層硅片垂直互連,并且采用硅刻蝕技術將芯片內埋入基板內達到進一步縮減體積的目的。

3.2.1.1 TSV技術及硅刻蝕技術TSV技術是2.5D/3D集成的關鍵技術,TSV硅基板表面互連線以及內部硅通孔可實現三維異質異構集成、縮短元器件間距,進而提高電路集成密度,實現射頻微系統的小型化和低功耗。TSV技術大概思路是在硅晶圓上刻蝕出通孔后,向孔內填充銅等導體材料,以建立硅片上下表面信號互連通道。其工藝主要實現步驟包括:通孔刻蝕、絕緣層鋪墊(防止產生漏電流,材料通常為SiO2)、通孔填充、圓片減薄以及晶片堆疊與鍵合[13]。

硅刻蝕技術可依據要嵌入的芯片厚度并采用干法刻蝕工藝或濕法刻蝕工藝在硅基板上刻蝕出不同深度的空腔,從而將芯片埋入硅基板內部,減薄厚度,進而提高系統集成度。目前,已有不同深度空腔的一次性刻蝕工藝,即先用濕法刻蝕工藝做出深腔的開窗,然后用干法刻蝕一次性將深腔和淺腔刻出,工藝流程簡單。結構如圖5所示。

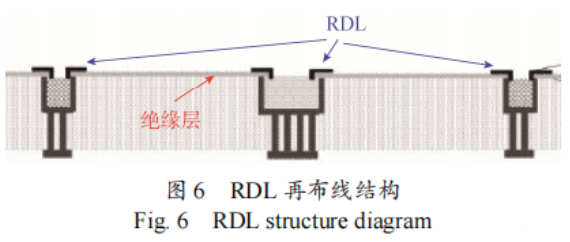

3.2.1.2RDL互連技術再布線RDL技術是通過晶圓級金屬布線制程和凸塊制程改變原設計的芯片線路接點,使集成芯片適用于不同的封裝形式。硅基板RDL大致流程為:先在硅基板上涂覆絕緣層,曝光顯影再電鍍新的金屬導線路徑以連接原有接點和新的凸塊,進而重新分布接點,實現高密度、高精度布線要求。工藝通常有兩種:大馬士革工藝和聚合物RDL工藝。如圖6所示,內埋芯片可用RDL互連線引出信號到基板表面,結合FAN-OUT扇出工藝,能有效應對引腳較多的芯片。同時,RDL優勢還包括:互連線高度較低,上蓋板不需要刻蝕深腔;相對于引線鍵合,其可承受更持久的高溫和更高強度的振動沖擊,增加了元件的可靠性且能取代部分系統設計,減少設計時間等。

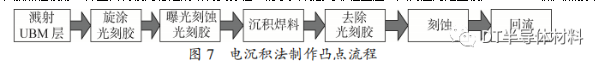

3.2.1.3 微凸點技術硅基射頻微系統在進行三維疊層時,常用技術主要有微凸點技術、高分子粘接、Au-Sn共晶焊接等[14],其中微凸點互連技術采用合金焊料和金屬,電氣互連和散熱性較好,并且具有較為穩定的結構支撐性,易于實現高可靠性互連,因而應用范圍較廣[15]。微凸點技術由IBM公司在20世紀70年代提出,由于其優良特性,直到今天仍備受微系統封裝設計人員的青睞。目前,微凸點的制備方法主要有電沉積法、焊料濺射法、模板印刷焊料法等。其中,電沉積法制作凸點流程[16]如圖7所示。

3.2.1.4 異構集成芯粒技術異構集成芯粒(chiplet)技術起源于多芯片模塊,由AMD公司在上世紀70年代為降低半導體芯片的設計成本而提出。芯粒是可以集成到低延遲中介層上的裸片,不同的裸片可以使用不同的工藝節點制造,甚至可由不同的供應商提供。芯粒設計類似于SoC但價格低于完全集成的SoC設備,其突破了傳統的在單個硅片上實現所有功能的限制,采用模塊化方法,通過多個被單獨制造的不同功能的芯粒來構建硅系統,從而減少設計時間和成本[17]。2017年8月,DARPA啟動通用異構集成和IP復用策略(CHIPS)項目,通過添加較小的專用芯粒來設計射頻微系統。CHIPS項目的創新之處在于不使用傳統印刷電路板而是用硅中介層(interposer)來連接芯粒,芯粒間通過die-to-die技術進行內部互聯,從而實現間距更精細的互連集成。

3.2.1.5其他技術Co-EMIB技術是英特爾在公司已有的嵌入式多核心互連橋接EMIB(Embedded Multi-DieInterconnect Bridge)和FOVEROS基礎上的進一步創新,在2019年7月的SEMICONWest會議上被提出。其結合了EMIB和FOVEROS3D封裝技術的優勢,將多個FOVEROS元件互連為一整個封裝,可以實現其高I/O密度、高帶寬、低功耗、多功能集成。

除以上舉例的幾種硅基射頻微系統異質異構集成技術外,還有許多先進技術,如臺積電將小外形集成電路封裝SoIC(Systemon Integrated Chips)、集成扇出型封裝InFO(Integrated Fan Out)、晶圓級封裝CoWoS(Chip-on-Wafer-on-Substrate)等3DIC平臺整合在一起推出的3D Fabric先進封裝技術;歐洲e-CUBES項目[18]基于TSV技術和空心通孔及金釘凸點鍵合技術,通過晶圓級封裝可實現嵌入式器件的芯片堆疊3D-WLP(Wafer Level Packaging)和器件級別的三維射頻微系統3DSoC、可壓縮微互連CMIs技術[19]等等。更多先進異質異構集成技術還在不斷地涌現發展,硅基射頻微系統在未來有著巨大的潛力。

3.2.2 陶瓷基

射頻微系統的陶瓷基板采用共燒陶瓷技術制備。由于燒結溫度不同,共燒陶瓷[20]主要分為高溫/低溫共燒陶瓷HTCC/LTCC(High-Temperature Co-fired Ceramic/Low-Temperature Co-fired Ceramic),HTCC多層基板具備更高的機械強度和散熱系數,化學性能也更為穩定,而LTCC基板一般電性能較好、并且可內埋無源元件,但機械強度和導熱率較低。陶瓷基射頻微系統多采用球柵陣列BGA(Ball Grid Array Package)技術和疊層封裝技術實現立體封裝。

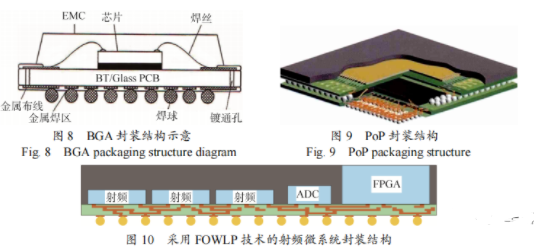

3.2.2.1 BGA技術BGA技術常用于多引腳小尺寸電子產品的封裝。BGA封裝結構如圖8所示,其可在封裝基板背面以面陣列形式排列的焊球代替傳統鍵合金絲和連接器,用于與外部電路互連并傳遞射頻信號[20],與傳統表面貼裝SMT(Surface Mounted Technology)封裝相比,具有裝配簡單、成本低,布線難度小、互連距離短、尺寸小、焊球可自動對齊等優點。根據基板材料的不同,可以將BGA封裝分為塑封球柵陣列PBGA(Plastic Ball Grid Array)、載帶自動鍵合球柵陣列TBGA(Tape Ball Grid Array)和陶瓷球柵陣列CBGA(Ceramics Ball Grid Array)。其中,CBGA封裝基板材料一般為共燒陶瓷基板。BGA技術近年來廣受CPU等高密度、高性能、多引腳IC和射頻微系統封裝設計者的青睞,如英特爾Pentium大功率高集成度CPU芯片采用了CBGA封裝,并在外殼安裝微型風冷裝置,以提高電路性能與可靠性。

3.2.2.2 PoP技術疊層封裝PoP(PackageonPackage)技術在2007年隨iPhone一起進入公眾視野。PoP封裝結構如圖9所示[21],其可將先單獨封裝制造的邏輯、存儲和射頻等模塊再垂直堆疊互連集成為一個封裝整體,芯片封裝類型更加靈活,在硅基、陶瓷基、樹脂基的射頻微系統集成中都有應用。如2020年6月,在第70屆IEEE電子元件與技術會議ECTC(ElectronicComponentsandTechnologyConference)上,印度微系統研究人員[22]基于PoP技術和LTCC工藝設計了一款用于5G毫米波通信應用的收發射頻微系統封裝,同時,新加坡A*STAR研究所[23]研究人員也對采用扇出型晶圓級封裝FOWLP方法的PoP射頻微系統封裝展示了一些新的研究發現。

3.2.3 樹脂基

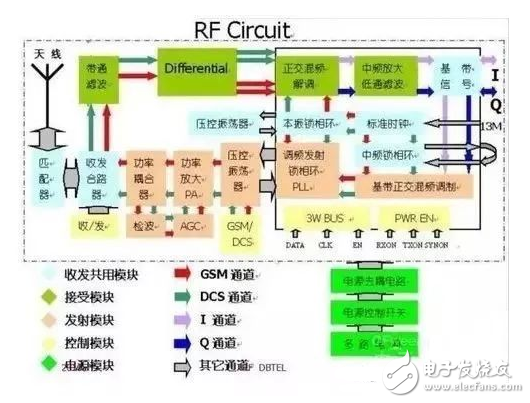

3.2.3.1 FOWLP技術樹脂基射頻微系統通常采用扇出型晶圓級封裝FOWLP方法,通過晶圓重構將多個射頻芯片和數字芯片粘貼為同一區域,然后進行多層再布線并制備凸點,最后進行切割分離,得到能夠與主板射頻互連的一體化微系統封裝[24]。圖10是一種典型的扇出型晶圓級微系統封裝結構,相比于傳統的以引線鍵合技術為基礎的封裝,其在成本、尺寸、性能方面都有突出優勢,并可以實現不同功能材料芯片的系統級異質異構集成。各代工廠都有其獨特的FOWLP方案,如英飛凌的嵌入式晶圓級球柵陣列eWLB(EmbeddedWaferLevelBGA)技術,TSMC的In FOFO WLP技術,三星的FOPLP技術等。

3.2.3.2 側邊互聯技術

基于樹脂封裝的三維射頻微系統,通常先通過層疊的方式對單層微波電路進行立體組裝,然后使用樹脂填充封裝,樹脂封裝脫模后對封裝表面金屬化并刻蝕布線,不同層間的射頻垂直互聯通過采用側邊互聯技術以每層射頻電路端面與側邊表面類共面波導CPW(Co-PlanarWaveguide)結構的形式實現。圖11展示了一個樹脂包封的三維多芯片射頻組件微系統[25]。

射頻微系統最終目的是要滿足產品微小型化、多功能化、低成本化的發展趨勢與要求,晶體管技術、三維異質異構集成技術正是服務于這一目的而誕生和發展的。先進的集成工藝技術帶來可以滿足民用領域和軍事領域應用需求的優異產品,而科技進步帶來的對微系統集成度和性能更高的要求也在推動著射頻微系統集成技術的不斷進步,繼而攀向一個又一個高峰。

4 射頻微系統熱管理技術

“小”是電子產品永恒的追求。隨著微系統集成度和小型化程度的不斷提高,微系統封裝內熱流密度大等問題逐漸變得不容忽視。傳統熱傳導、強迫液冷、風冷等熱管理技術存在著占用空間大、不易集成、散熱效率低等缺點,已經難以滿足高集成度射頻微系統的散熱需求,在保證封裝結構緊湊的前提下如何進行高效散熱已成為國內外團隊的研究重點之一[26,27],現階段射頻微系統常用的熱管理技術有使用高導熱材料襯底和封裝以及微流道技術等。

4.1高導熱材料襯底及封裝基于高導熱材料襯底及封裝進行散熱的方式設計簡單可靠,但對材料的熱導率以及與硅、砷化鎵等材料的熱匹配性等性能要求較高,目前較為常用的高熱導率襯底有多層石墨烯、金剛石、碳化硅等,高熱導率熱沉及封裝材料有金剛石基(銅、鋁、銀)、石墨復合材料等。

DARPA于2011年啟動近結熱傳輸NJTT(Near-JunctionThermalTransfer)項目[28],目的是通過功率器件的局部熱管理,降低半導體器件熱阻抗,其中一項重要內容即為高導熱金剛石襯底。多個研究團隊參與研究并取得了一定進展[29],如雷神公司采用金剛石襯底實現了GaN器件1/5至1/3的熱阻降低;BAE系統公司將金剛石與薄GaN鍵合以減小熱膨脹系數CTE(Coefficient of Thermal Expansion)不匹配影響;諾格公司在碳化硅襯底上刻蝕金剛石過孔提高了芯片散熱效果。這方面國內起步較晚,目前,中電55所已完成了76.2mm多晶金剛石襯底GaNHEMT的轉移鍵合[30]。

國外對高熱導率封裝材料與熱沉研究較早并較為成熟,如金剛石、石墨復合材料已經廣泛用于微電子封裝熱沉。美國勞倫斯利弗莫爾國家實驗室在1995年就開發出了一種熱導率可達600W/(m·K)、CTE與硅相近的金剛石-銅復合材料,并已應用于多芯片模塊的熱管理設計;國內北京研究總院和北科大[31]在2009年制備的金剛石-銅復合材料的熱導率可達503W/(m·K)。石墨復合材料的代表性散熱產品有美國愛美達公司的K-core、珉泰克公司的PYROID熱解石墨等。

4.2微流道技術微流道技術由斯坦福大學的Tuckerman和Pease在1981年提出,并隨著微系統加工工藝的發展而逐漸成熟。相比于傳統散熱方式,微流道技術可將散熱性能提升幾個量級,并且更加易于集成、占用體積更小。2006年,IBM公司在風冷基礎上開發出高熱導界面技術,通過制作的芯片表面樹狀結構將散熱效率提升數倍;之后,蘇黎世實驗室提出噴射沖擊冷卻后再通過樹狀結構迅速回收液體的水冷散熱方案,將散熱效率提升至原先的6倍左右[32];2007年,上海交通大學聯合國家重點研究室設計出了一種新型變截面微流道散熱器,可輸送5×107W/m2的熱通量[33];2012年,DARPA啟動芯片內/芯片間增強冷卻ICECool(Inter-Chip Enhancement Cool)項目[34],目標是探索先進的熱管理技術,其中,嵌入蒸發微流道冷卻技術被最為看好以解決遠端冷卻局限;2017年,普渡大學在芯片間設置分級微孔集分水腔和高長寬比微流道陣列等,微流道散熱效率提升10倍;2018年,歐洲微電子研究中心IMEC(Interuniversity Microelectronics Centre)展示了其3D打印的微流道芯片換熱器,可將熱流密度達100W/cm2的芯片溫升控制在15℃以下。

4.3 其他技術除上述技術外,射頻微系統熱管理技術還在不斷推陳出新。如2015年Kim等[35]人采用熱電薄膜制冷技術設計了一種新型散熱器;2018年,中電26所提出了一種基于微冷控制元件的主動微系統冷卻技術[28],可通過壓電驅動為內部微流道液冷循環提供足夠的壓力與工作流量,進而有效散熱。

5 射頻微系統檢測和測試驗證技術

射頻微系統檢測和測試驗證主要包括以下內容:

①微制造工藝的檢測,如TSV結構的漏電流測試、微納結構的擊穿電壓測試、微凸點形貌測試等微缺陷檢測排查;②射頻微系統的電學性能檢測,如頻率、發射功率、接收/發射增益、噪聲等參數的目標符合性驗證;③射頻微系統的可靠性驗證,如TSV/TGV轉接板、晶圓鍵合、材料外延的評估,射頻微系統模塊力學、熱學可靠性測試與壽命預測等。

目前,國內外多家機構在射頻微系統測試技術方面都開展了一定研究。日本ASET在2008到2012的5年間,發展了關于設計環境、芯片測試等技術,以支持日本夢芯工程項目;我國臺灣地區先進堆疊系統與應用研發聯盟Ad-STAC,整合各種3DIC設計、技術、設備、材料、封裝與測試開展研究,以達到推動臺灣3DIC設備及材料自產化的目的[36];長電科技、通富微電、天水華天等企業均對系統級封裝測試方向進行了多年研發,在模型電參數提取等方面已積累了一定經驗;在我國“02”專項、“973”計劃等的支持下,中科院微電子所與多家研究機構聯合,對射頻微系統三維封裝設計、TSV測試方法、混合信號芯片測試技術等關鍵技術開展了多項研究并獲得了一定成果[37,38]。

6 射頻微系統發展策略分析

國外的射頻微系統技術起步較早,美國、歐洲、日本等發達國家早在上世紀末已將微系統技術列為先進核心技術,近十年來已通過多個工程項目落地了射頻微系統在設計仿真、三維集成、散熱、封裝測試等方面的各項技術開發和應用成果。目前,各機構仍然在持續探索射頻微系統的新材料、新工藝、新技術。

6.1我國射頻微系統技術發展現狀近年來,我國對射頻微系統技術高度重視。2011年3月,我國完全自主研發的數字處理器芯片“魂芯一號”問世,打破了國外高端數字處理芯片對我國的壟斷;2012年,航天科技集團公司元器件保證研究中心組織系統開展了航天未來片上集成系統論證工作,為航天微系統的發展發揮了重要作用;2014年,國務院頒布的《國家集成電路產業發展推進綱要》中明確指出,到2015年要達到中國廠商占30%左右先進封裝收入的目標;國發(2015)28號《中國制造2025》與國發(2016)43號《“十三五”國家科技創新規劃》將微系統技術作為提升新一代信息技術產業自主發展的重要能力,與新一代信息技術重點進行發展。目前,我國在需求牽引和技術推動下,已先后支持了機載綜合處理、遙感信息處理、彈載多模通信等方向的軍用微系統集成課題研究工作,并取得一定成果和進展,已初步建成了SoC、SiP微系統技術平臺和共享IP庫,目標是統籌國內研究力量打造微系統協同設計生態。

現階段我國與國外射頻微系統發展存在的差距主要有以下幾點:

①射頻微系統架構設計缺乏深入研究,各領域均缺乏統一的微系統體系評價標準。目前我國射頻微系統成果往往以各個高校、研究所獨立研發為主,缺乏統一組織、協同研究的成熟微系統設計架構與研發路線,對微系統產品許多方面的評價要求與方法尚無統一標準,容易出現研究功能重復、性能相近等問題;另外,對產品的檢測和評價多方溝通流程復雜,且可能出現指標要求大大高于應用需求的指標浪費的情況。因此,有必要對射頻微系統產品的架構設計進行深入研究,并規范射頻微系統體系評價標準,建立規范化、通用化射頻微系統技術平臺。

②射頻微系統核心元器件難以滿足航天與武器型號任務以及民用領域應用,仍普遍存在核心芯片依賴進口的情況。在當前復雜的國際環境下,核心技術受制于人不僅會導致產品生產成本高,并且給武器的供貨保障帶來不穩定性;另一方面,可能存在的“芯片后門”也威脅著軍品的安全性,使國防安全存在隱患。因此,迫切需要通過開展國內軍用射頻微系統設計研究,重點掌握相關集成技術,突破關鍵封裝工藝瓶頸,打破芯片外部技術封鎖,實現核心射頻微系統器件的高可靠自主可控。

③射頻微系統多物理場協同設計研究不足,技術攻關矛盾點較多。一方面,由于射頻微系統通常尺寸較小、集成度高,因此往往功率密度較大、對散熱性能要求較高;另一方面,不同的材料優勢側重點不同,往往很難平衡兼顧產品多種可靠性和電氣性能,在技術上需要解決較多矛盾點。這就需要研究人員開展微納尺度下的多物理場協同分析和設計,考慮多維度物理場下電磁場糾纏效應與趨膚效應、信號串擾、熱–力–電耦合匹配等問題,提高產品整體性能。

6.2 我國射頻微系統技術發展思考

結合國內射頻微系統發展現狀,對未來射頻微系統技術發展思路提出了以下幾點建議:

①對射頻微系統進行系統需求與架構的深入論證,制定規范統一的射頻微系統研發流程與評價標準,充分整合利用國內資源,形成以各大高校、工業部門研究機構以及軍民企業為核心的射頻微系統協同研發隊伍,建立微系統異構集成支撐平臺,發展協同創新、合力突破的微系統設計生態。

②優先發展國家最迫切需求的并能較快取得階段性成果的射頻微系統相關技術;重點攻堅突破射頻微系統設計與多物理場協同仿真、三維異質異構集成、熱管理與高可靠設計、微系統測試驗證技術等射頻微系統關鍵技術;鼓勵支持推進射頻微系統重要基礎研究和核心技術自主創新。

③關注射頻微系統方向核心人才培養,不斷為射頻微系統研發隊伍注入高素質的新鮮血液,確保微系統持續有力地蓬勃發展。

7 結束語

射頻微系統技術符合電子信息裝備微型化、智能化、輕質化、多功能化、高性能化的永恒追求和發展趨勢。從技術突破到產業發展,射頻微系統技術已成為全球最具關注度、影響力和市場潛力的先進技術之一,未來必將推動軍事與民用工業的顛覆性進步。為滿足我國航天發射系列任務與新一代武器裝備需要,應結合射頻微系統發展趨勢與系統需求,充分探索和利用微系統現有技術條件,在國家相關政策的大力支持下,通過對射頻微系統技術總體布局、規范標準、協同設計、重點突破,在保障我國射頻微 系統技術快速穩健發展的同時實現技術創新。

原文信息與來源:《射頻微系統技術發展策略研究》 劉德喜,張曉慶,史磊,劉亞威,游月娟

電子發燒友App

電子發燒友App

評論