01

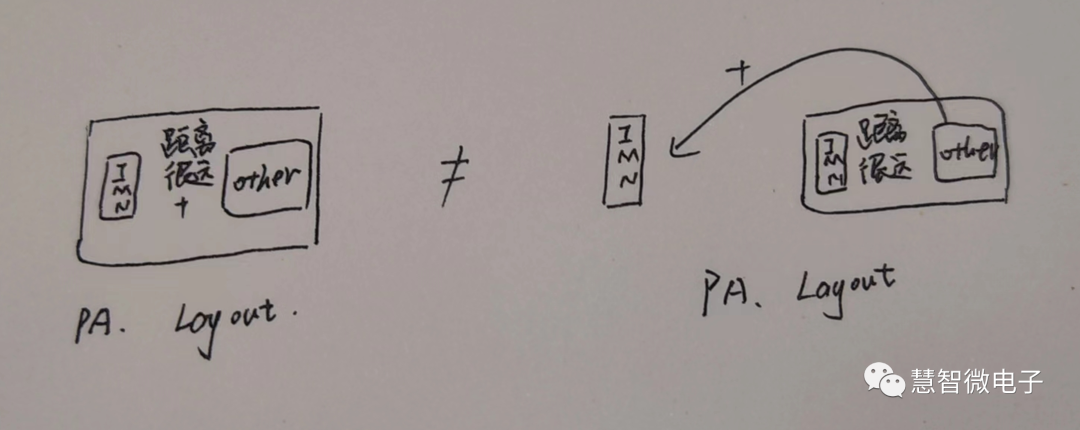

Q:向大家請教一個ADS版圖的仿真的問題,這兩種情形仿出來不一樣是為啥呀?

A:放在一起EM仿真和單獨放不一樣?

Q:是的

A:如果距離很遠,查一下port,用direct模式,不要用TML,如果還是不一樣,查一下地,看看兩種情況的共地。

Q:好的好的,謝謝大佬? ,明天上班看看。

02

有關晶體管寄生容感去嵌入后Loadpull的討論

Q:請教各位大佬們一個問題,把晶體管漏極寄生電容和電感去嵌以后做負載牽引,功率圓中心在實電阻處,但是最大效率圓心不在這個位置,這個是為什么呢?

A:這個看你有沒有去嵌干凈,假設你去嵌干凈了,把輸入和輸出的所有諧波阻抗(到3次)都設成0,再看看。

Q:輸出諧波阻抗設置可以短路,但是源阻抗設成短路,好像HB仿真會報錯。只設置輸出諧波阻抗短路,但源阻抗諧波開路的話,兩個圓心比較接近。

A:換個問法,晶體管的最佳功率點和最佳效率點不同,是由管子漏極的寄生電容引起的嗎?

Q:對,就是這個問題。

A:我覺得你的這個做法可能不能驗證,管子內部的這個寄生電容是非線性的,跟驅動功率有關系,你去嵌的做法是一個線性的操作。

A:不是,你想想,最大輸出功率的時候,你看的只是基波的功率,這個時候你沒管諧波,但是最大效率點,你是用基波功率除以總功耗,其中總功耗包含了DC+基波+諧波。

Q:如果去嵌的模型是飽和功率下提取的,那在這個驅動功率下負載牽引的應該就可以吧,而且諧波阻抗都短路,目前是牽引出來的最佳功率阻抗與理論計算的Ropt差別比較小?

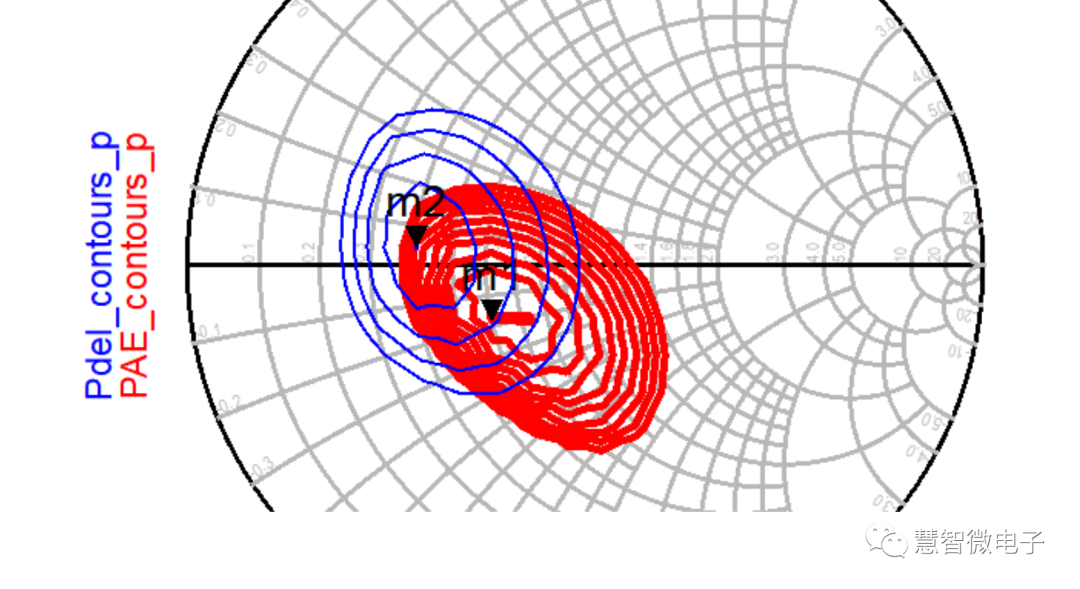

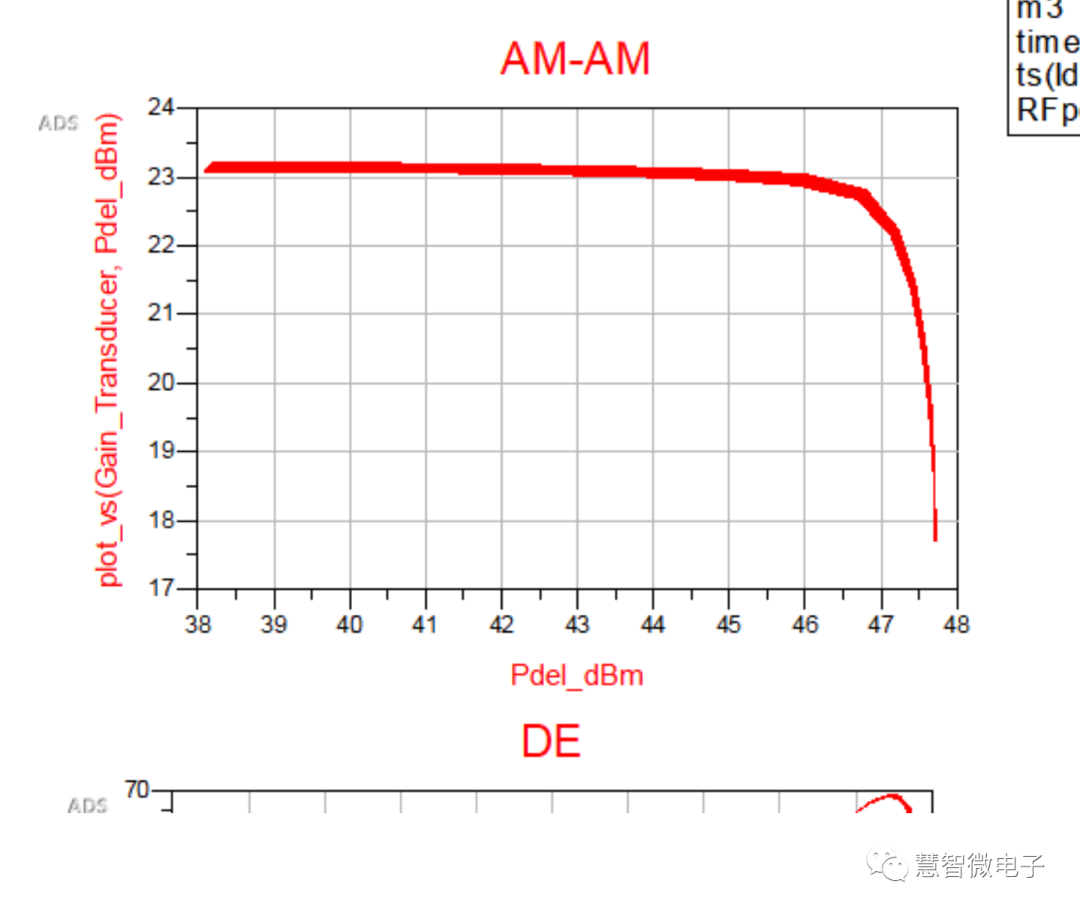

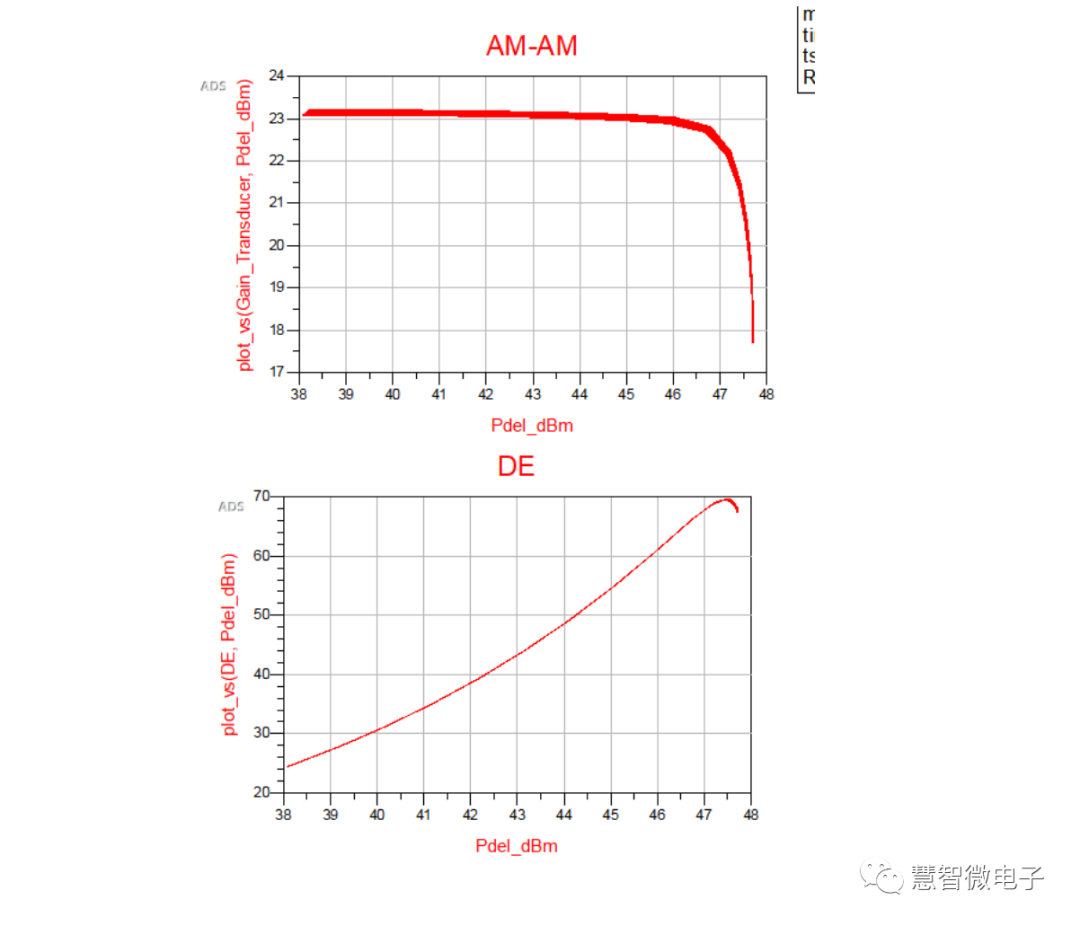

A:稍等,我最近在做一個項目,給你看看我去嵌的效果

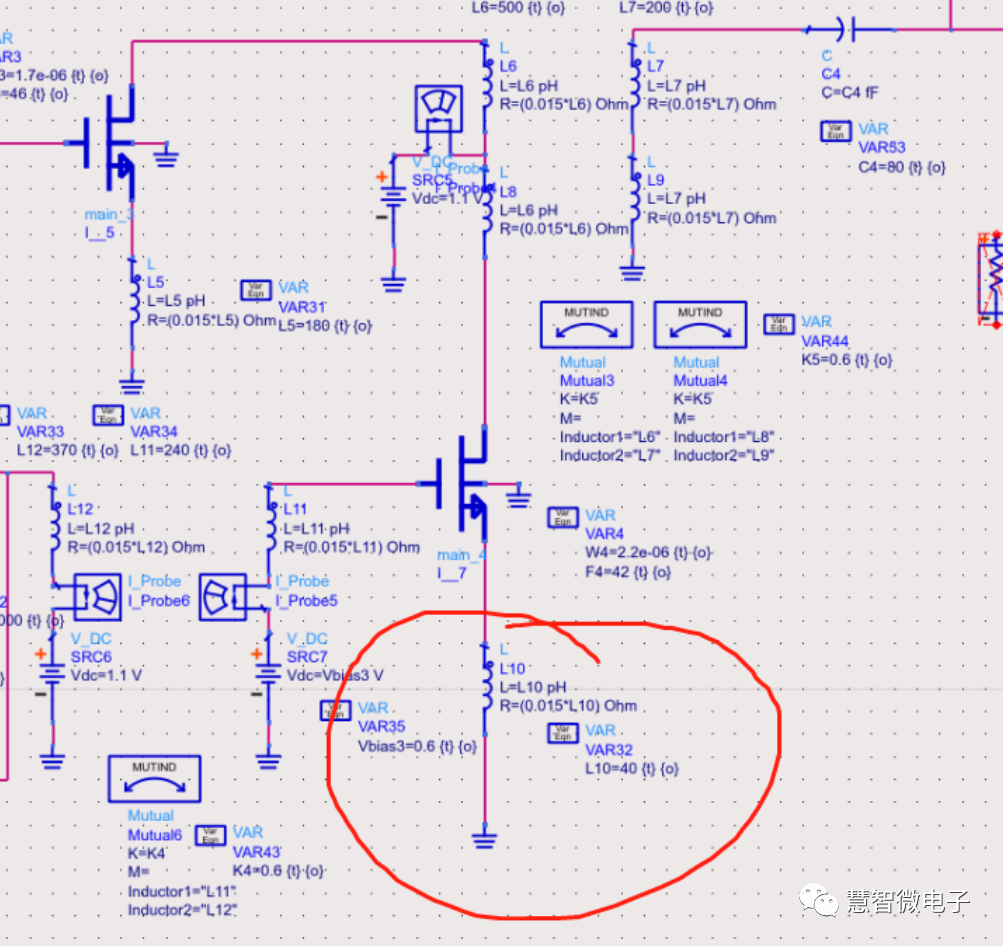

我把輸入和輸出的頻率部分(就是電容和電感)全部去嵌掉了,上面的圖是我從100M掃描到8G的AMAM曲線。

可以看不管是功率還是增益,跟頻率沒有關系,這表示你的去嵌去的是正確的,就是把管子頻率部分去掉了。

Q:輸入和輸出的寄生去嵌之后,最佳功率點和最佳效率點是接近的嗎?

Q:那在實際設計中有什么想對有用的電路結構可以消除掉管子的頻率部分嗎?

A:?看這個圖再加上我上面對于諧波部分的解釋你就知道是不是一樣了

Q:懂了,謝謝。

Q:再請教一下,這種非線性的電容,去嵌方法是什么?

A:去嵌的電路,比如GaN,可以找一篇管子建模的paper看看,里面有現成的電路結構。對于非線性部分,這個其實就要分析和取舍,比如GaN PA,其非線性電容分為幾部分,分別是Cgs,Cgd,Cds,這部分可以分為兩部分提取,一是在冷管情況下提取,比如是C0,冷管提取有一個好處,就是可以避免管子自激。

剩下的就是非線性部分,就要在諧波仿真里面,將C0+X,將X作為一個掃描變量來掃描相關的參數,比如Cgs+X可以側重于小信號增益,Cds+X可以側重于輸出功率,等。

對于GaN而言,其X并非是一個持續變化的量,具體可以參考變容二極管的電容隨電壓變化曲線,有一個拐點,即突變點,突變點前后變化劇烈,而突變之后變化并不劇烈。當然,有源部分的參數提取沒有準確一說,因為影響因素太多了,功率越大的管子提取越費勁,可以研究一下。

Q:去嵌的目的是啥呢,方便后續設計嗎?

A:就是做寬帶的時候比較好選阻抗點,比如輸出阻抗,其變化的由兩部分,一是R,不同的R決定了不同的性能,二是頻率部分,電容和電感,頻率部分決定了不同頻率的阻抗,在做寬帶時不好用Loadpull選阻抗點,可以做參數提取,變化的是R,不變的是頻率部分,就比較好匹配。

Q:不好意思,lgen是指die的哪個位置?

A:Current Generator。

Q:不好意思有個疑問:去嵌的目的是為了寬帶時選擇阻抗點,但我理解,這個頻率部分其實是不消耗能量的,它只是周期性地吸收和釋放能量,所以我原本會覺得做寬帶匹配其實就是通過對匹配網絡的設計讓匹配到的阻抗實部是Ropt,虛部在0附近就行的,如果我這樣理解沒什么問題的話,那好像也不需要去嵌?那去嵌是如何幫助選阻抗點的呢?

A:這個問題如果從頭來解釋比較長,一個小反問,你說的沒有錯,確實是去掉虛部留下實部,那咱怎么能知道我要去掉的虛部是多少,要留下的實部是多少呢?

Q:虛部有影響,從時域上看,虛部就是決定電壓波形和電流波形的相對相位。

A:我這還有一個疑問,我的理解是電阻的響應隨頻率的變化不大,電容得響應隨頻率變化大,跟您提到的方法剛好相反,是因為電容的特性已經由外部的去嵌電路抵消了嗎?

Q:對,在外圍電路加一個負的拓撲就可以抵消了

A:感謝老師。

Q:PA這個東西挺深的,從材料到數學模型到物理模型到實際應用(結構+熱處理等),基本上就是一個射頻系統,有很多問題還學不明白,共同探討,不存在老師一說,嘿嘿

A:請教下,寬帶不好用loadpull選阻抗點是什么原因,帶內不同頻點load出來的阻抗很發散嗎?

Q:數學公式上阻抗是由實部+虛部組成,虛部的值就是電容和電感隨頻率而產生的阻抗值。所以同一個電容或者電感,但是頻率不一樣,阻抗就不一樣;電路角度來說,就是一個電阻R與電抗Z并聯或者串聯,而Z是隨著頻率變化,所以你看到的阻抗就是隨頻率變化,個人理解。

A:請教個問題,balance PA的架構,對二次諧波的抑制有什么利好嗎

Q:好問題,用時域信號算一下,看看二次諧波的相位是怎么變化的。

A:謝謝,還是不太理解為什么做寬帶的時候,變化的實部R,而頻率部分不變。去嵌以后是去除了頻率部分,而得到一個在實軸上的值。那么這個時候,實部隨什么變化呢?

Q:額,我說的這個變化是你根據你的需要選擇R,比如你想選高效率,或者高功率,或者高功率,這個是根據你的需要做選擇,站在你的角度來說是一個主動變化,你要求它變。

A:哦,這樣理解了,自己去trade off ,去嵌后,排除虛部帶來的隨頻率的阻抗旋轉,其實你就是選定了一個中意的實部了,然后來做匹配。

Q:好解釋。

03

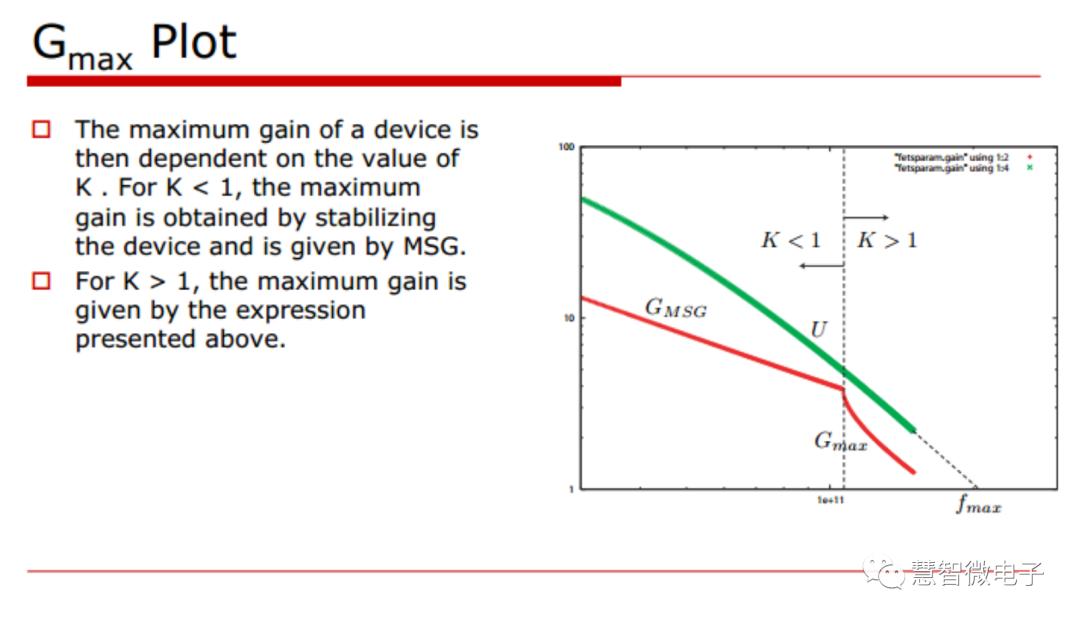

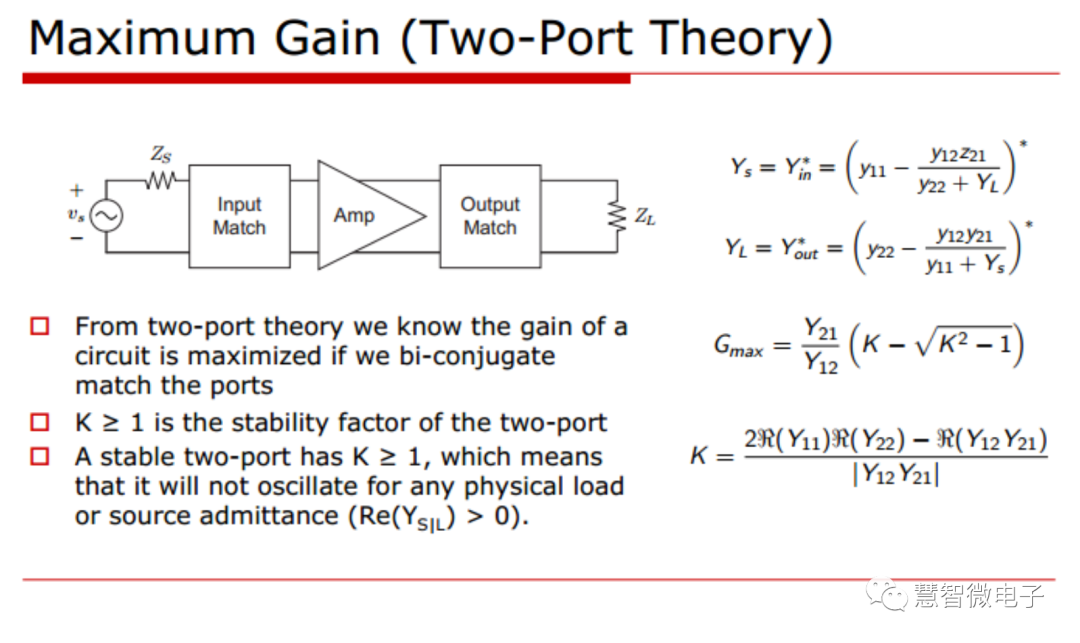

有關Gmax轉折點的討論

Q:請教一個基礎問題,為什么Gmax會有一個拐點?或者誰Gmax的的表達式是什么樣的,好像是文獻及教科書,還是仿真,都是有這么一個拐點,一直不同明白為啥。

A:MAG和gMSG的分界點。

Q:就是說這個曲線是兩條的重疊?

A:可以看一下ISSCC2020-ShortCourse2

Q:豁然開朗,謝謝你。

04

有關TFR電阻加工誤差的討論

Q:關于HBT中?TFR?電阻加工誤差請教一下群里大佬們

1: TFR加工的時候阻值誤差主要來源于長寬厚(濃度)?這幾個因素中的哪一個,還是隨機的?

2:?在一張Wafer上,一顆小的die上,die上面的TFR電阻偏差,是往一個大小方向偏差的,還是有一定的隨機性。

A:?1.寬度和濃度,建議用3um以上寬度TFR,2.中心值上下偏差,不同foundry不太一樣,三安一般+-3ohm內

Q:非常感謝!

05

有關SMA接頭打螺紋膠的討論

Q:請問各位前輩一個工藝問題,有在SMA接頭上打螺紋膠的嗎?有必要打嗎?

A:因為SMA內部是聚四氟乙烯有一定”彈“性或不同材質間的差異性,不像2.92、2.4mm是空氣介質;在需要經常振動的產品上最好在上完力矩后點些中強度或低強度的螺紋膠保險一些。

Q:謝謝。

06

Q:請問ADS里,優化濾波器的時候,用那個算法比較好呀?

A:我一般遺傳再模擬退火

Q:這樣比較快嗎??我都放退火而已??有相關資料可以分享嗎??謝謝群友。

A:沒有比較快,只是習慣了,或是路徑依賴吧。

Q:能否分享一下算法?

A:直接用遺傳算法會不會很慢才收斂,是不是反過來反而會快些。

A:我覺得模擬退火后是全局最優,所以把這個放在后面。

A:應該都有風險落在局部最優,遺傳算法的結果應該不會相對前一個結果惡化。

Q:我試了這個?結果不能跑?其他的算法才可以?請問是什麼原因?

A:里面沒有一種遺傳退火算法么?只聽過這種方法做過波束賦形。

07

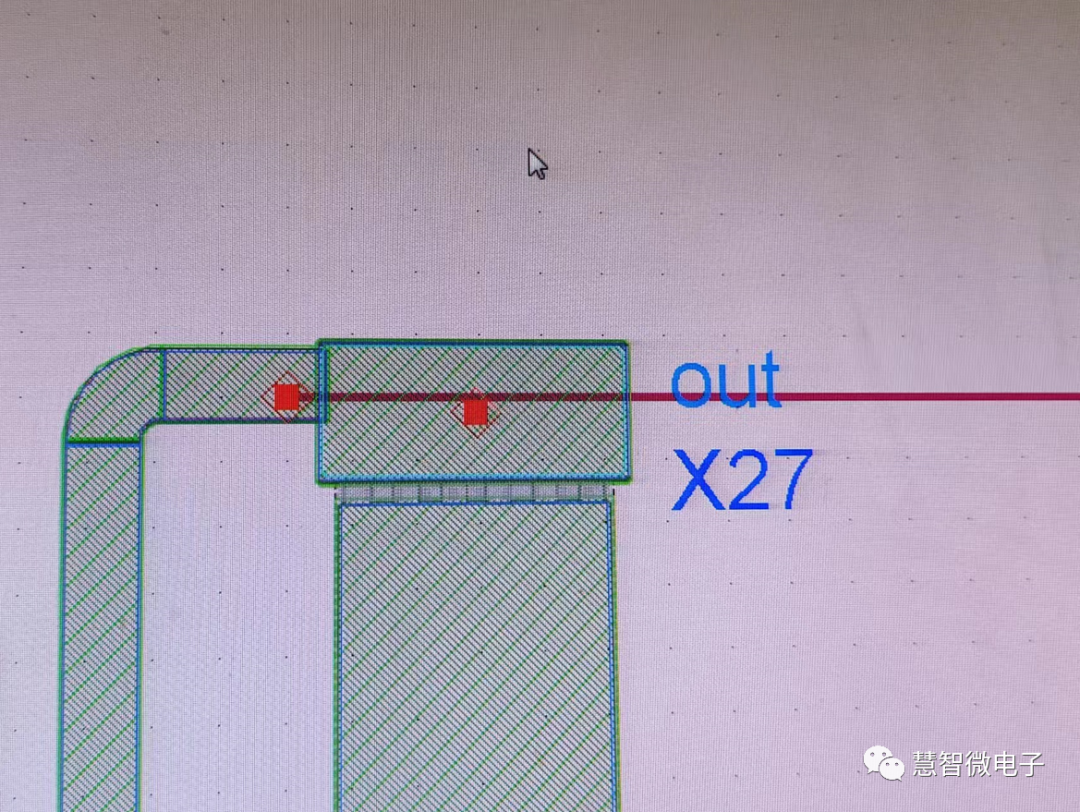

有關ADS仿真中線連接不上連接點的討論

Q:請問有人見過這種wire連不上紅色格點的情況嗎?怎么解決的呢?

A:Ctrl+E.

Q:OK.

08

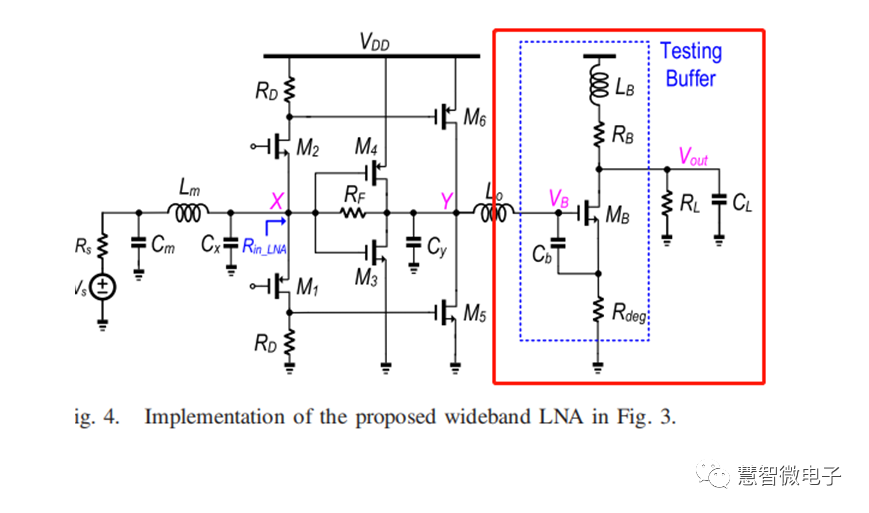

有關電路中增加測試buffer級的討論

Q:請問大家,為啥在好多文章中看到低噪放的末端需要加一個testing?buffer

A:方便測試啊,又不影響性能。到時候直接去嵌。

Q:話說怎么方便測試啊?

A:不然核心電路還要去搞輸出匹配啊。有了test buffer以后就不用做了。測完再把這個buffer剪掉就是你電路的性能了。這不是很方便嘛。

09

有關噪聲貢獻仿真的討論

Q:請問大家,cadence或者ads可以仿真電路某個部分的噪聲貢獻嗎?

A:cadence的noise summary可以看到噪聲貢獻。

Q:恩恩,這個之前有查到過,但是不知道在ADS里咋仿因為管子都鏈接到ADS里了。

ads不知是否有類似仿真噪聲貢獻的設置?

A:可以,你在ADS help去搜Noise,就很多類型的。

Q:ADS?感謝老師!

10

有關射頻放大器中饋電電感的設計

Q:大家在設計LNA、PA的時候,饋電電感的取值是如何讓選取的?是不是越大越好?一般PDK中的電感設計不了太大。大家的biasing network都是咋設計的,可以交流交流

A:滿足你應用頻段的RFchoke就行了吧,面積越小越nice

Q:一般RFC的在工作頻段的阻抗要求多大呢?我看有的書上寫的是10*Zo,至少500歐姆,這個高阻的RFC一般的PDK中實現不了,電感值一般會偏小,電抗較低。

A:是的,所以很多單片放大器很多要求片外加額外的rfc電感。

Q:所以在設計中,如果要把偏置電路集成到MMIC中需要犧牲一部分性能為代價?

A:我覺得這要看拿什么對比了,你做自適應偏置電路,是對你電路的pvt性能產生優化作用的,你拿理想器件看可能感覺犧牲了性能。

Q:自適應偏置一般是用在柵極的吧,漏極的偏置一般使用RFC的吧?

A:是的,習慣上說偏置一般是指柵極的偏置電壓

Q:好的,多謝。

11

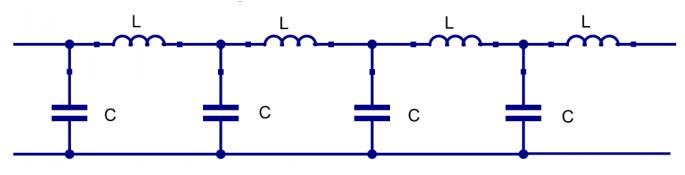

有關饋電電感的再次討論

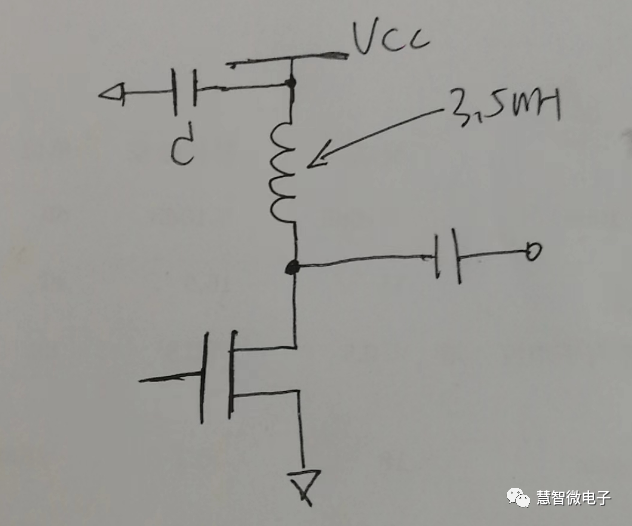

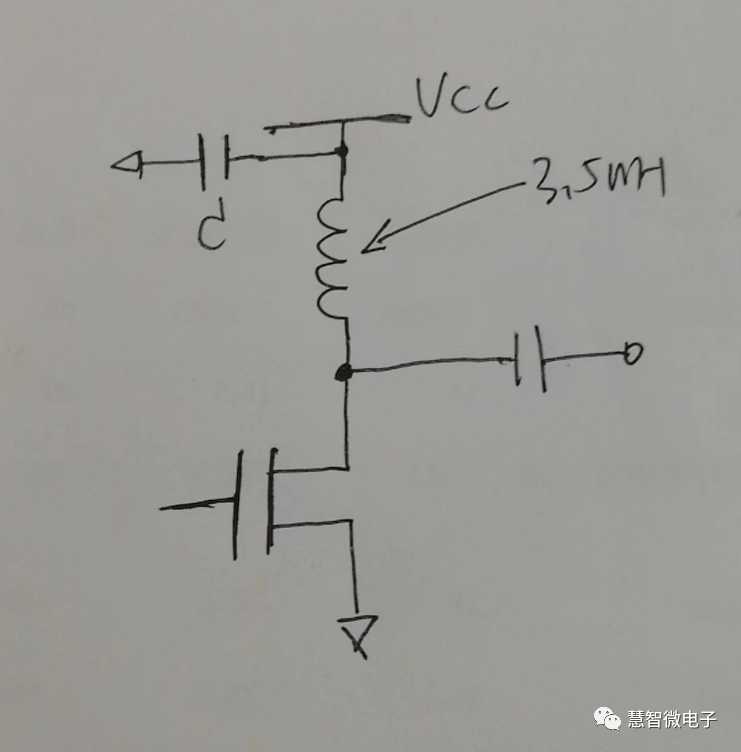

Q:有人說這個3.5nH的電感是負載電感,不是饋電電感,如何解釋?這個電感和哪個電容諧振呢?實際的負載阻抗是LC諧振阻抗值,不是電感的值。有勞各位,給解釋一下,我被這個搞蒙了

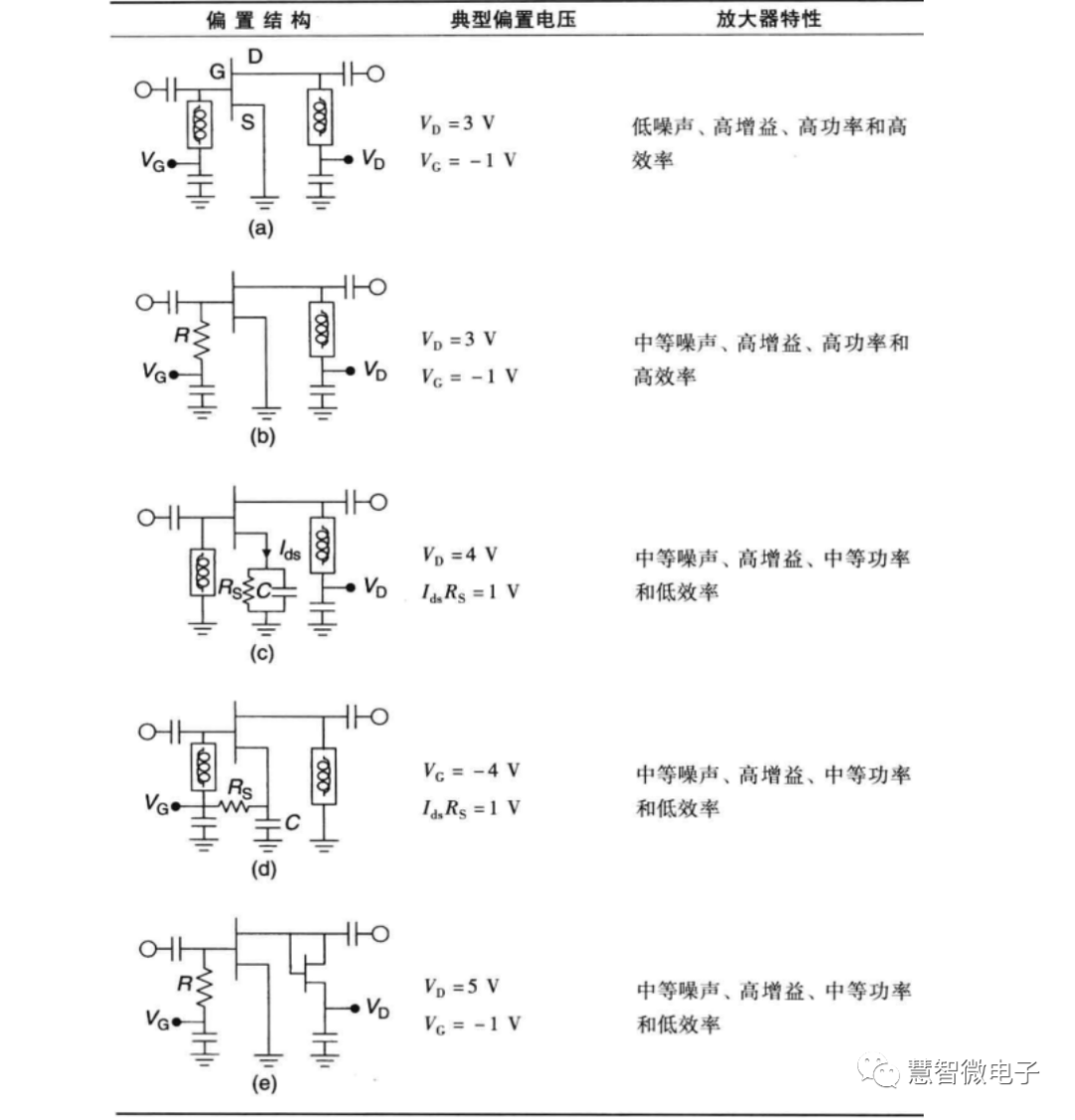

《射頻與微波晶體管放大器基礎》書本上是這樣的

A:一般這種兩種作用都有的吧,參與匹配和choke。

Q:但是實際上,在低頻段,如果把饋電電感集成在MMIC內部,一般PDK都不會有太大的取值,或多或少都有RF信號的泄露。

但是我看有一個例子。2.4GHz,漏極饋電電感取值3.5nH,有老師說這是參與諧振的LC電路,屬于負載電感。但是不知道和哪個電容C諧振

A:嘗試回復一下:choke電感的作用是通直隔交(不會讓交流信號耦合到電源),理想情況下需要足夠大才能達到效果(ads里model的10uH左右?)

但是因為我們現在都會存在bypass或decouple電容作為射頻地,所以對choke電感的要求降低了,使其可以使用較小的值同時可以提供匹配的效果(uH級別并聯電感在smith圓圖上是基本不動的)

說到諧振網絡:要看你是想要帶通效果還是低通效果,帶通可以在choke上并電筒,低通可以輸出串電容(該電容還有隔直的效果)

A:我覺得不可能完全隔絕射頻信號泄漏進偏置電路的,或多或少都有

Q:就是這個電路,2.4GHz,取值3.5nH,如果計算電抗只有53Ω,有個老師說是諧振電路,但是不知道和哪個電容諧振。說這個電感是負載電感

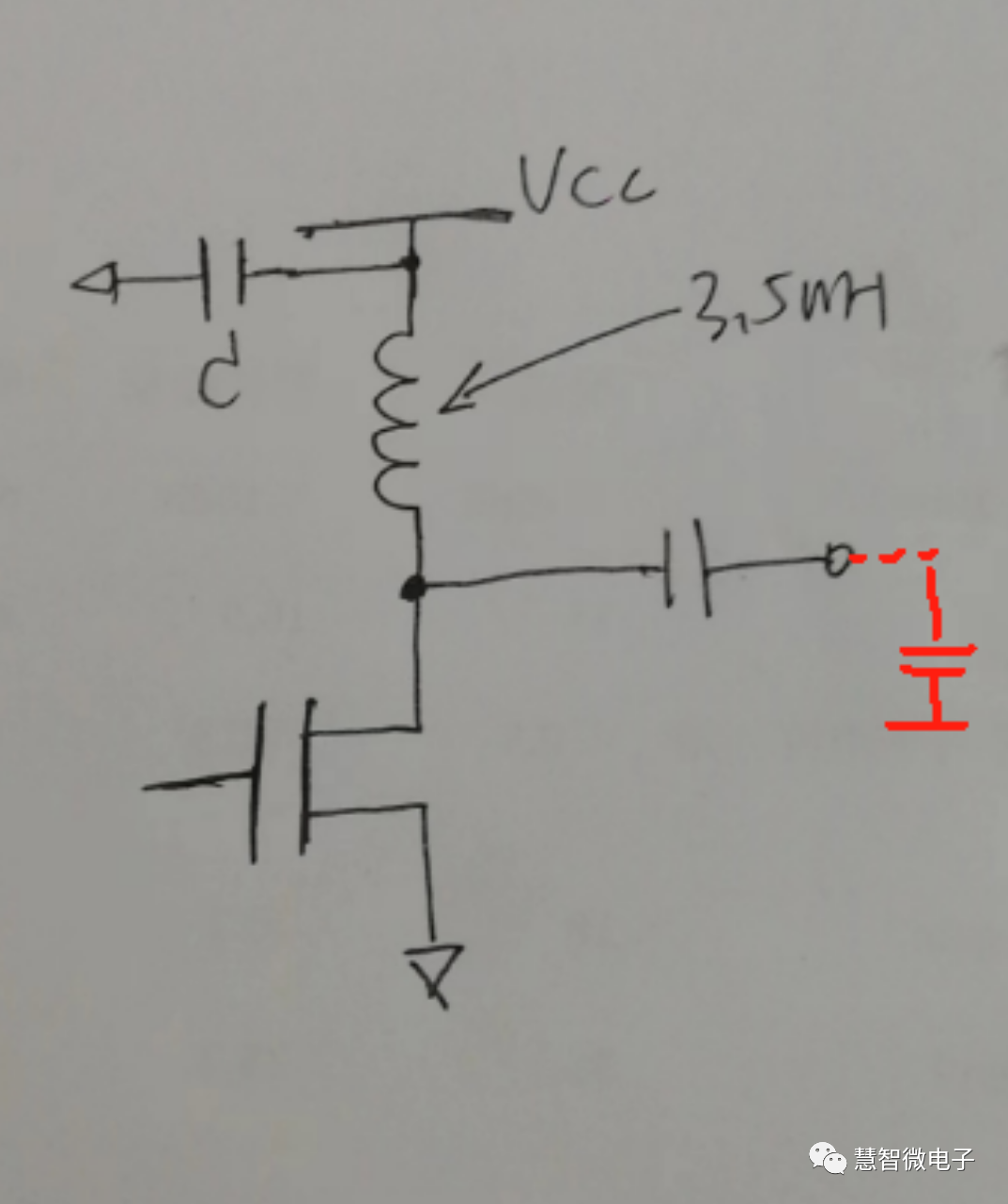

A:這個要具體分析,理想情況是輸出串的電容和這個3.5nH,非理想情況會有段走線到Vcc,這個時候bypass的C會和3.5nH諧振(因為不是理想地了)。就是有兩個諧振點。

A:會不會是和漏端的所有等效電容。

A:實際上面那個C和VDD相連,是隔絕從VDD帶來高頻干擾的吧

Q:C是bypass電容。

A:只有一種可能存在諧振,后面你有負載電容,不然的話就是一個dc饋電

Q:后面直接接50歐姆負載了,是不是MMIC直接饋電的話,都是利用諧振原理設計的,PDK中沒有那么大的RFC,在低頻中,如L/S,高頻就可以用微帶線了。

A:會不會是跟cds 諧震呢?是有人用並聯電感去消除cds 影響。

Q:應該不單單是Cds,Cds沒有那么大。

A:“是不是MMIC直接饋電的話,都是利用諧振原理設計的,PDK中沒有那么大的RFC”??一般用tank搞個幾百歐的Rp就夠了。

12

有關放大器退化電感的討論

Q:大家好,請教一個問題,電路里的高頻增益與源退化電感有很大關系,調整的過程中發現源退化電感越小,增益越大,但現在這個電感已經比較小了,請問各位大神有無好的辦法?

A:源退化電感是為了噪聲么,如果不能直接去掉,考慮使用其他類型的放大器?

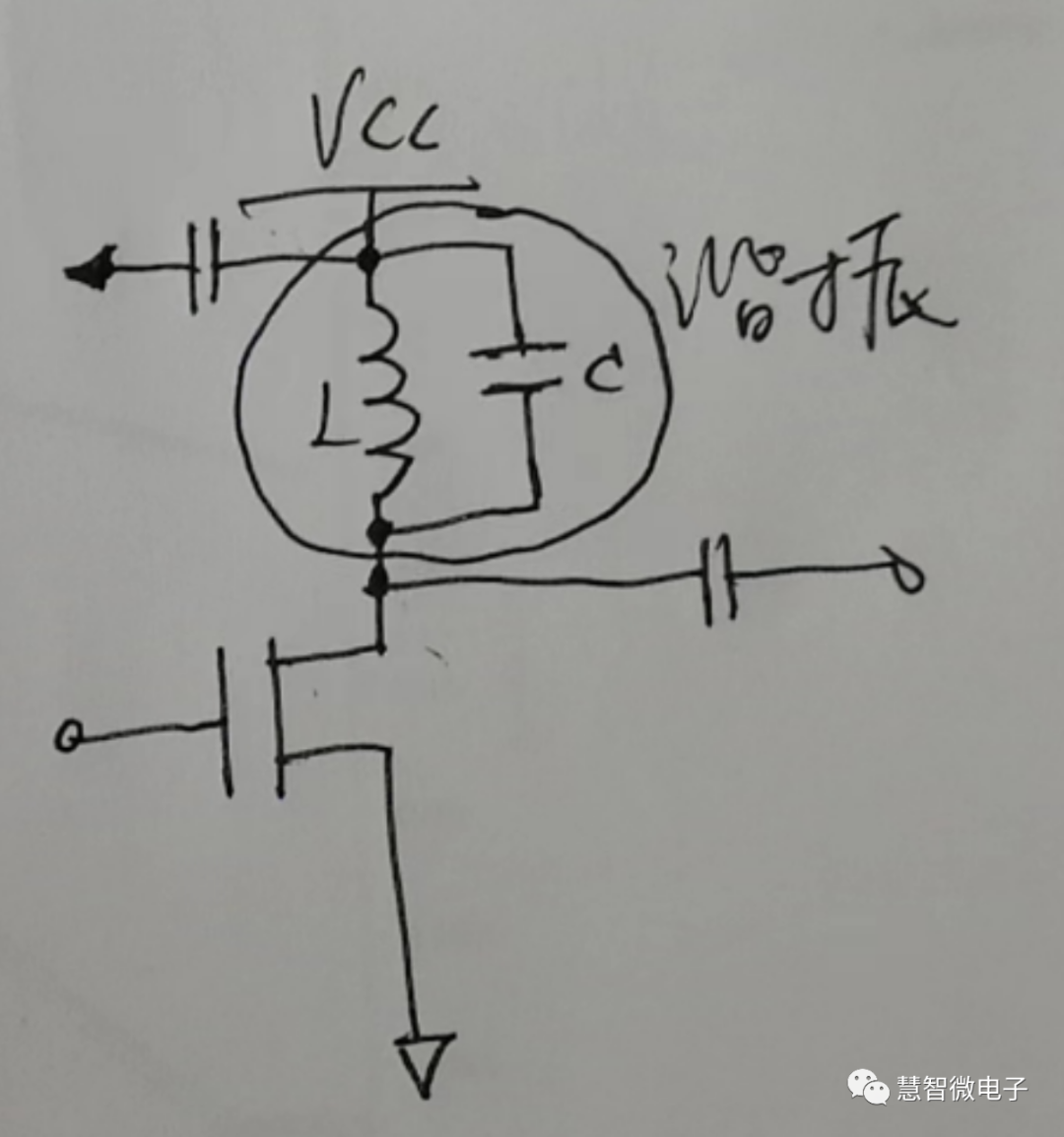

Q:這種?

A:是的,現在用的大都是這樣的。

Q:謝謝大家。

13

有關Doherty的非對稱設計

Q:如果Doherty中輔助功放電流是主功放的三四倍了,回退功率點大于6dB了,有什么壞處嗎?

A:這不就是非對稱的doherty嗎?很正常吧,因為現在的調制信號也不止6dB了,8或者9的papr都有,就需要1比2或者1比1.5了

Q:我看到輔助功放電流大一些線性度會更好,但如果太大會有缺點,不知道是什么缺點。

A:符合你設計的要求就好,因為peak大部分時間也不會接近飽和。

Q:謝謝。

14

有關LNA穩定性設計的討論

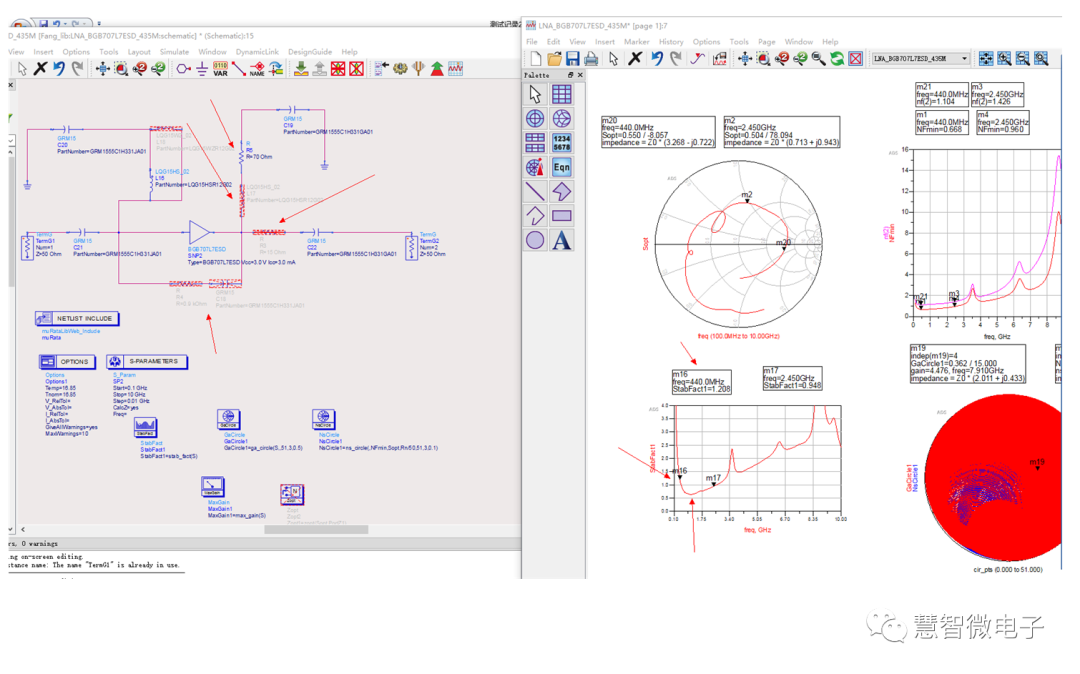

Q:請教一下LNA提高穩定性的方法,如果不用負反饋,要通過偏置和輸出串聯電阻來調整的話,怎樣才能把圖片中最低點調到大于1,而且工作頻率433M的K值又不要太大了,1.1左右。現在就是如果全頻段大于1,工作頻率433M又太大了。

A:加個濾波器,把gain卡在范圍內。

Q:這樣啊,濾波器不是外圍的嗎,會影響LNA的K值?

A:如圖:

A:?濾波器如果是無窮Q 的,?不會改變K。?如果改變是因為gain 降低了,?其實和反饋或是其他減低增益的方法沒有本質區別。

Q:降S21來提高穩定性??那我還是乖乖用負反饋吧,本來想用偏置和輸出電阻來提高K值的,結果K值工作頻率太不平坦了。

A:如果不想降低增益,?提高K 值。?里面的電路設計需要修改,?主要是看到反饋dB(|S12|)?是不是夠大?> 30dB。?如果夠大,但是K 還是有風險,檢查一下電路中有沒有類似 oscillator 的架構,找到的話,把它毀掉。一般的de-bug 就這思路。

Q:試了一下負反饋,K值是好平坦,但是NFmin由0.6變成了1.0了。

Q:負反饋就是回引入噪聲,想問一下,k值平坦度有什么影響嗎?

Q:不是大于1就可以了?

Q:想問一下,穩定性因子需要在全頻段大于1嗎,只在工作頻段大于1可以嗎

A:全頻段都需要。其他干擾信號不一定在工作頻段內。

k和增益相互制約,要做高效率肯定要限制k不能太高,在1附近能出管子最大性能。

Q:我用的英飛凌這個芯片都是設計全頻道大于1,只工作頻段會不會有風險?

A:K>1 不是干擾的擔憂,?主要是帶外阻抗的擔憂。

Q:帶外阻抗是指的是??

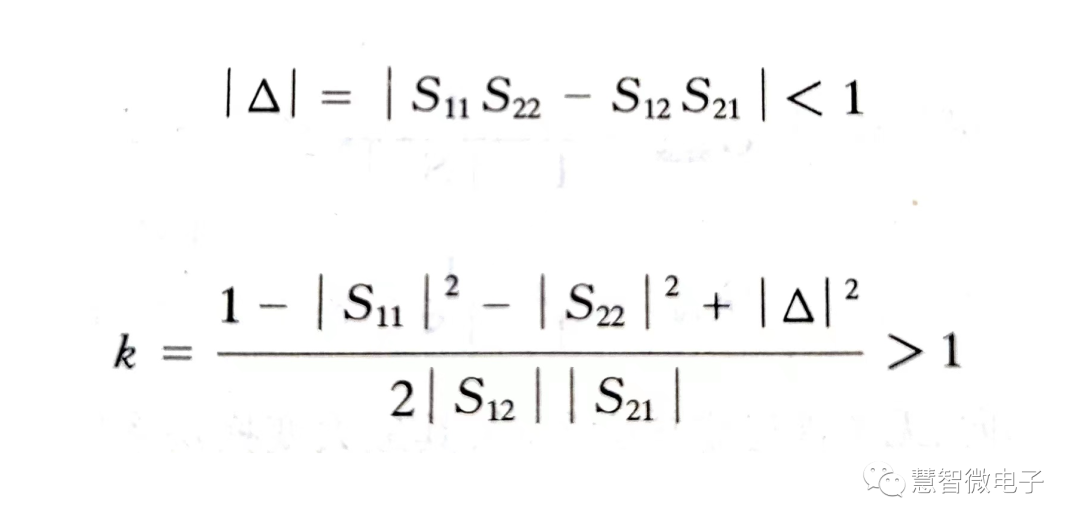

A:人們引入K 的概念是想解決無條件穩定的問題,無條件是指 我們不知道input 或是 output 的阻抗是啥,所以就說那就是整個smitch chart 的任何一點吧。

Q:不都是看Mu值嗎?

A:是的,mu 更好,?歷史上也是現有K+delta, 后來才有的mu 。K 值?>1, 只是告訴我們?無條件穩定,但是 k=2 和 K=3 比,我們不能說K 越大?這個電路就穩定。而mu值確實可以這么下結論。

濾波器無論是放在前面還是后面,?只能保證?帶內50ohm,帶外是啥阻抗,沒有人控制的了,一般在smith 圓外側。但是還是不能改變K ,因為它自己的計算就是整個smith 圓。

Q:“人們引入K?的概念是想解決無條件穩定的問題,無條件是指?我們不知道input??或是?output?的阻抗是啥”??這個是啥意思,那如果LNA在板子上,前后都有固定物料,那是不是就帶內K大于1就行了。

A:他的意思是不管接什么阻抗都是穩定的,K才全頻段大于1,其實很難知道,所以K>1 是現在的標配。

Q:有一個問題,就是穩定性看的一般都是小信號,如果設計的是class c的pa,看小信號的話會不會沒有意義,因為管子都沒開啟。是不是還要看大信號仿真。

A:直接用ab類的穩定網絡。

Q:你好,穩定系數看全頻段,是指帶寬內的所有頻率,還是說我0-100G這種所有頻率?

A:0-100這種

Q:看你們之前的聊天,說還要看mu,我沒看過這個,就大概看下K,有啥影響嗎?

A:兩個都看。

Q:學到了,謝謝幾位的解答。

15

有關諧振腔帶外凹點的討論

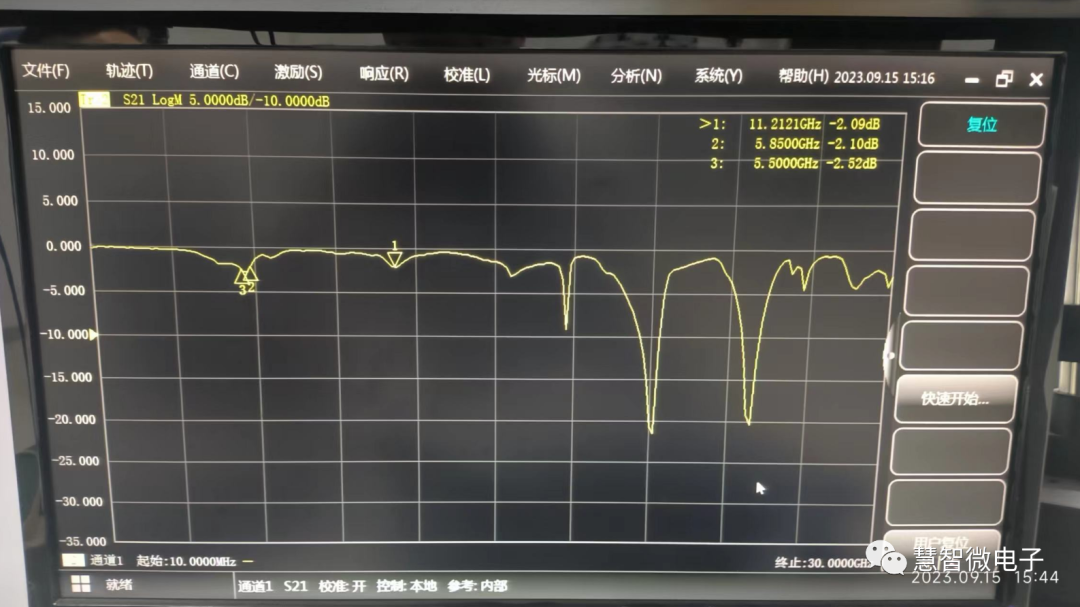

Q:在測量諧振腔的S21參數時,為什么在第一個諧振坑11GHZ前還有一個坑,有哪位大佬知道嗎?

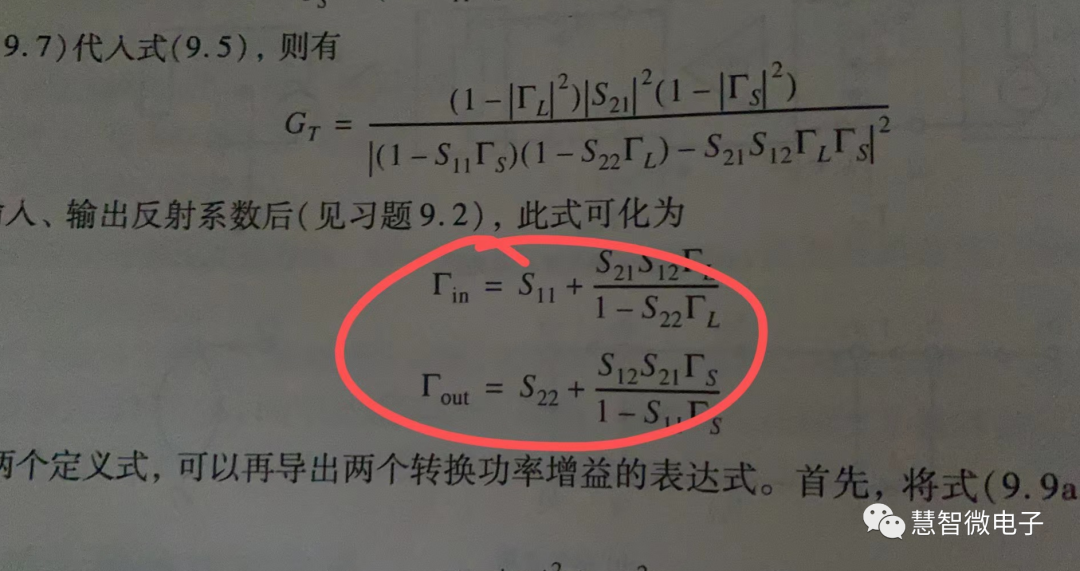

Q:網絡的S參數是固定不變的嗎,還是隨源和負載的不同而變化呀?有哪位好心人解答一下嗎?ADS中仿真出來的S11是理論的S11,還是輸入端反射系數呀?

A:應該是反射系數,會隨源和負載變化的。

A:S參數是會和負載源的不同變化的

Q:我的理解是只要這個網絡做好了,他的S參數就固定不變了,因為S參數是在匹配情況下的值,應該是唯一的。但是為什么仿真的時候會隨著變化呢?

A:有截圖嗎?是怎么個變化?按道理,只要你的網絡做好了,負載,源這些都沒變,S參數是不會變的。

Q:現在手里沒圖

Q:反射系數和s參數不是一回事吧,

A:只要你的隔離度做的好,輸入端的反射系數就大概等于S11。

Q:哦哦,謝謝各位了

A:嗯,反射系數和S參數相互之間可以換算的,是與源或者負載阻抗相關的。

A:s參數是某個電路在特定條件下(源端/負載匹配)的特性;反射系數是此電路在實際情況下(源端/負載不一定匹配)的特性。

A:是的 我們常認為測試的s參數 是在負載端匹配下,也就是gamma L 等于0。

Q:那么仿真軟件測出來的s11/s22就是輸入/輸出端口實際的反射系數,并不是網絡本身的s參數特性?我看過一篇帖子說s21測出來的是電路的實際增益,maxgain才是網絡的S21

A:仿真某電路的時候也是要50Ω負載的,這個實際增益也是在仿真條件下的增益,實際上源/負載阻抗有變化,這個增益就會和仿真有變化。

Q:好,謝謝老師。

16

有關LNA設計中RC并聯電路作用的討論

Q:有個問題想請教大家 LNA版圖上經常在源到地那里掛RC并聯電路主要是為了什么?跟直接電感或者電阻地有啥區別?

A:電阻R起到負反饋作用來穩定直流工作點 電容C的話在高頻時旁路信號 從而不起到負反饋作用 就不會降低增益 感覺有這方面因素哈。

Q:感謝各位解答。

17

有關PA大信號穩定性的討論

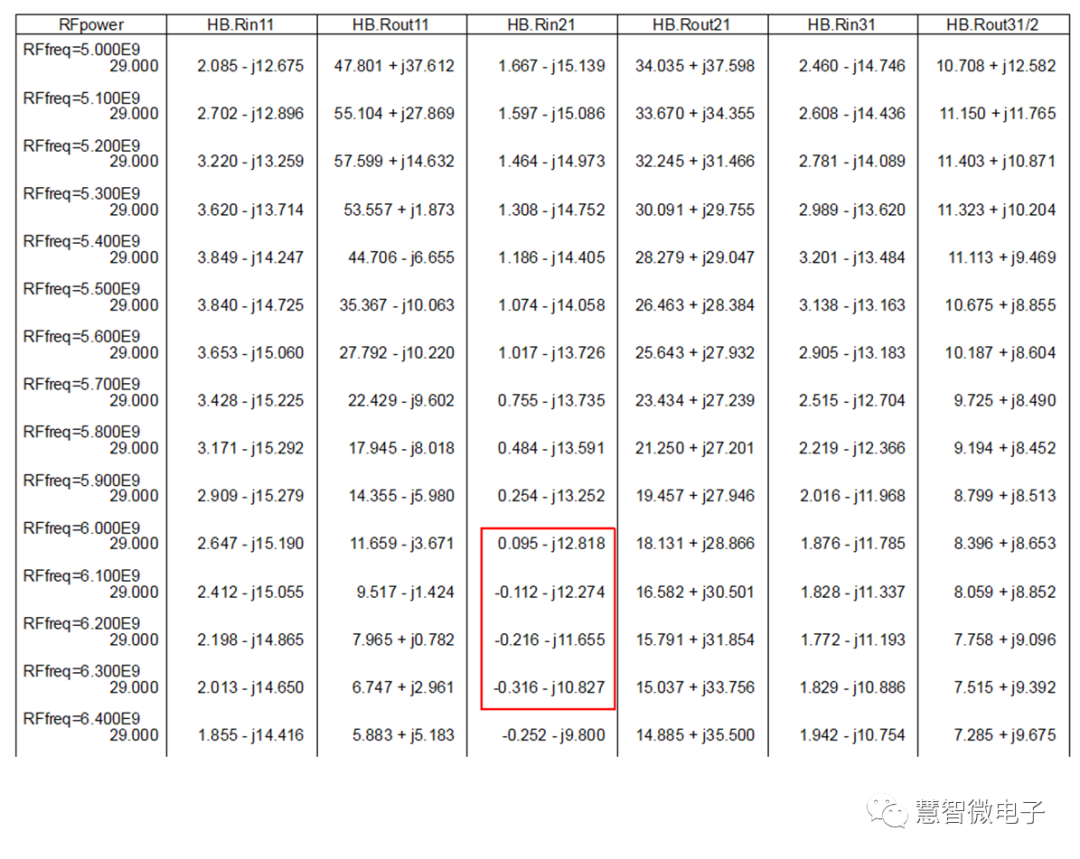

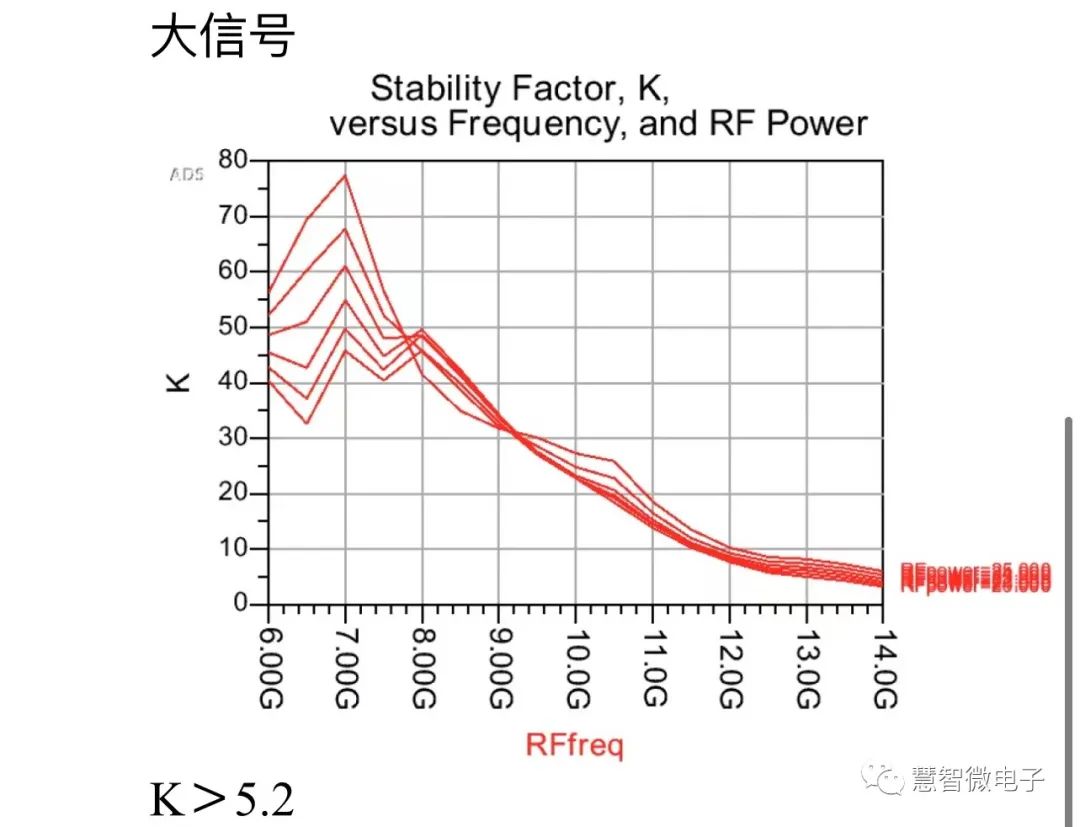

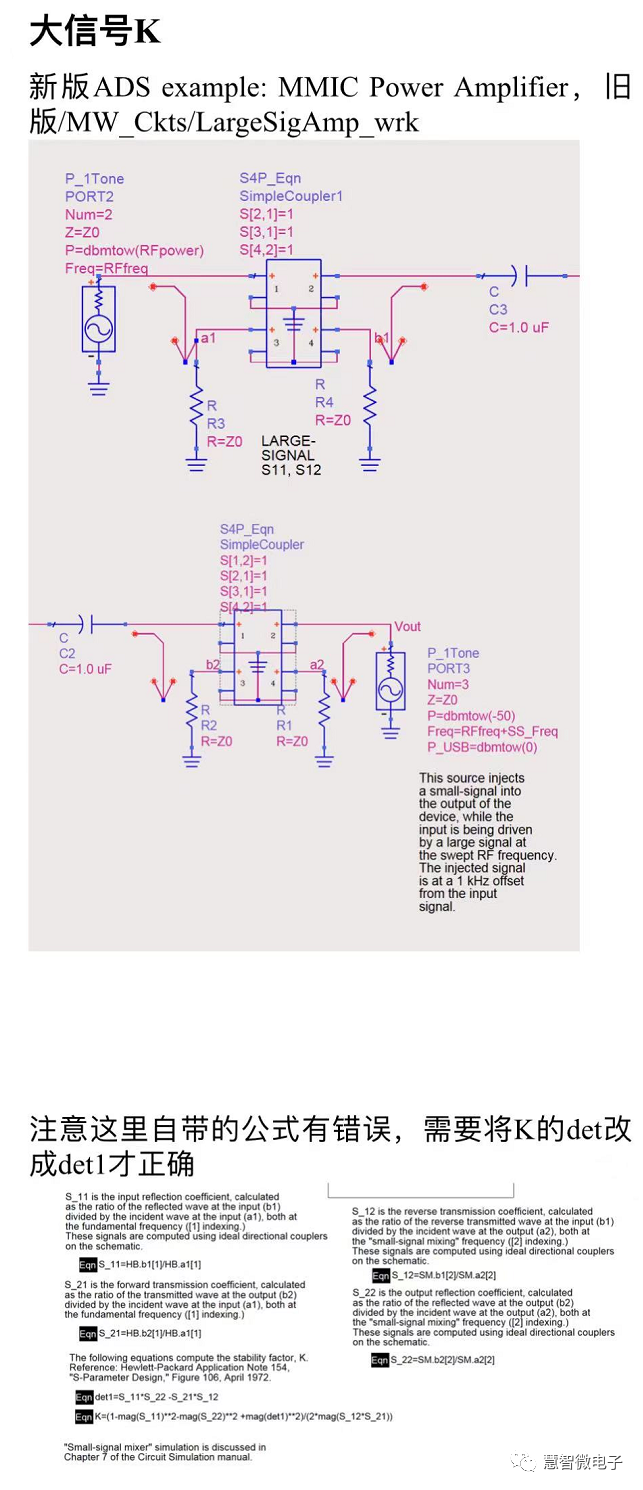

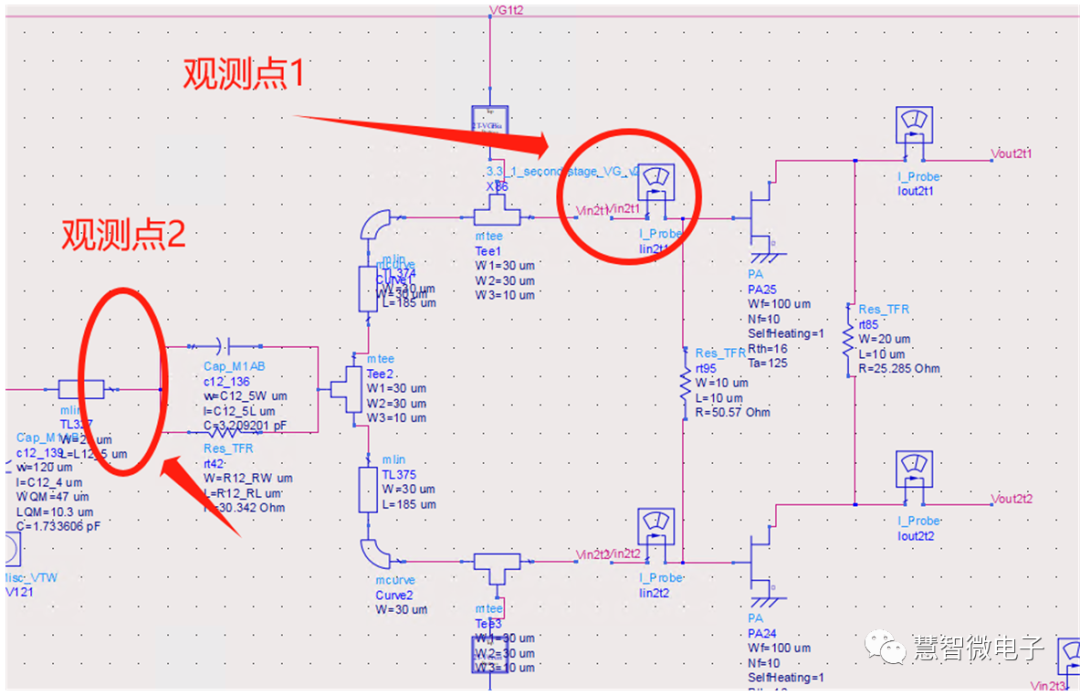

Q:大家好!有個關于PA放大器的設計當中,關于穩定性的考量,大家通過什么去進行設計的。通常來說一個是小信號的K,u值;那在大信號仿真上面呢?

我們在整版原理圖的大信號仿真上,在單管的輸入輸出添加電壓表和電流表,通過公式Rout=Vin[1]/Iin.i[1]來看管子輸入輸出的阻抗,觀察大信號阻抗來判斷其穩定性以及阻抗匹配等。發現在管子的輸入端,在某些頻點會出現負阻的情況。

一個是,不知道這種看大信號阻抗的方式是否能用來判斷功放的穩定性。另外一個就是,大信號的穩定性,大家是通過什么方式去進行考量、驗證的?

A:可以通過瞬態看,看看bias上有沒有非理想的波形。

A:最近設計的pa流片回來也發現白激嚴重,仿真的時候u在所有頻段是大于1的。最后實測發現是流片的電容整體偏小,導致Vcc的并聯耦合電容偏小從而導致自激。

A:有大信號穩定性的模版,找一個大信號仿真的模版?然后看這個大K值。

自激目前來說,還要看下級間穩定性,用WSprobe或者這個SProbePairT模版,我做了兩個PA都沒震蕩,看這個是沒問題的,也和別人詢問過經驗,也是用這種方法。

Q:那個我們敲公式看的那個負阻?其實參考意義不大的是嘛?

A:也有這種說法,不過這個模版公式里好像就是用這個看的。

Q:好的?我們去check一下。

A:以我觀察,pa尤其是基站pa還是基于測量的技術,例如loadpull確定最佳阻抗的方法,包括穩定性,最終還是通過實測來定論的,因為管子的模型還不夠準確完備,各種脈沖信號調制信號的響應并不完全正確。設計時,穩定性還是以小信號參考為主。比如k值留有余量,駐波小于0,帶外無高增益,無阻抗突變等等。小信號沒問題,我感覺能保證90%的pa是穩定的。但是還是有10%的pa在特定場景下,比如低溫,雙音脈沖或者其他特別的信號條件下,蹦出一些雜散信號出來,需要具體問題具體分析的。仿真時,尤其是die輸入負阻,阻抗在smith圓圖外是不被允許的,意味著駐波大于0,不穩定。一定要通過串電阻或者有耗匹配把阻抗都轉到圓內。大信號的穩定性可能可以看看阻抗和曲線amam,ampm是否有突變等等。穩定性我理解主要還是參考小信號。

A:小小補充下,就算廠家能準確測出大信號模型,但實際運用條件和環境變化都會導致管子大信號阻抗和大信號模型有較大差別PA還得是一門優化調試的手藝活

Q:這里我有個疑問就是?我比如我已經采用有耗匹配的方式去進行阻抗的一個轉移。

采用有耗匹配對單管的阻抗進行改善,那我后續采用的觀測點是用1還是2?這里關于觀測點的選擇,也可能是造成我們困擾的一個原因之一。

A:一般來說就加在管子前后,如果不是用WSprobe這種,還得把穩定網絡加上。

Q:感謝各位老師!

18

有關Doherty功放設計的討論

Q:大家好!向大家請教一下關于Doherty 功放中Peak路單管調試方法的相關問題。目前,peak功放輸入和輸出匹配網絡的微帶線已經確定,用電容調試功放的性能。目前用矢網調輸入匹配網絡S11<-10dB,然后調輸出匹配網絡,脈沖信號下調Psat。請問:1.調小信號S11的目的是什么?這個與Peak路開啟點有關系嗎?2.當輸出匹配網絡調不動了,目標的Psat沒有達到。下一步是不是需要在脈沖信號的情況下調輸入匹配網絡?然后相互迭代?還是修改Peak的匹配網絡,直到滿足Psat為止。3.peak路的效率應該怎么考慮?滿足什么要求?

A:個人理解僅供參考,有問題歡迎大佬糾錯

1.我理解只是調輸入駐波,跟開啟點沒關系;2.輸出調不動就調輸入,找到合適狀態返回調輸出,進行迭代;3.peak開啟是為了要飽和,一般按設計peak要出到接近最大功率的,這個狀態可以不考慮效率

Q:我理解功放管大信號和小信號的輸入和輸出最優阻抗點不一樣。最初調輸入S11是為了什么?

A:你們小信號駐波要求多少,對于功放-10應該已經很好了,按說是不太差就行。

調完輸出匹配網絡之后再去看小信號S11,S11發生了變化,要求我不清楚,調S11<-10之后,直接脈沖調輸出,調Psat。

A:peak路要調整小信號下的s22,需要單獨接出來看,通過調整offset line保證接近開路點,psat出不了可能的相位合得不好。

Q:目前只調peak功放單管。在AB類的偏執下,調它的Psat。調輸出匹配網絡的電容,找它的Psat。

A:peak路調s11為了啥? peak.路不是c類嗎?

Q:?AB類的peak和C類的peak在小信號的大概增益差多少?psat大概差多少?

A:c類小信號沒增益,功率看你DPA的是不是對稱的??對稱一樣??非對稱??根據回退量可以計算出來。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論