88e6060簡介

Marvell?88 e6060單個芯片上集成一個完整的6-port快速以太網交換機支持一個CPU連接。它包含五10 base - t / 100 base-tx收發器(物理),兩個可以用來支持100 base-fx;六個獨立的快速以太網介質訪問控制(mac)、高速非阻塞開關結構,高性能地址查找引擎和1/2 m幀緩沖mem-ory。它是專為廠商低端口計數開關系統和防火墻的路由器。

PHY收發器的設計和Marvell Vir-tual電纜測試儀?(VCT?)技術先進的電纜診斷。VCT使IT經理可以很容易確定布線問題到一米的位置,減少網絡安裝和支持成本。

Marvell 88E6060被設計成在所有環境下工作,在PHYs的自動跨界、自動極性和自動談判中支持真插即用,以及橋環路的預防(使用跨越樹支持的端口狀態)。基于共享的基于內存的交換結構采用了最晚的Marvell switch架構,在所有的交通環境中提供非阻塞的切換性能。

第6個端口,是RMII / MII / MII / MII / SNI接口的接口,可以直接連接到管理或路由器cpu,它可以在RMII模式,MII - phy,MII - mac模式或者是MII - mac模式,或者是MII - mac模式,或者是MII - mac模式,這些接口和BPDU的操作,可以編程的每個端口VLAN配置,和端口狀態,支持生成樹,真正隔離的WAN和局域網的防火墻應用程序。

在Marvell 88E6060中,使用Marvell先進的混合信號處理技術,實現了自適應均衡和時鐘數據恢復的數字實現,采用了特殊的電源管理技術,實現了低功耗和高端口計數的集成,在Marvell 88E6060中,PHY和MAC單元都充分利用了IEEE 802.3、IEEE 802.3 u和IEEE 802. 3x標準的相關部分。

Marvell 88E6060的許多操作模式可以使用SMI(串行管理接口- MDC/ MDIO)和/或低成本串行EEPROM(93C46,C56或C66)配置。

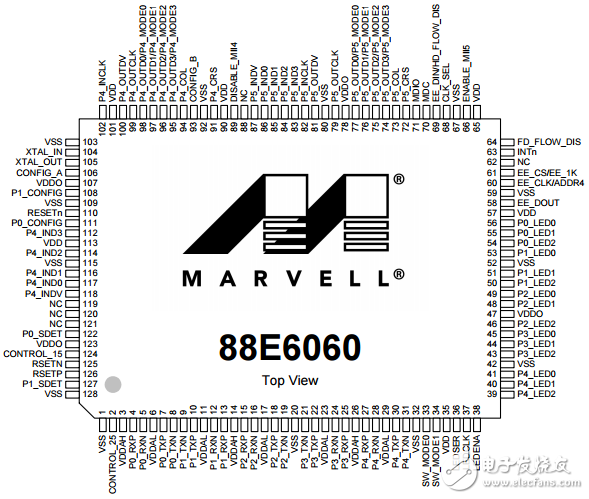

88e6060引腳圖

88e6060引腳說明

P[4:0]_RXP:通常輸入,在交叉模式是輸出。

接受輸入的正極,

P[4:0]_RXN:通常輸入,在交叉模式是輸出。

接受輸入的負極,

P[4:0]_TXP:通常輸出,在交叉模式是輸入。

接受輸入的正極,

P[4:0]_TXN:通常輸出,在交叉模式是輸入。

接受輸入的負極,

P[1::0]_SDET:輸入

信號檢測輸入,如果端口0和/或1被配置為100BASE-FX模式,SDET表示光纖收發器的信號是否被檢測到,正電平表示的信號被檢測到。

如果配置端口0和/或1個10/100BASE-T模式,SDET沒有被使用,但不能懸空,因為這些引腳不包含內部電阻器,必須連接到VSS或VDD直接通過一個4.7K的電阻

P[1:0]_CONFIG:輸入

端口0和1的配置。CONFIG引腳用于設置端口0和1的默認配置,這些引腳連接到其他設備引腳如下:

VSS =啟用自動協商功能 - 默認

P0_LED1=強制10BASE-T半雙工

P0_LED2=強制10BASE-T 全雙工

P1_LED0=強制100BASE-TX半雙工

P1_LED1=強制100BASE-TX全雙工

P1_LED2=強制100BASE-FX半雙工

VDDO=強制100BASE-FX全雙工

端口2,3和4的默認配置是自動協商功能。

CONFIG引腳復位后配置,包含內部下拉電阻,使他們可以懸空來選擇自動協商。

CONFIG_A: 輸入 懸空的話內部上拉電阻設置為模式3

全局配置引腳:全局配置用于設置默認的LED模式和遠端故障指示(FEFI)在100BASE-FX模式下,這些引腳連接到其他設備引腳如下:

VSS= LED模式0,FEFI禁用

P0_LED0= LED模式0,FEFI

P0_LED1= LED模式1,FEFI禁用

P0_LED2= LED模式1,FEFI

P1_LED0= LED模式2,FEFI禁用

P1_LED1= LED模式2,FEFI

P1_LED2= LED模式3,FEFI禁用

VDDO= LED模式3, 默認FEFI啟用

CONFIG_A引腳配置復位后,包含內部上拉電阻。

CONFIG_B: 輸入

全局配置B,全局配置引腳用于設置的默認自動交叉模式為; VDDO=自動交叉,B類驅動,默認啟用能量檢測

復位后被配置,內部有一個上拉電阻。

穩壓器和參考:

RSETP,RSETN:參考電阻。2kΩ(1%)的電阻器被放置之間的RSETP和RSETN。此電阻器是用來設置一個內部偏置基準電流。

CONTROL_15:

外部1.5V穩壓器的電壓控制。這一信號控制外部PNP晶體管,以產生1.5V電源為的VDD和VDDAL的引腳。 CONTROL_25:

外部的2.5V穩壓器的電壓控制。這個信號產生2.5V電源為VDDAH引腳控制一個外部PNP晶體管。

系統:

XTAL_IN:輸入 25M晶振

25M或者50M系統參考時鐘輸入;這個時鐘輸入頻率由CLK_SEL選定。

時鐘源可以來自晶體的頻率(25 MHz)或振蕩發生器(25或50 MHz)。這是唯一的需要,因為它是用于在交換機和PHY的時鐘。

XTAL_OUT:輸出 25M晶振

系統基準時鐘輸出。此輸出只能被用來驅動一個外部晶體的頻率(25 MHz)。它不能被用于驅動外部邏輯。如果振蕩器連接到XTAL_IN該引腳應懸空。

CLK_SEL:輸出 接VSS

時鐘頻率選擇,該引腳連接到VSS如果XTAL_IN為25 MHz。如果XTAL_IN為50 MHz該引腳連接到VDDO或將其懸空。該引腳必須是穩定的在復位之后。

CLK_SEL是通過一個內部電阻拉高。

RESETn:輸入 復位低電平有效

硬件復位。低電平有效。復位時配置的88E6060;

當RESETN為低時,所有的引腳被配置輸入和這些引腳上的值在RESETN上升沿或一段時間后的被鎖存。

寄存器訪問接口:

MDC:管理數據的參考時鐘為串行管理接口(SMI)。

預計不會是一個連續的時鐘流,支持的最高頻率為8.3兆赫。

SMI是用于訪問物理層(PHY)和在交換機中的寄存器假如串行EEPROM不能訪問寄存器。它可以在所有組合中的SW_MODE[1:0]。

MDC是通過一個內部上拉電阻拉高。

MDIO:輸入;

為SMI管理數據輸入/輸出的。

MDIO是用來傳輸的管理數據輸入和輸出與MDC同步;

該引腳需要一個外部上拉電阻,范圍在4.7kΩ到10kΩ的范圍內。

88E6060設備使用16的32種可能的SMI端口地址。

這個16使用可以選擇EE_CLK/ADDR4引腳。

MDIO是通過一個內部上拉電阻拉高。

INTn:開漏極輸出;

INTn是一個低電平有效,漏極開路輸出引腳, 表示非屏蔽中斷事件發生。

當這個信號是無效的,需要一個外部上拉電阻,實現了邏輯高電平。

串行EEPROM接口:

EE_CS/EE_1K:I/O 口, 串行EEPROM芯片選擇

EE_CS是通過一個內部上拉電阻拉高。使用一個4.7kΩ電阻到VSS的配置低

EE_CLK/ADDR4 :I/O, 串行EEPROM時鐘

EE_CLK是通過一個內部上拉電阻拉高。使用一個4.7kΩ電阻到VSS的配置低。

EE_DIN/HD_FLOW_DIS:通常是輸入,

EE_DIN是一個多功能引腳,在硬件復位時用于配置88E6060。當芯片復位時引腳狀態被確定,芯片復位時EE_DIN成為輸入和配置禁用半雙工的流量控制,它的值被鎖存于復位的上升沿;

低=使能所有半雙工端口的流量控制

高=禁止所有半雙工端口的流量控制

EE_DIN是通過一個內部電阻拉高。使用一個4.7kΩ電阻到VSS的配置低。

HD_FLOW_DIS用于選擇全雙工端口的流量控制

EE_DOUT:輸入

串行EEPROM數據從EEPROM器件。

EE_DOUT是串行EEPROM的數據,參考EE_CLK用于接收EEPROM的配置數據從外部串行EEPROM(如果有的話)。

EE_DOUT是通過一個內部電阻拉高

端口5使能:

ENABLE_MII5:輸入;

使能端口5MII模式,高電平時使能,低電平禁止,內部上拉電阻拉高;

端口5在MII模式工作:

P5_INCLK:通用I/O口:工作在MAC模式

輸入時鐘,這個時鐘是參考P5_INDV和P5_IND[3:0],P5_INCLK的方向與頻率在復位結束后由P5_MODE[3:0]確定; 如果該端口PHY模式,P5_INCLK輸出。在100BASE-X模式下的時鐘頻率為25 MHz, 如果該端口是在10BASE-T模式和50MHz RMII模式時鐘頻率2.5 MHz。

如果該端口的MAC模式,P5_INCLK是一個輸入。在這種模式下的時鐘頻率可以在任何地方從0Hz到25 MHz的,盡管它應該是為25 MHz100BASE-X模式下和2.5 MHz的10BASE-T模式。

P5_INCLK是在復位期間三態,它有一個內部電阻拉高。

P5_IND[3:0] 輸入;

輸入數據。P5_IND[3:0]接收的數據半字節被發送到交換機用來選擇100BASE-X和10BASE-T模式;

P5_IND[3:0]是同步的P5_INCLK。

這些引腳的輸入來自于端口的模式(即模式PHY或MAC模式)。

P5_IND0 SNI模式被選擇時使用。

P5_IND[1:0] RMII模式被選擇時使用。

P5_IND[3:0]內部上拉電阻高通過。

P5_INDV:輸入

輸入數據有效。

當P5_INDV被置為高電平,數據P5_IND[3:0]到交換機接受。P5_INDV必須是同步P5_INCLK SNI和MII模式,它必須是同步到P5_OUTCLK或P5_INCLK在RMII模式。

P5_INDV通過內部拉低電阻。

P5_OUTCLK:通用I/O

輸入時鐘,這個時鐘是參考P5_OUTDV和P5_IOUTD[3:0],P5_OUTCLK的方向與頻率在復位結束后由P5_MODE[3:0]確定;

如果該端口PHY模式,P5_OUTCLK輸出。在100BASE-X模式下的時鐘頻率為25 MHz,如果該端口是在10BASE-T模式和50MHz RMII模式時鐘頻率2.5 MHz。

如果該端口的MAC模式,P5_OUTCLK是一個輸入。在這種模式下的時鐘頻率可以在任何地方從0Hz到25 MHz的,盡管它應該是為25 MHz100BASE-X模式下和2.5 MHz的10BASE-T模式。

P5_OUTCLK是在復位期間三態,它有一個內部電阻拉高。

P5_OUTD[3:0]/P5_MODE[3:0]: 通常是輸出,僅僅在復位的時候是輸入;

輸出數據。和交換機傳輸的數據;

P5_OUTD[3:0]引腳同步到P5_OUT_CLK。

這些引腳是輸出端口的模式(即PHY或MAC模式)。

只有P5_OUTD0包含有意義的數據在SNI模式

P5_OUTD[1:0]選擇RMII模式1時。

在復位時,引腳的值被鎖定來確定工作模式,內部電阻拉高;

P5_OUTDV:輸出

輸出數據有效。

當P5_OUTDV被置為高電平,數據P5OUTD[3:0]到交換機接受。

P5_OUTDV必須是同步P5_INCLK 在MII模式,在RMII模式下應該同步與P5_INCLK或P5_OUTCLK在;

P5_INDV在復位時是三態模式,通過內部拉高電阻。

P5_CRS:通用I/O

載波偵聽。復位后,如果此端口PHY模式選擇,P5_CRS的成為輸出。

它仍然是輸入,如果MAC模式選擇。

P5_CRS將置1(或預期置1)當接收數據路徑的非空閑。

在半雙工模式的傳輸過程中P5_CRS也被置1(或預計置1)。

P5_CRS是異步到P5_OUTCLK和P5_INCLK的。

P5_CRS是在復位期間三態,它在內部被拉低,因此該引腳果不使用可以懸空

P5_COL:通用I/O

碰撞。復位后,P5_COL的PHY 模式變為輸出,如果在MAC模式選擇選擇此端口。它仍然是輸入;

在PHY模式,P5_COL的置1當發送和接收路徑是在兩個半和全雙工模式下非空閑; 在半雙工的MAC模式下,P5_COL的將置1非空閑時發送和接收路徑。

全雙工MAC模式下,P5_COL被忽略。

P5_COL是異步與P5_OUTCLK和P5_INCLK的。

P5_COL是在復位期間三態,它是內部拉低。

端口4使能:輸入;

DISABLE_MII4:

禁用端口4,高電平時使能PHY禁止MII,低電平時禁止PHY使能MII;

內部上拉電阻

交換機配置端口:

SW_MODE[1:0] 輸出;

開關模式。這些引腳用來復位后配置88E6060。切換模式引腳的工作方式如下:

0 0 CPU連接模式,端口來已禁用

0 1 保留

1 0 單機模式 - 忽略EEPROM

1 1 EEPROM連接的模式2

EEPROM的連接模式(SW_MODE[1:0] =[1,1])可以使用一個CPU。但在所有的獨立模式中,INTn腳發出低電平有效在EEPROM初始化內部寄存器完成后,(即停止命令已被執行);

SW_MODE[1:0]的上升沿不鎖存的復位和正確的設備操作必須保持靜態。他們是通過內部上拉電阻拉高。

FD_FLOW_DIS 輸入

全雙工流量控制禁用。

高=禁用所有全雙工端口的流量控制

低=啟用IEEE802.3x暫停的流量控制在所有支持全雙工端口

FD_FLOW_DIS到所有端口的PHY寄存器復位的上升沿被鎖存。它是通過一個電阻拉高。

EE_DIN/ HD_FLOW_DIS多功能引腳選擇半雙工端口的流量控制

端口狀態燈:

P[4:0]_LED2 輸出

每個端口并聯LED的輸出,低電平有效LED引腳直接驅動的LED在并聯LED模式。它 可以被配置為顯示多個選項。

P [4:0]_LED2低電平有效無論RESETN是否置1。

P[4:0]_LED1 輸出

每個端口并聯LED的輸出,低電平有效LED引腳直接驅動的LED在并聯LED模式。它 可以被配置為顯示多個選項。

P [4:0]_LED1低電平有效無論RESETN是否置1。

P[4:0]_LED0 輸出

每個端口并聯LED的輸出,低電平有效LED引腳直接驅動的LED在并聯LED模式。它 可以被配置為顯示多個選項。

P [4:0]_LED0低電平有效無論RESETN是否置1。

LEDSER:

LEDSER輸出串行狀態位被移入移位寄存器,可以通過LED顯示。LEDSER是的同步輸出LEDCLK。

LEDENA:

LEDENA置1不管LEDSER被存儲到移位寄存是否具有有效的狀態;LEDENA同步于LEDCLK;

LEDCLK:

LEDCLK是LED的串行信號的參考時鐘。

電子發燒友App

電子發燒友App

評論